Fan-out single die packaging structure, and preparation method thereof

A packaging structure, fan-out technology, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problem of high manufacturing cost of fan-out wafer-level packaging technology, to prevent position shifting, shorten Process time, effect of quality assurance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0071] like Figure 1 to Figure 11 As shown, this embodiment provides a method for preparing a fan-out single-die packaging structure, and the method includes:

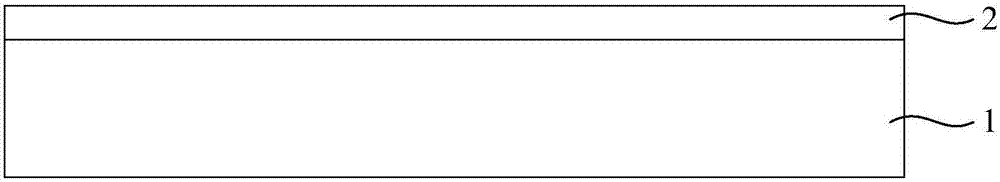

[0072] 1) Provide a carrier 1, and form an adhesive layer 2 on the upper surface of the carrier 1;

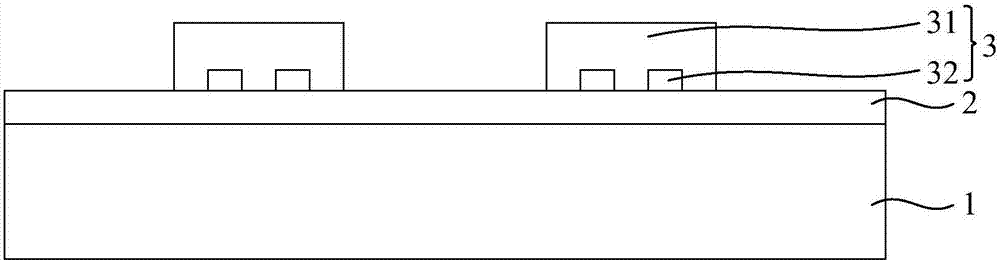

[0073] 2) forming a chip structure 3 on the upper surface of the adhesive layer 2, the chip structure 3 includes a bare chip 31 and a contact pad 32 located on the bare chip 31 and electrically connected to the bare chip 31;

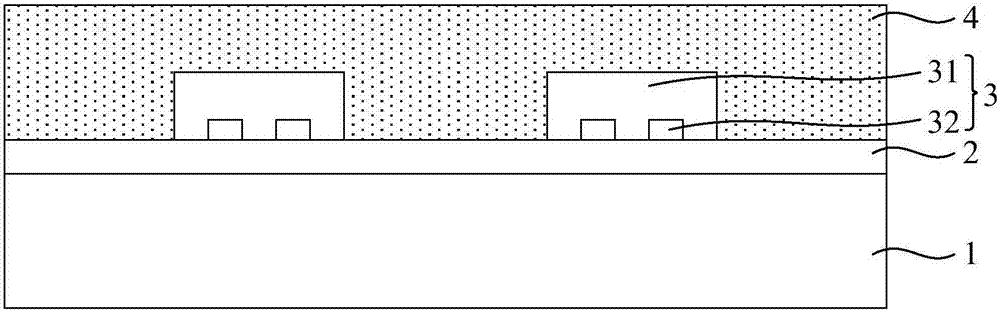

[0074] 3) forming a plastic sealing layer 4 on the upper surface of the adhesive layer 2, and the plastic sealing layer 4 covers the chip structure 3;

[0075] 4) removing the carrier 1 and the adhesive layer 2 to expose the chip structure 3;

[0076] 5) Form a first dielectric layer 5 on the surface of the plastic encapsulation layer 4 exposing the chip structure 3, and perform photoetching on the first dielectric layer 5 to form a first dielectric layer 5 exposing the contact pad 32. opening...

Embodiment 2

[0120] Such as Figure 11 As shown, this embodiment provides a fan-out single die packaging structure, the packaging structure includes:

[0121] A chip structure 3, the chip structure 3 comprising a bare chip 31 and a contact pad 32 located on the bare chip 31 and electrically connected to the bare chip 31;

[0122] enclosing the chip structure 3 while exposing the plastic encapsulation layer 4 on the surface where the contact pad 32 is located;

[0123] The first dielectric layer 5 located on the upper surface of the plastic encapsulation layer 4 and the chip structure 3, the first dielectric layer 5 exposes the contact pad 32 through the first opening 6;

[0124] A rewiring layer 7 located on the upper surface of the first dielectric layer 5 and the contact pad 32, the rewiring layer 7 exposes the first dielectric layer 5 through the second opening 8;

[0125] The second dielectric layer 9 located on the upper surface of the rewiring layer 7 and the first dielectric layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More