Manufacturing method of thin film transistor, thin film transistor and display substrate

A technology for thin film transistors and a manufacturing method, which is applied in the fields of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of affecting the electron mobility of thin-film transistors, unsatisfactory contact between amorphous silicon patterns and polysilicon patterns, etc. Mobility, performance improvement, effect of multi-touch area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the technical problems, technical solutions and advantages to be solved by the present invention clearer, the following will describe in detail with reference to the drawings and specific embodiments.

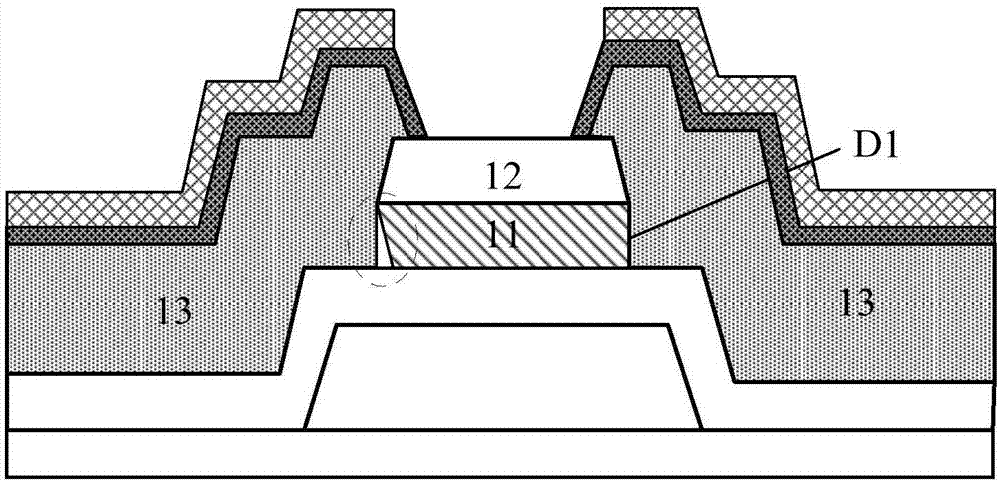

[0031] The invention provides a solution to the problem that the electron mobility of the thin film transistor is lowered due to the unsatisfactory contact between the amorphous silicon pattern and the polysilicon pattern in the active layer of the existing thin film transistor.

[0032] On the one hand, an embodiment of the present invention provides a method for manufacturing a thin film transistor, including a step of forming an active layer, the step including:

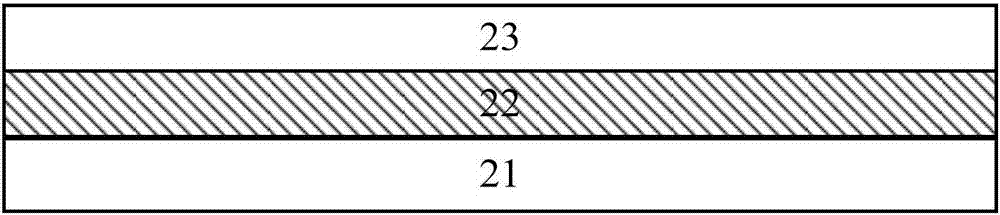

[0033] Step S1, refer to Figure 2A , sequentially forming a polysilicon layer 22 and a protective layer 23 on the base substrate 21;

[0034] Step S2, refer to Figure 2B , using the first etching gas to etch the protective layer 23 to obtain the protective pattern 23* formed by the prote...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com