High-speed parallel multi-path fractional delay filter implementation method

A technology of fractional delay and implementation method, applied in the field of communication, can solve problems such as low data rate, resource consumption, unrealistic, etc., and achieve the effect of simplifying the process of solving filter coefficients

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

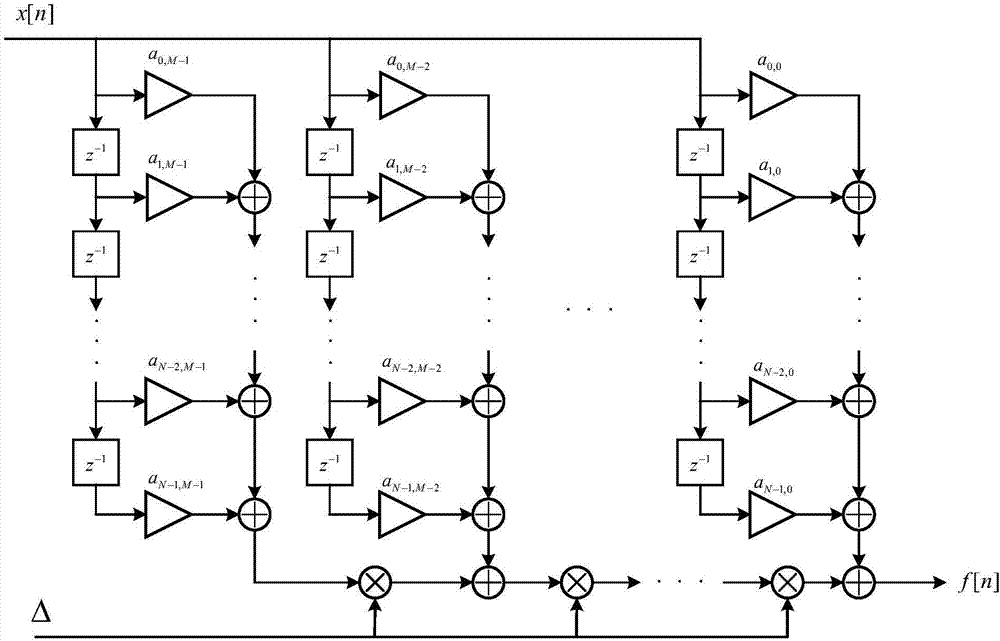

Method used

Image

Examples

Embodiment 1

[0059] In the present invention, the amount of delay compensation is 0.5T s , Performance simulation of applications under parallel 4-way conditions.

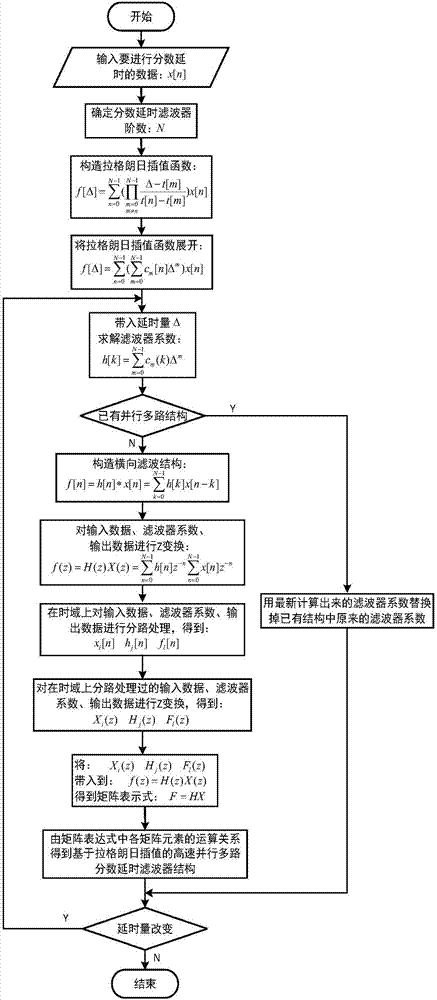

[0060] The implementation method and specific process of embodiment 1 are as attached image 3 shown.

[0061] Consider a single-frequency cosine signal with a frequency of f=100MHz, assuming that the ADC at the receiving end is 18 bits, and the sampling rate is f s =1GHz, sampling period T s =1ns, the number of sampling points is D=1000.

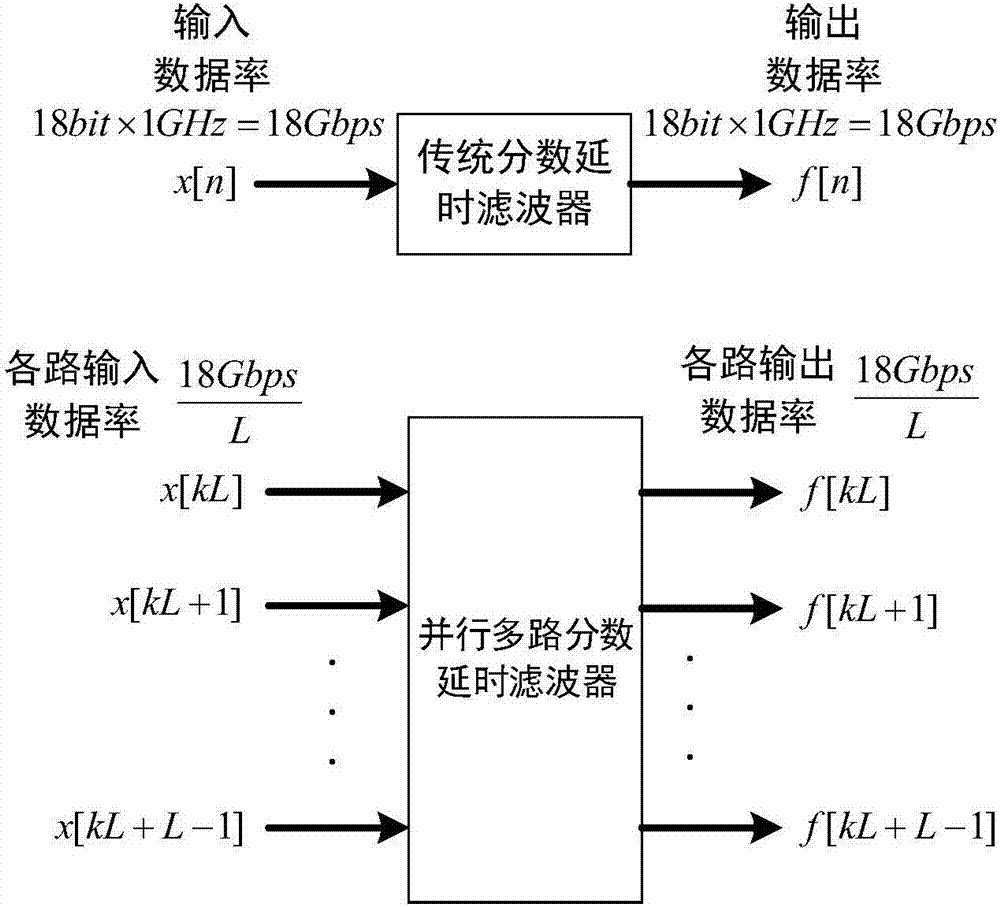

[0062] Because the data rate after sampling is very high (18bit×1GHz=18Gbps), if the traditional serial single-way fractional delay filter implementation method is used, the entire system is required to work at a clock frequency of 1GHz, which is unrealistic. It is difficult to realize in FPGA and DSP, so the traditional serial single-channel fractional delay filter implementation method cannot be applied. Therefore, we adopt the implementation scheme of the present invention to divide ...

Embodiment 2

[0103] The present invention has the performance of performing parallel 4-way fractional delay compensation on the target signal under the condition of different delay amounts.

[0104] The method of embodiment 2 is attached figure 2 As shown, the value of delay Δ is: Δ={0.1T s 0.2T s … 0.9T s}, and the rest of the simulation conditions are the same as those in Example 1. After changing the simulation conditions, perform the steps in Example 1, and record the rms corresponding to each value of the delay value Δ, and you can get the attached Figure 5 .

[0105] From attached Figure 5 It can be seen that the delay is 0.3T s The maximum delay compensation error is 2.4378×10 -4 , the delay is 0.9T s The minimum compensation error is 3.1523×10 -5 . Generally speaking, the present invention can complete parallel 4-way to the target signal, and the amount of delay is: Δ={0.1T s 0.2T s … 0.9T s}'s delay compensation and the compensation effect works very well.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More