Separable array-based reconfigurable accelerator and realization method thereof

An implementation method and accelerator technology, applied in physical implementation, neural learning methods, biological neural network models, etc., can solve problems such as waste of computing resources and bandwidth resources, low utilization of memory bandwidth, waste of resources, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0078] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

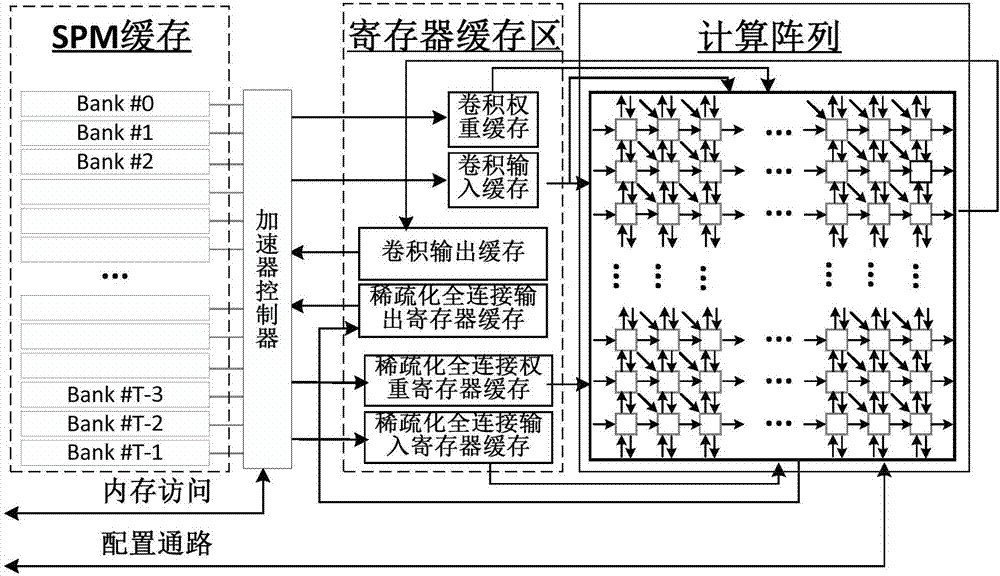

[0079] figure 1 It is a schematic structural diagram of a reconfigurable accelerator based on a divisible array according to an embodiment of the present invention, such as figure 1 As shown, the reconfigurable accelerator includes: a scratch-pad memory buffer (Scratch-Pad-Memory Buffer, SPM buffer or SPM buffer for short), a register buffer and a partitionable computing array (computing array). The register buffer area is connected to the computing array, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More