Universal double 2-vote-2 computer architecture and implementation method thereof

An implementation method and computer technology, applied in the direction of computers, digital computer components, calculations, etc., can solve the problems of large system security risks, low efficiency, non-failure reconfiguration, etc., and achieve the effect of improving maintainability and high fault coverage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

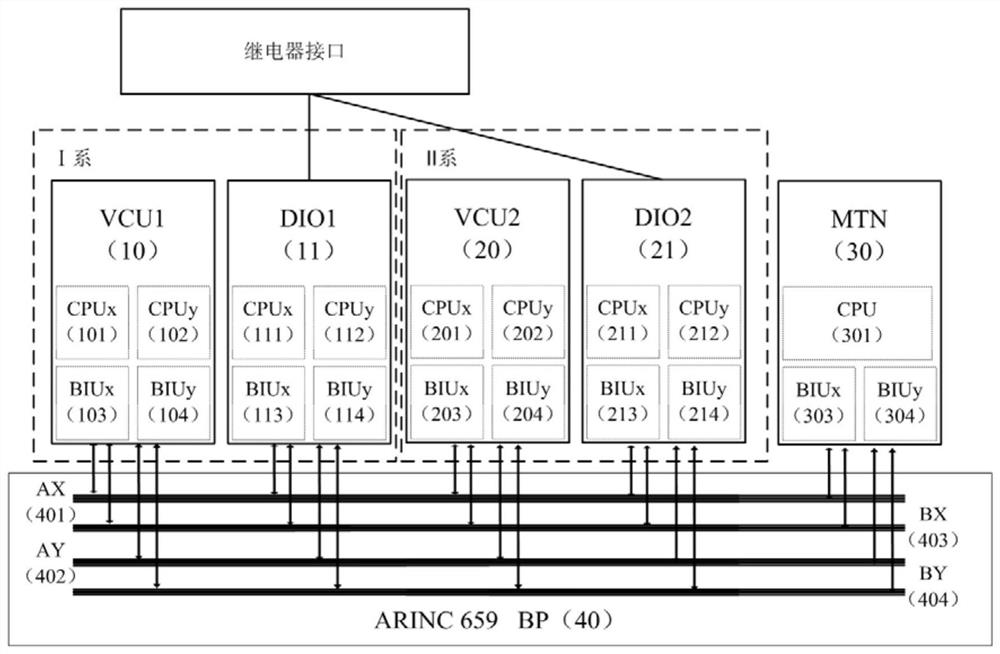

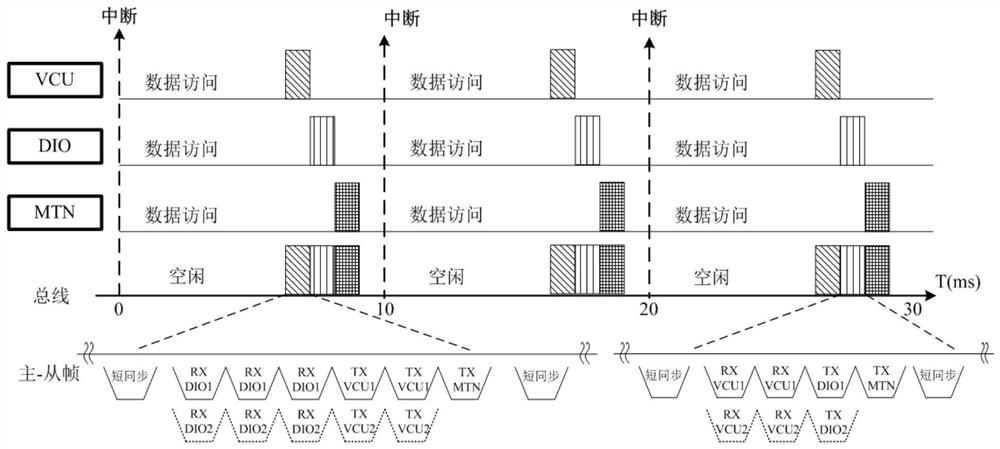

[0031] figure 1 It is a module composition diagram of a two-by-two architecture computer, combined with figure 1 As shown, this embodiment provides a general-purpose two-by-two computer architecture. The computer architecture includes a maintenance board MTN 30 and computer I series and computer II series with the same structure. The computer I series and computer II series pass The ARINC 659 bus is used for data connection with the maintenance board MTN30; the ARINC 659 bus is used for data exchange and data two-out-two comparison between computer series I and computer series II.

[0032] The maintenance board MTN 30 provides upgrade software programs to different CPU modules in the computer architecture, and records faults.

[0033] In this embodiment, the computer I series includes a self-monitoring processor board VCU1 10 and a self-monitoring input and output board DIO1 11; the self-monitoring processor board VCU1 10 is combined with control software to carry out compute...

Embodiment 2

[0044] This embodiment, in combination with the architecture of Embodiment 1, provides a method for implementing a general two-by-two computer architecture. The specific content is as follows:

[0045] In this embodiment, a two-by-two architecture computer is divided into completely identical and independent computer series I and computer series II, wherein the computer series I includes a self-monitoring processor board VCU1 10 and a self-monitoring input and output board DIO1 11 , the computer II system includes a self-monitoring processor board VCU2 20 and a self-monitoring input and output board DIO2 21 . Both VCU1 10 and VCU2 20 can simultaneously receive input information from the relay interface 50 of DIO1 11 and DIO2 21 .

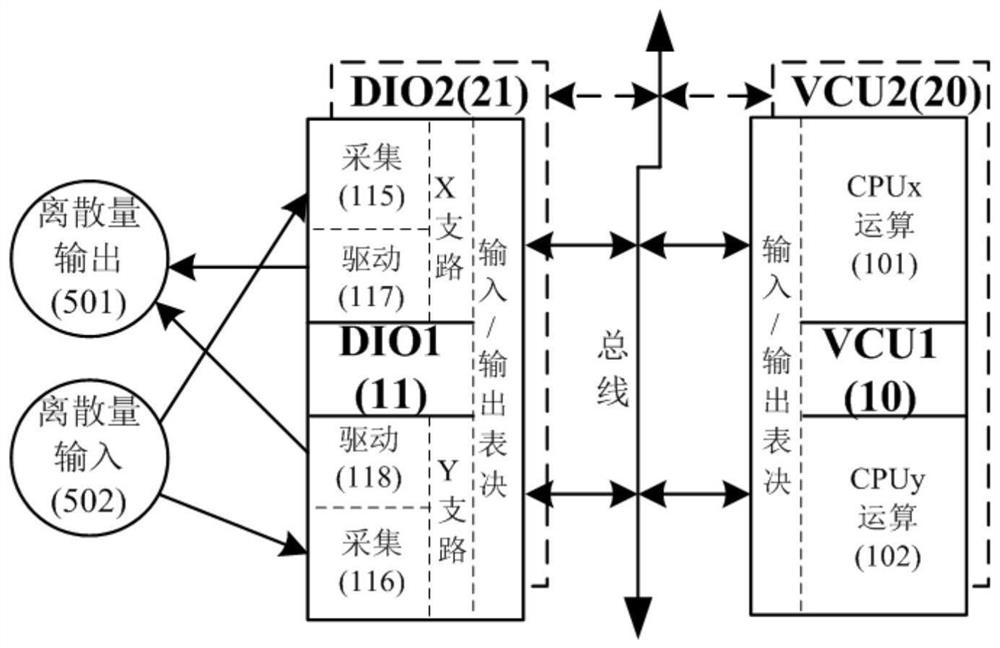

[0046] In the running mode, the self-monitoring input and output boards DIO1 11 and DIO2 21 collect the discrete signal of the relay interface 50 through an independent collection circuit under the action of the BIU synchronous clock.

[0047] As ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More