Front-end calibration method for assembly line ADC based on minimum quantization error

A technology of quantization error and calibration method, applied in the direction of analog/digital conversion calibration/test, electrical components, code conversion, etc., can solve the problems of high bandwidth and high gain operational amplifier, gain error, nonlinearity and other problems, and achieve improved calibration Low accuracy, reducing the effect of non-linearity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Below in conjunction with accompanying drawing and specific embodiment, describe technical solution of the present invention in detail:

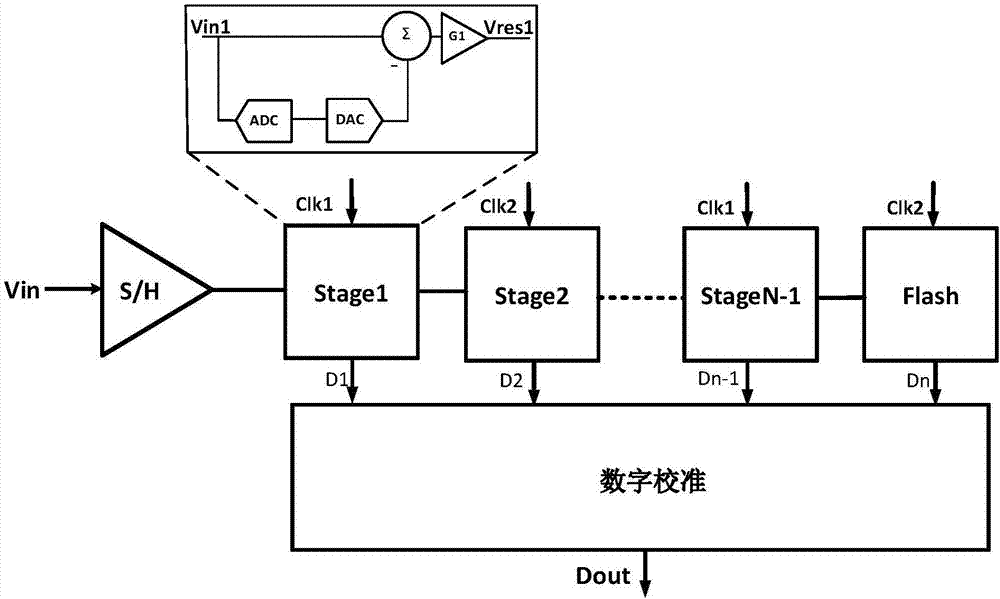

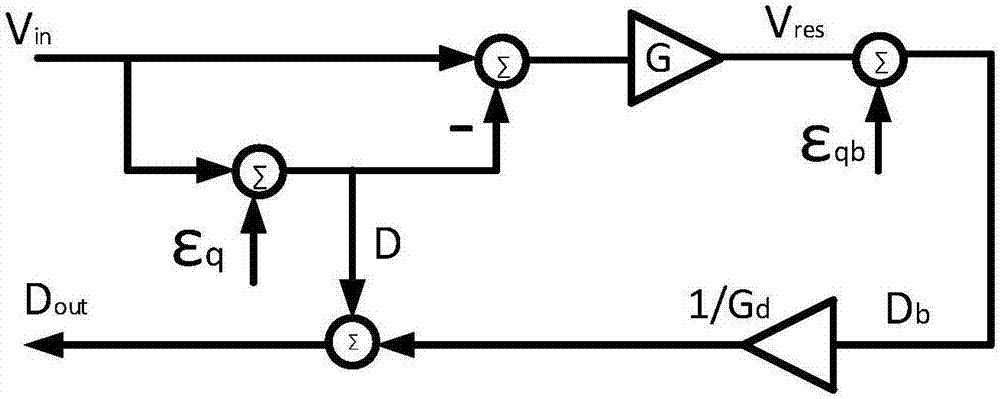

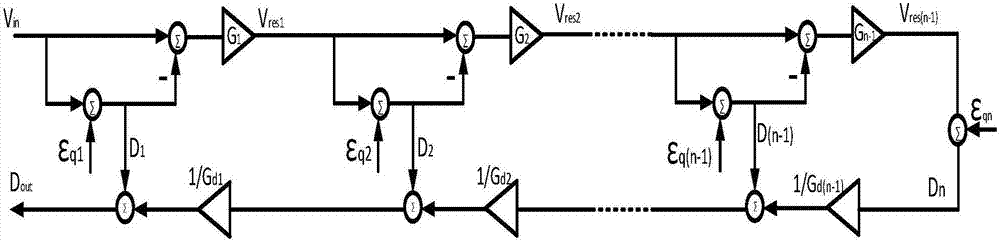

[0031] like figure 2 As shown, for an N-bit pipeline ADC, the signal flows into the first stage Stage1 through the sample-and-hold circuit, and the signal is sampled by the sub-ADC and MDAC at the same time during the sampling phase, and the signal is compared by the sub-ADC to generate a digital output Di; The middle DAC restores and makes a difference with the input signal, and then amplifies to generate a residual voltage V res . During this process, the sub-ADC quantizes the input signal to generate a quantization error ε q . Its input and output relationship is as follows:

[0032] D=V in +ε q (3)

[0033] V res =Gain*ε q (4)

[0034] in the attached figure 2 In addition to the first level, the total quantization error of other levels is determined by ε qb Indicates that, such as formula (5), when the calibration ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More