Patents

Literature

146 results about "Effective number of bits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

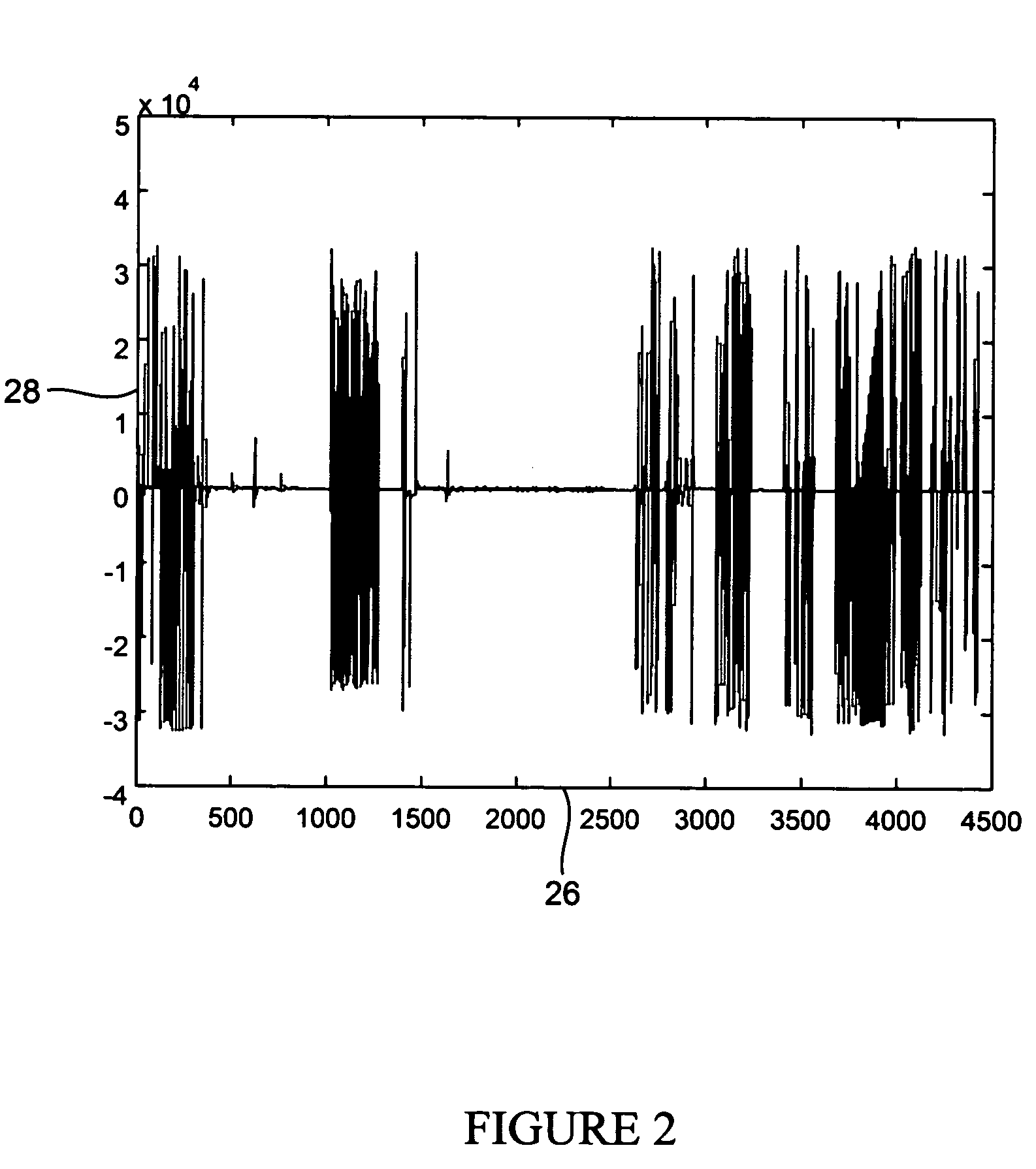

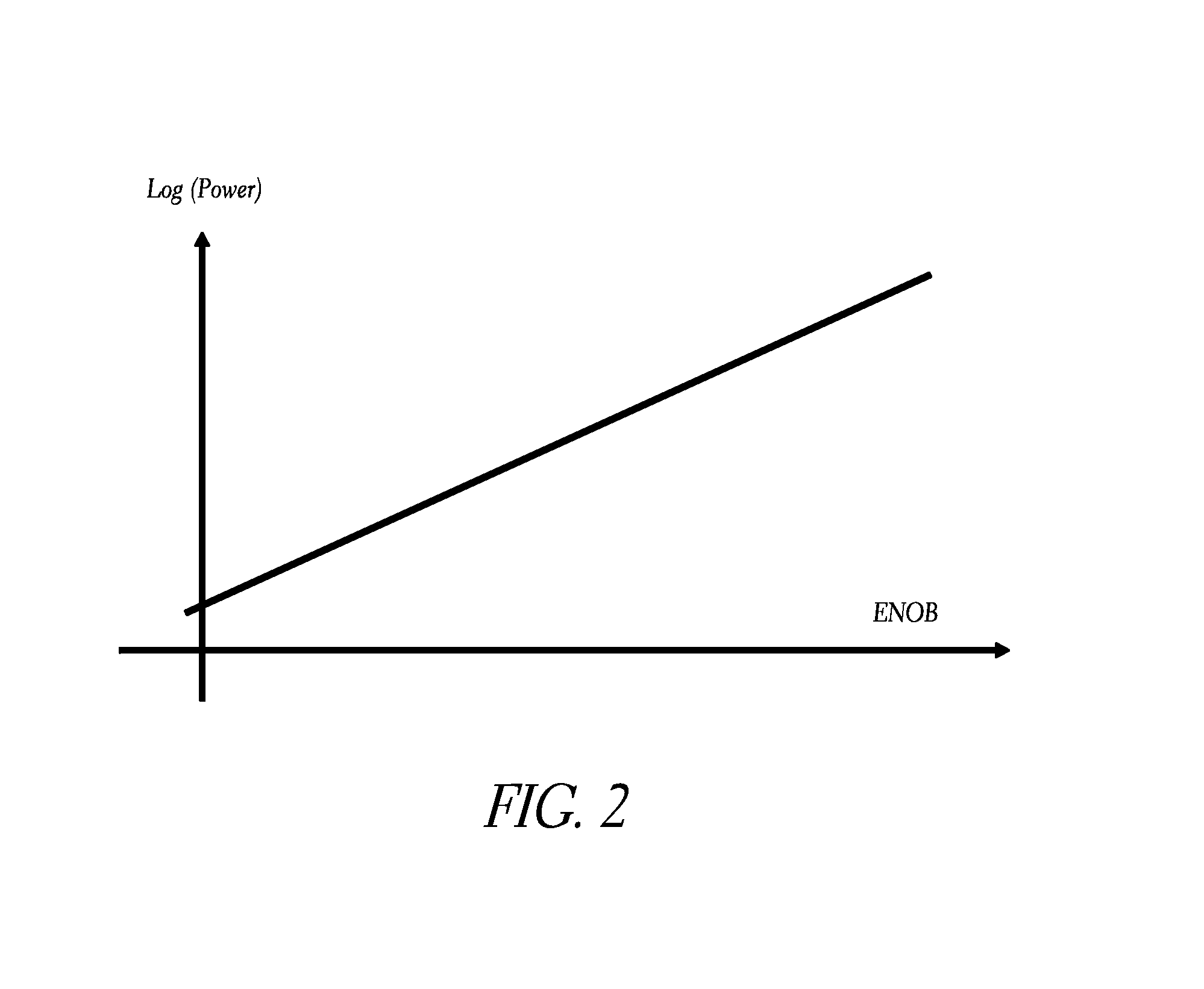

Effective number of bits (ENOB) is a measure of the dynamic range of an analog-to-digital converter (ADC), digital-to-analog converter, or their associated circuitry. The resolution of an ADC is specified by the number of bits used to represent the analog value. Ideally, a 12-bit ADC will have an effective number of bits of almost 12. However, real signals have noise, and real circuits are imperfect and introduce additional noise and distortion. Those imperfections reduce the number of bits of accuracy the ADC. The ENOB describes the effective resolution of the system in bits. An ADC may have 12-bit resolution, but the effective number of bits when used in a system may be 9.5.

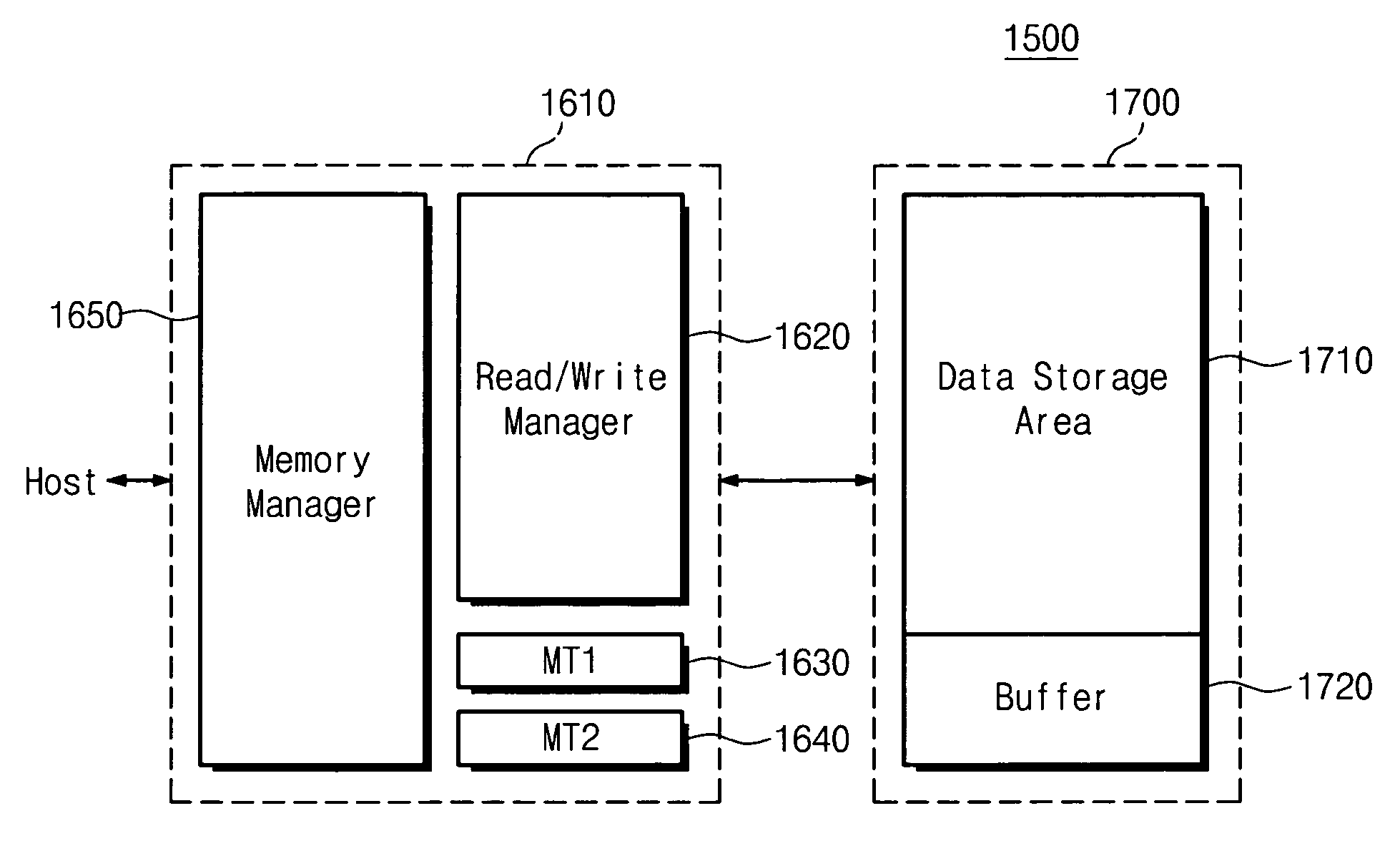

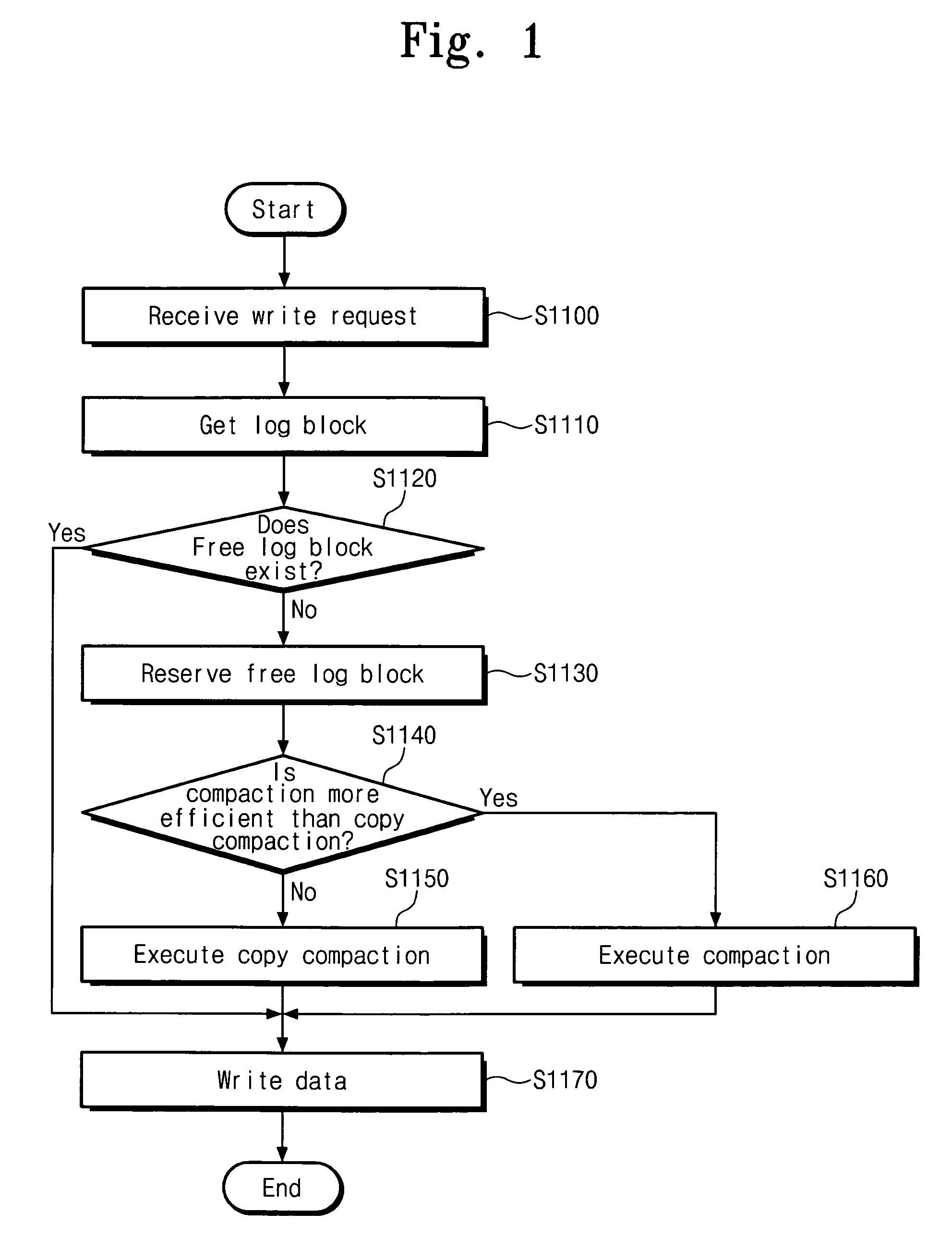

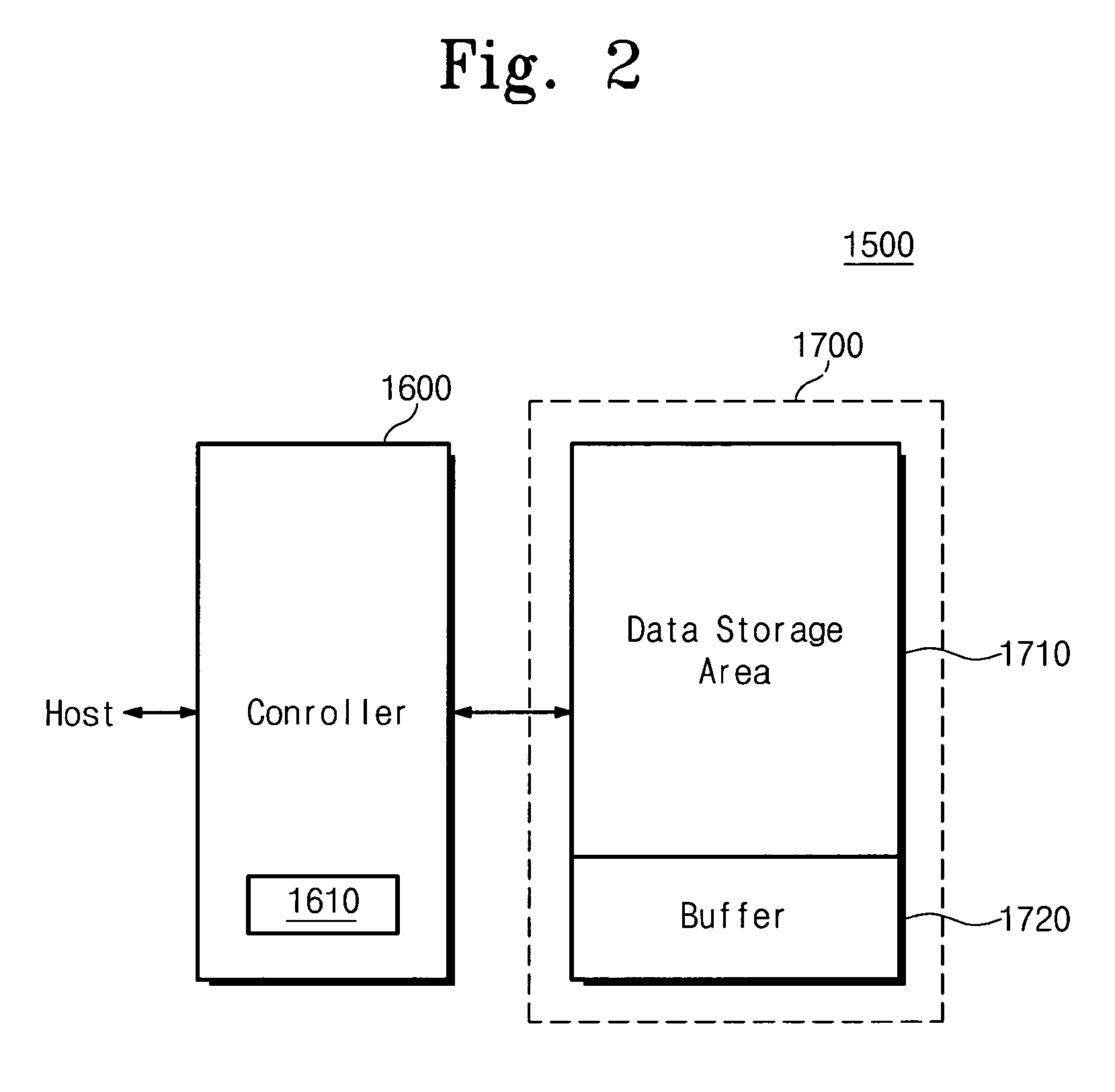

Memory system and method of accessing a semiconductor memory device

ActiveUS8027194B2Improve reliabilityMemory architecture accessing/allocationEnergy efficient ICTLeast significant bitMulti-level cell

One embodiment of a nonvolatile memory device includes a memory cell array including a plurality of multi-level cells, and a control unit configured to determine a characteristic of data to be stored in the memory cell array. The control unit is configured to select one of plural multi-bit programming methods based on the determination. Data is stored in the memory cell array according to the selected multi-bit programming method, and at least one of the plural multi-bit programming methods maintains least significant bit data when there is a program fail of most significant bit data.

Owner:SAMSUNG ELECTRONICS CO LTD

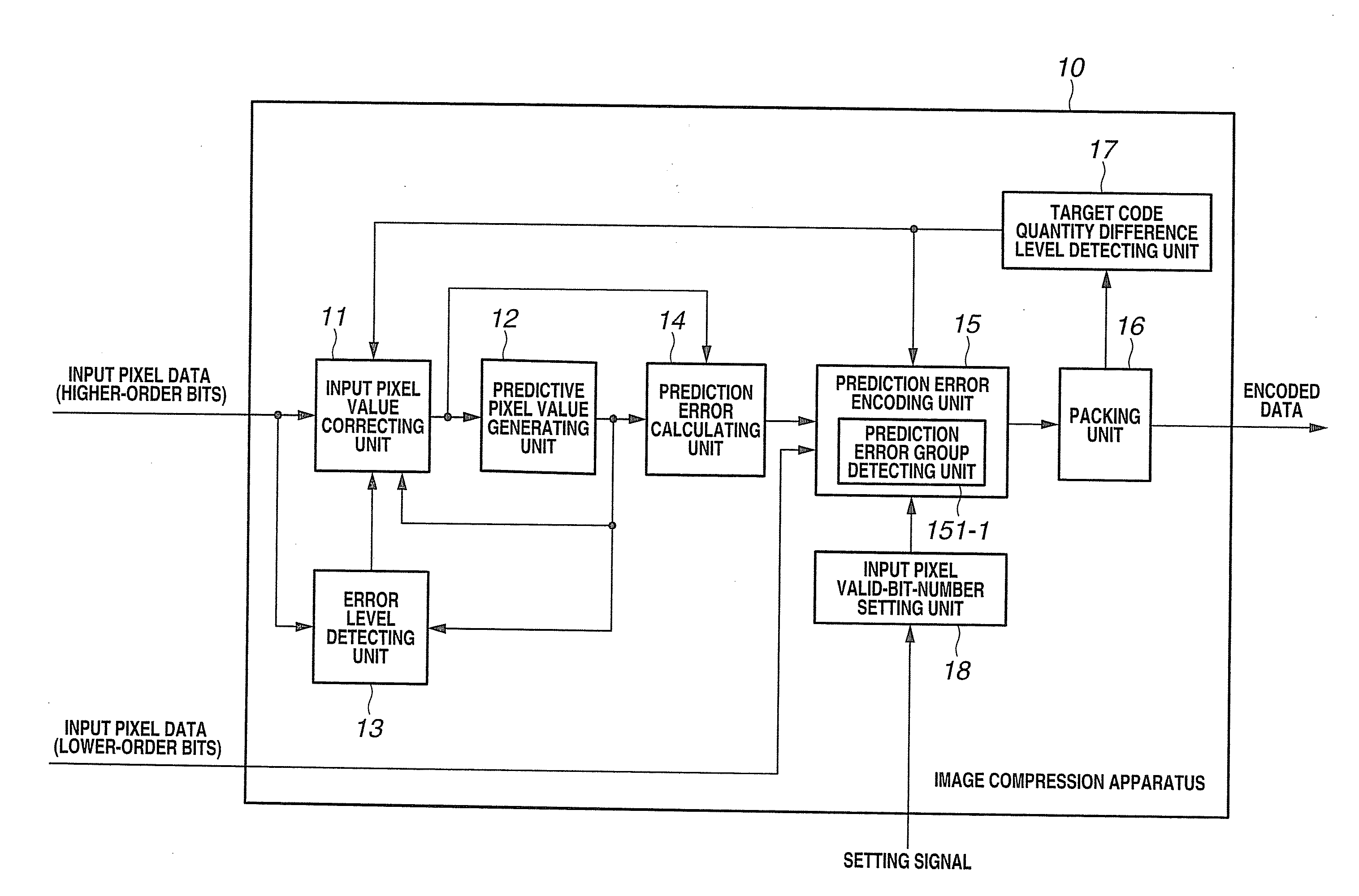

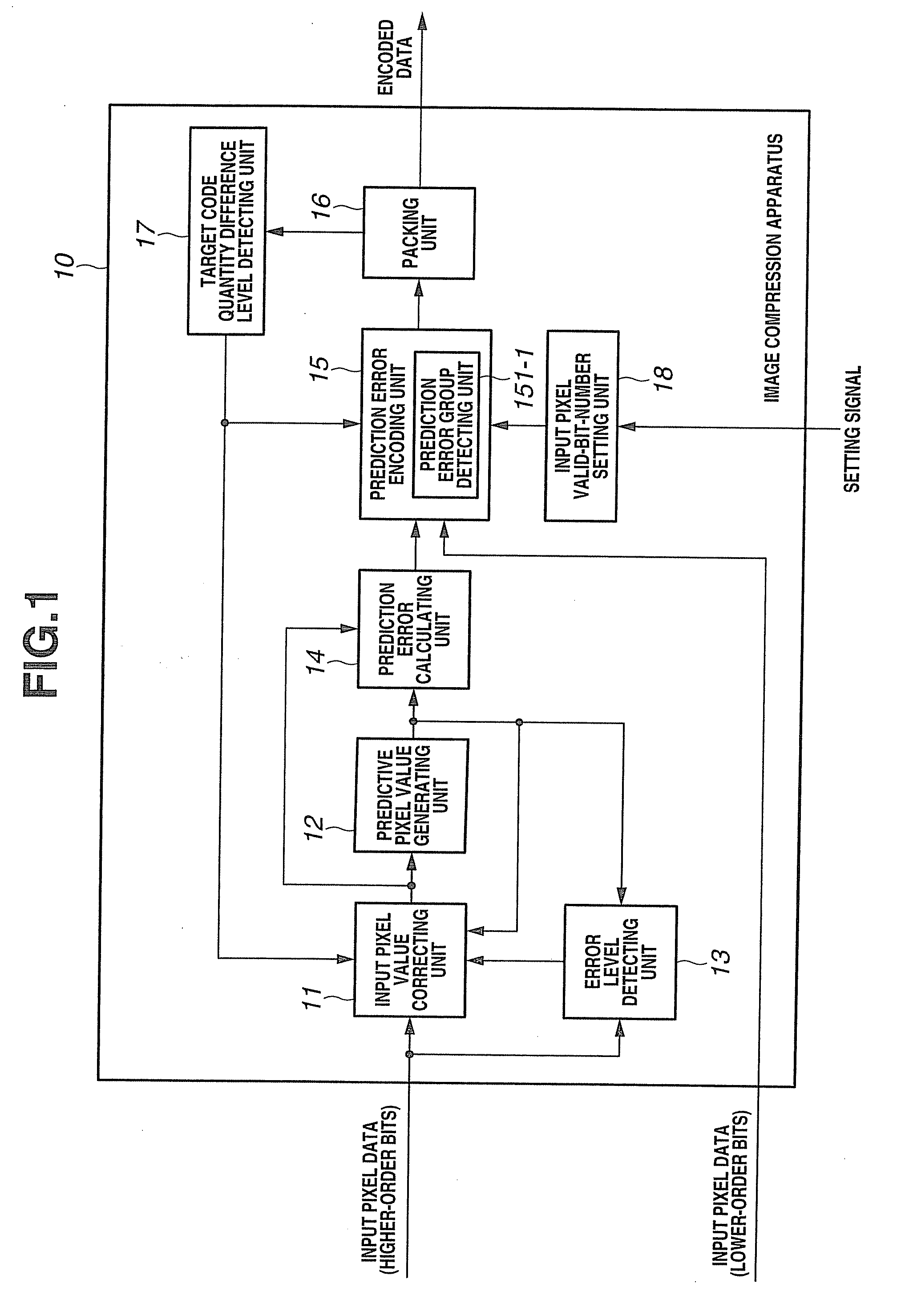

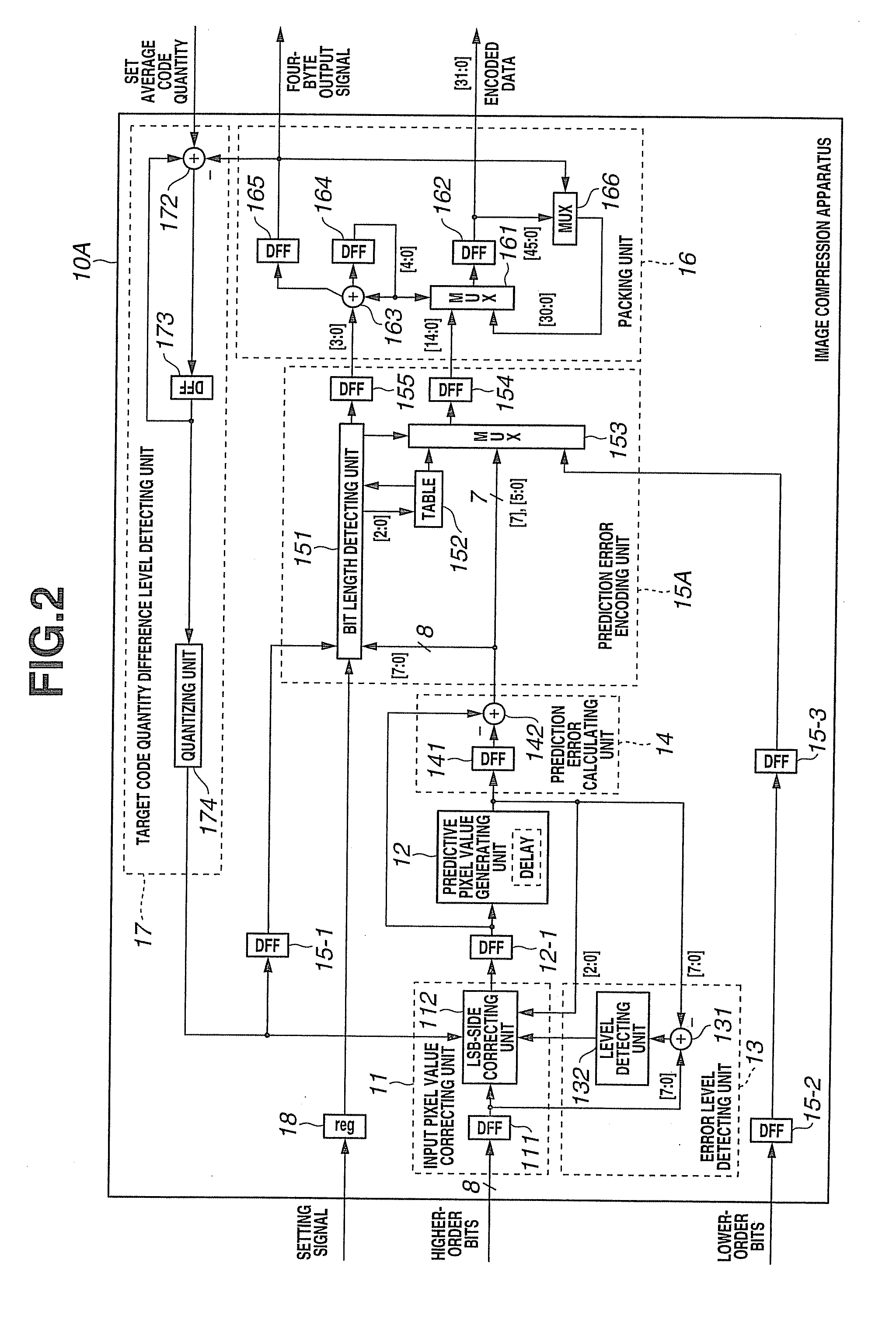

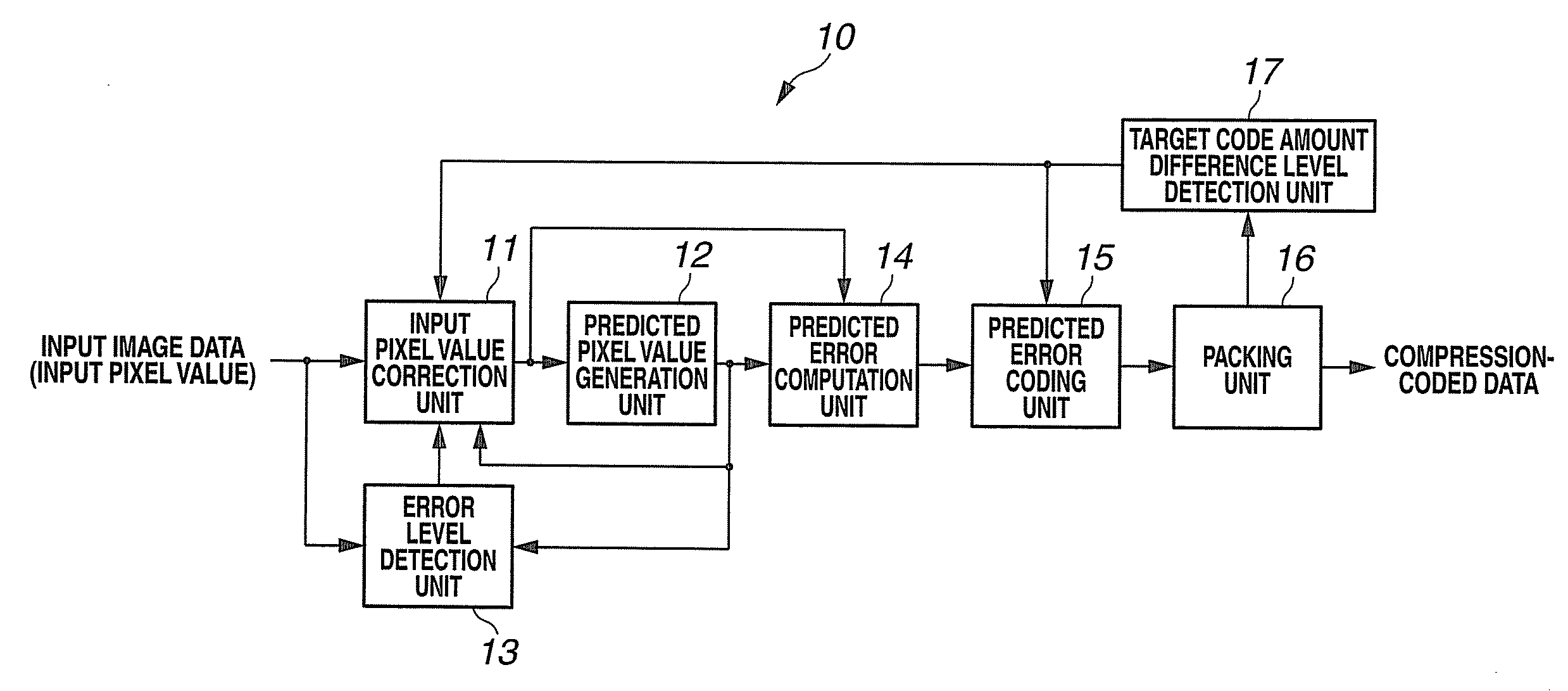

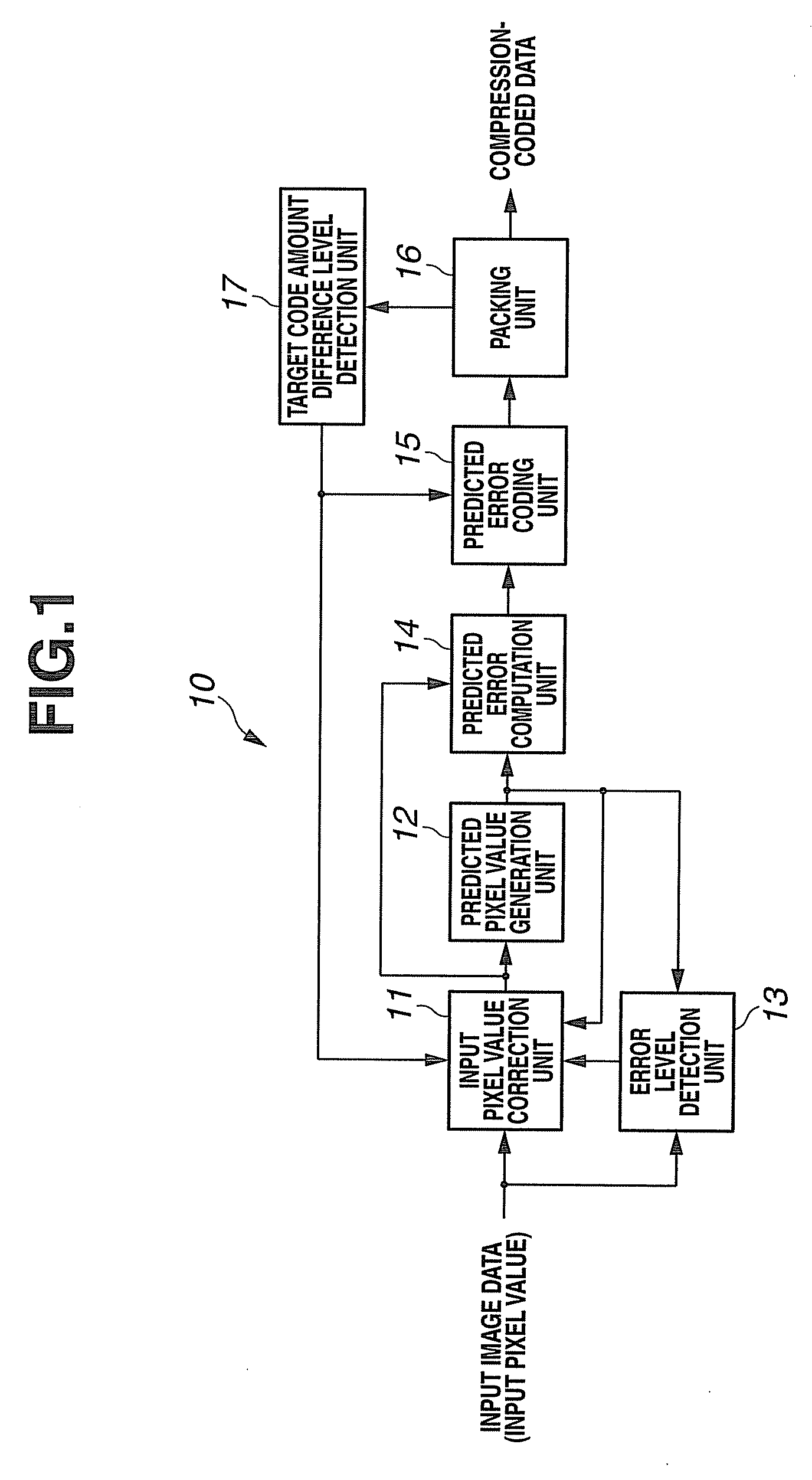

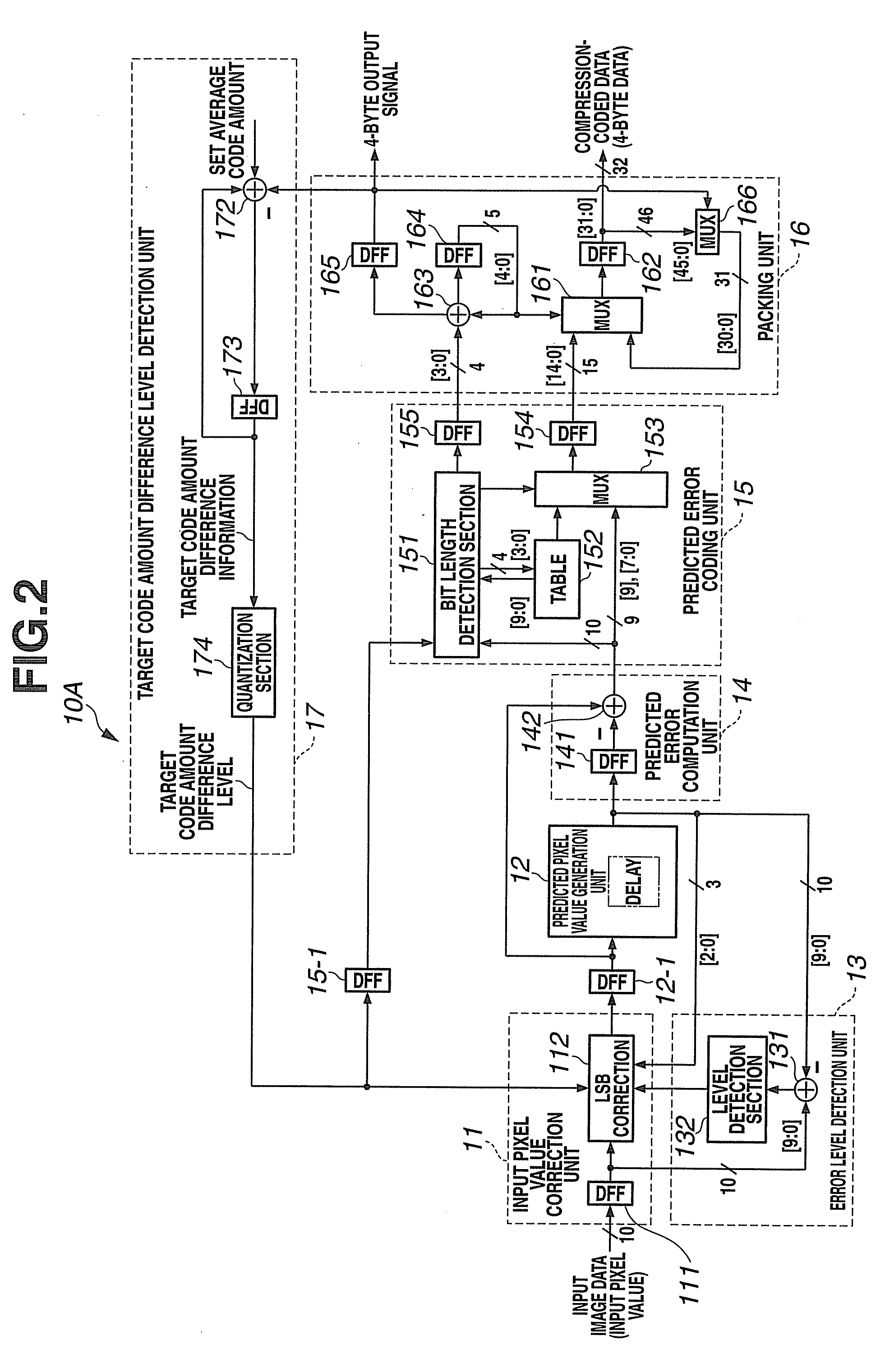

Image compression apparatus, image expansion apparatus, and image processing apparatus

InactiveUS20090279800A1Character and pattern recognitionDigital video signal modificationMultiplexingImaging processing

An input pixel valid-bit-number setting unit sets an input pixel valid-bit-number which is the number of gradations of input pixel data. A predictive pixel value generating unit refers to the higher-order bits of earlier already-input pixel data to generate a predictive pixel value for the higher-order bits of a new input pixel. A prediction error group detecting unit detects a prediction error group indicative of the magnitude range of a difference between the predictive pixel value and the value of the higher-order bits of the new input pixel. A prediction error encoding unit multiplexes variable-length encoded information indicative of the prediction error group, overhead bits indicative of a specific value within the prediction error group, and the lower-order bits of the input pixel appropriate for the input pixel valid-bit-number.

Owner:KK TOSHIBA

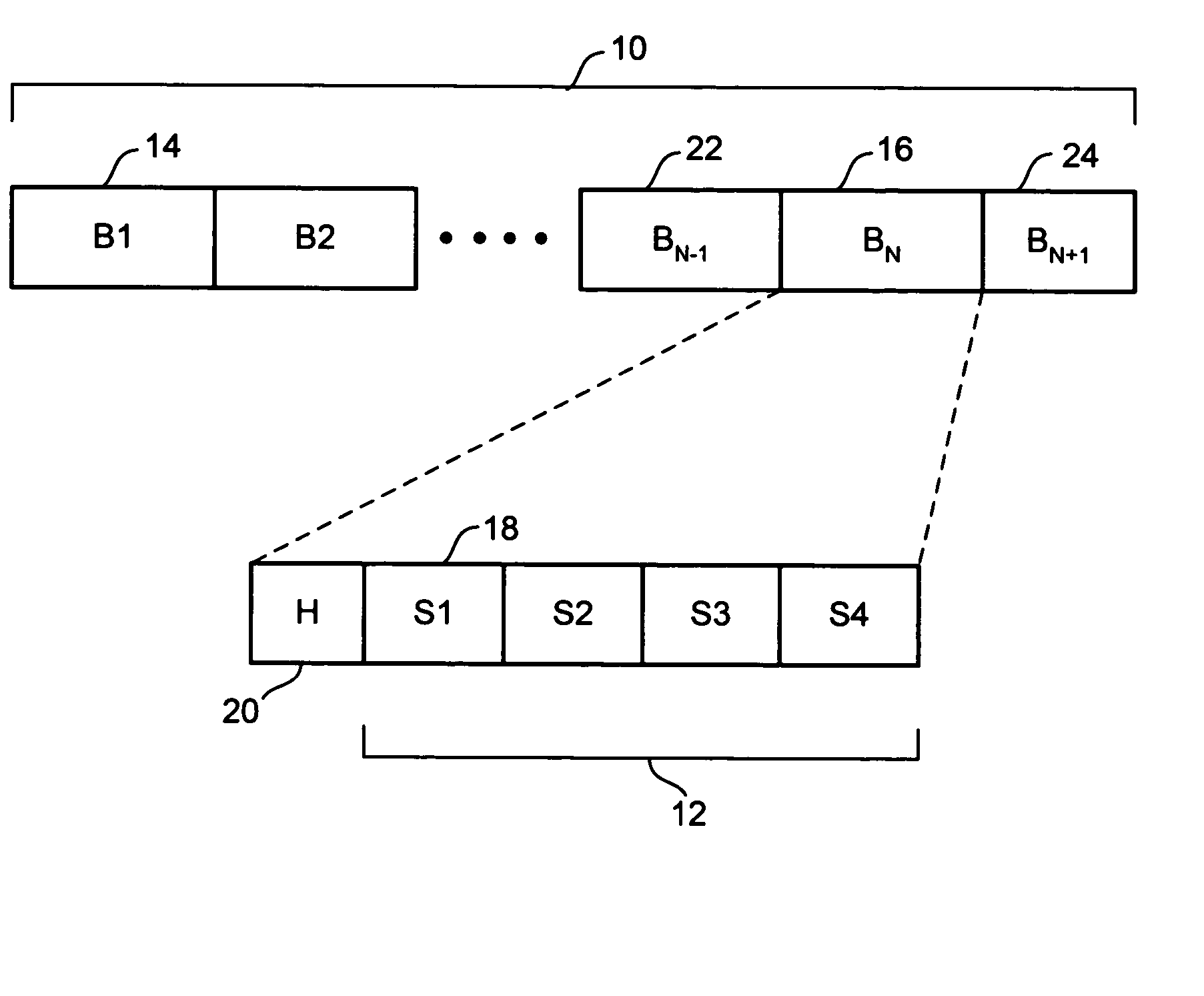

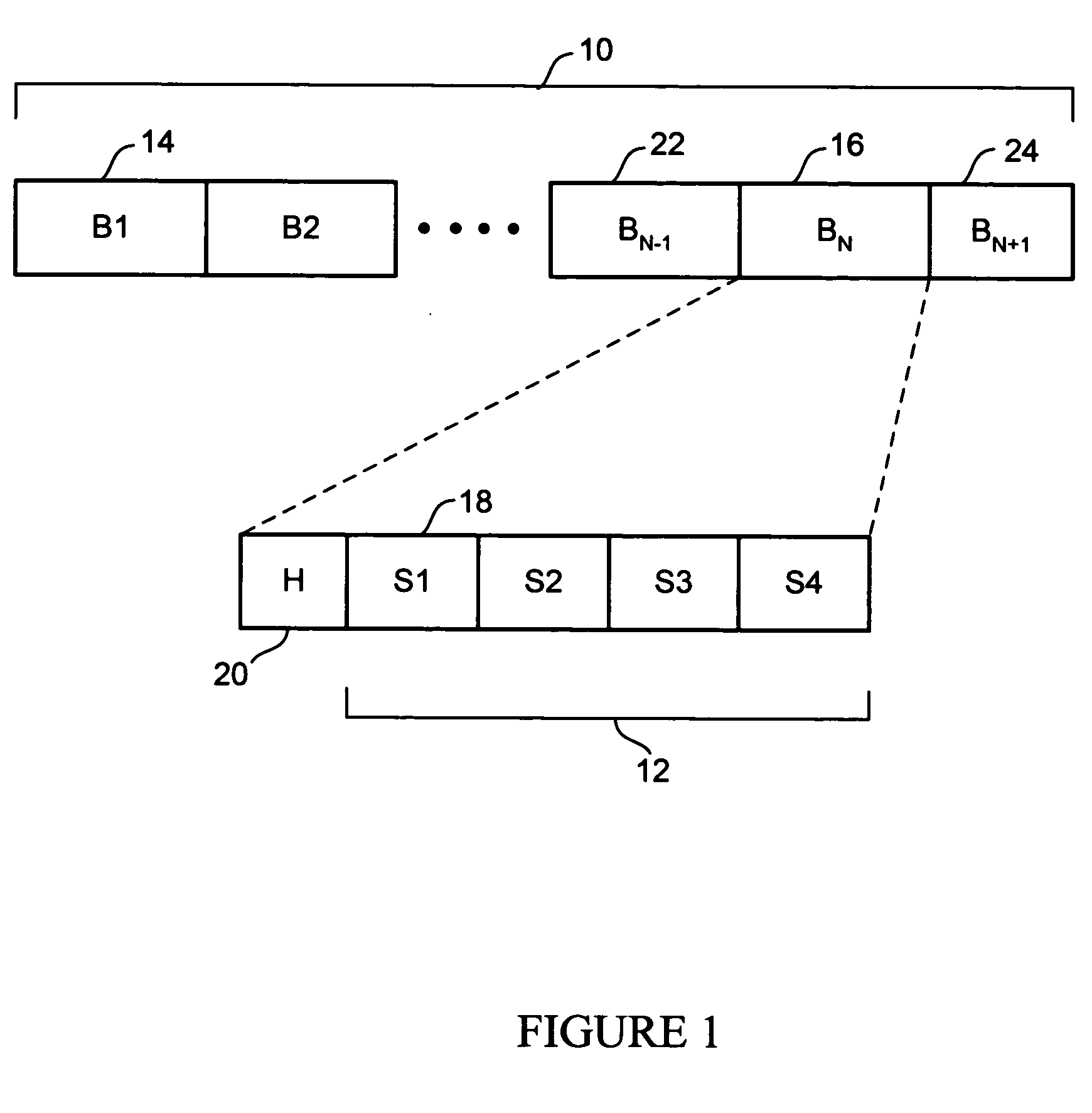

Reducing context memory requirements in a multi-tasking system

InactiveUS20050240380A1Reduce memory requirementsReduce context memory requirementCode conversionSpecial data processing applicationsLossless compression algorithmPrefix header

A process for reducing the context memory requirements in a processing system is provided by a generic, lossless, compression algorithm applied to multiple tasks or multiple instances running on any type of processor. The process includes dividing data in a task of a multi-tasking system into blocks with each block containing the same number of words. For the data in each task, a word in a block having a maximum number of significant bits is determined, a packing width to the block of said maximum number of significant bits is assigned, and the least significant bits of each word in the block into a packed block of the packing width multiplied by a total number of words in the block is encoded with a lossless compression algorithm. A prefix header at the beginning of each packed block to represent a change in the packing width from the packed block from a packing width of a previous packed block is also provided.

Owner:TELOGY NETWORKS

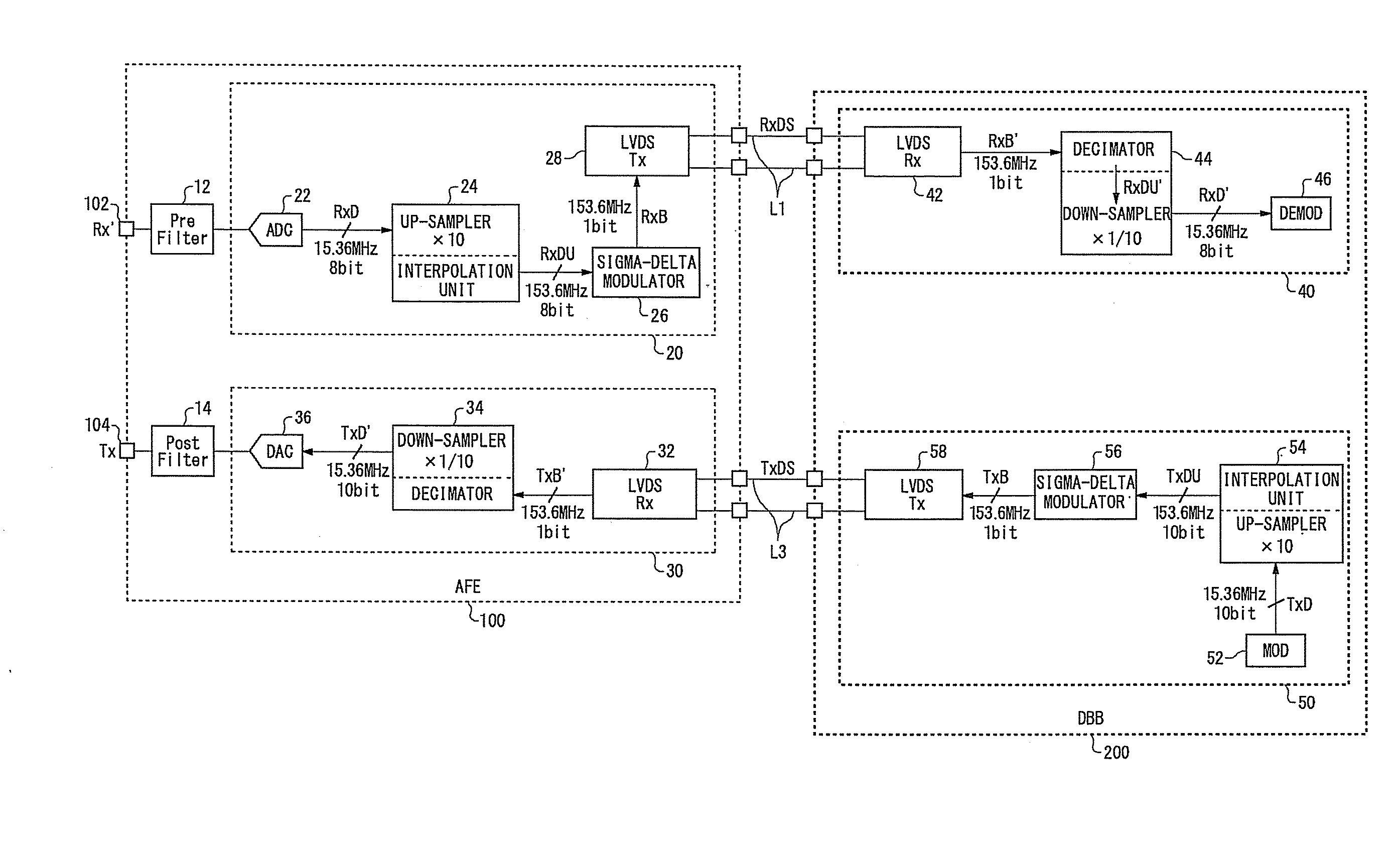

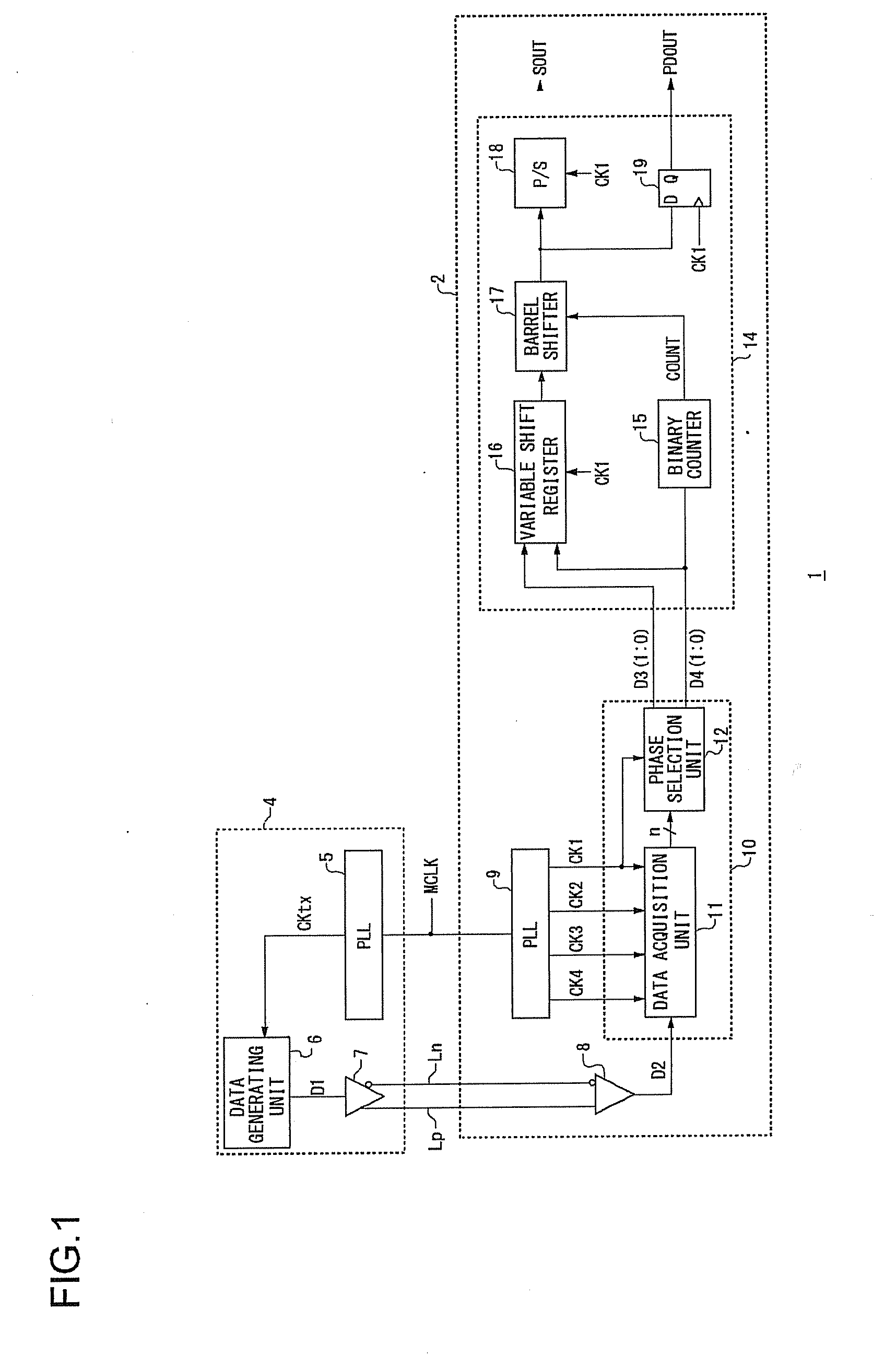

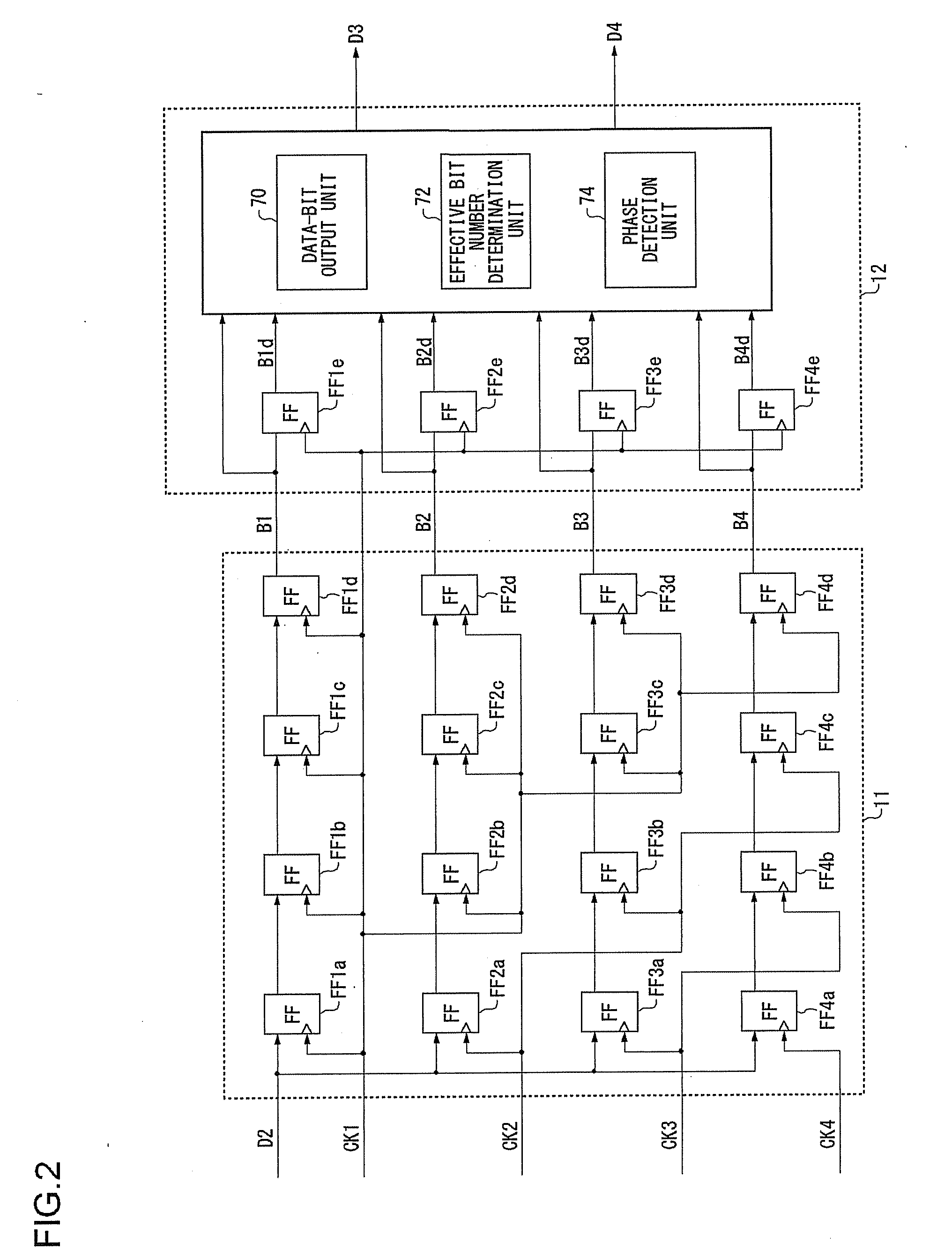

Receiver circuit and receiving method

InactiveUS20080159444A1Parallel/series conversionPulse automatic controlPhase shiftedTransition edge

Clock signals are supplied, with a phase shift of 1 / n cycles between adjacent clock signals. A data acquisition unit acquires serial data at a timing of each of the clock signals. A phase detection unit detects the phase of the transition edge of the serial data using n bits of data. An effective bit number determination unit determines the effective bit number, which is the number of bits to be acquired, based upon the phase of the transition edge of the serial data in the current data-bit acquisition step and the phase of the transition edge of the serial data in the previous data-bit acquisition step. A data-bit output unit outputs the effective bit number of the bits of data acquired at a timing of each clock signal having a predetermined phase relation with the transition edge of the serial data.

Owner:ROHM CO LTD

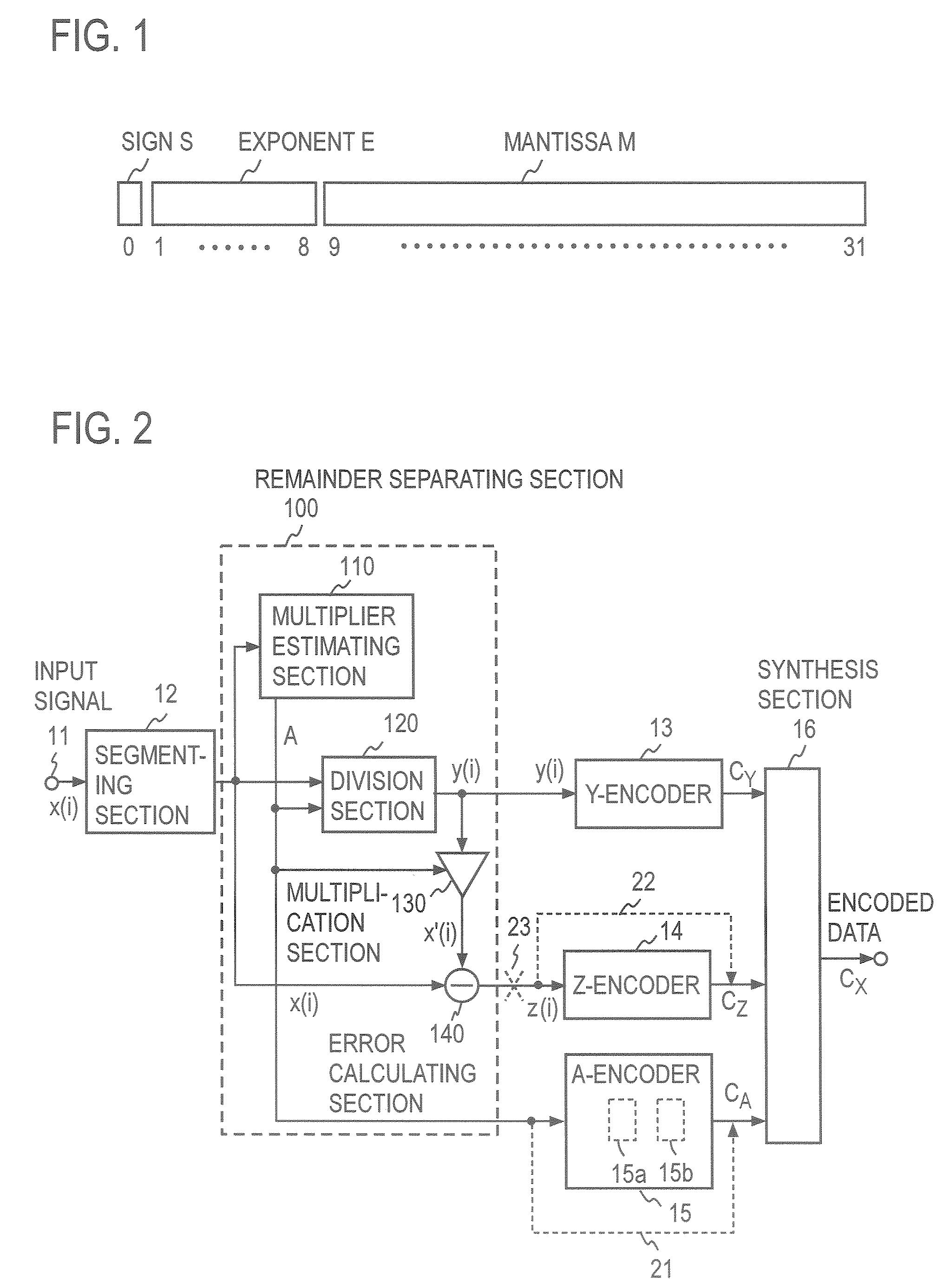

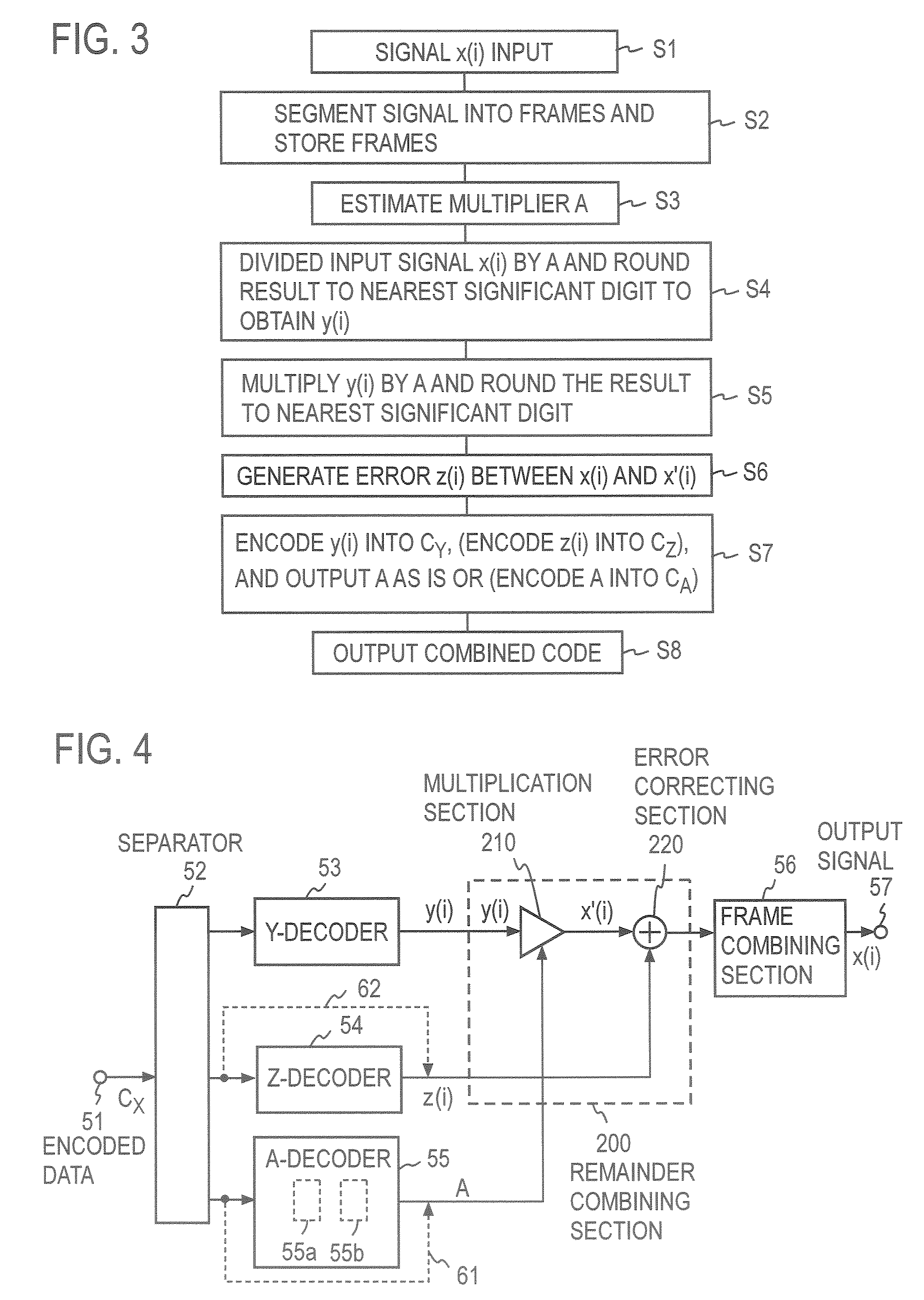

Information Encoding Method, Decoding Method, Common Multiplier Estimating Method, and Apparatus, Program, and Recording Medium Using These Methods

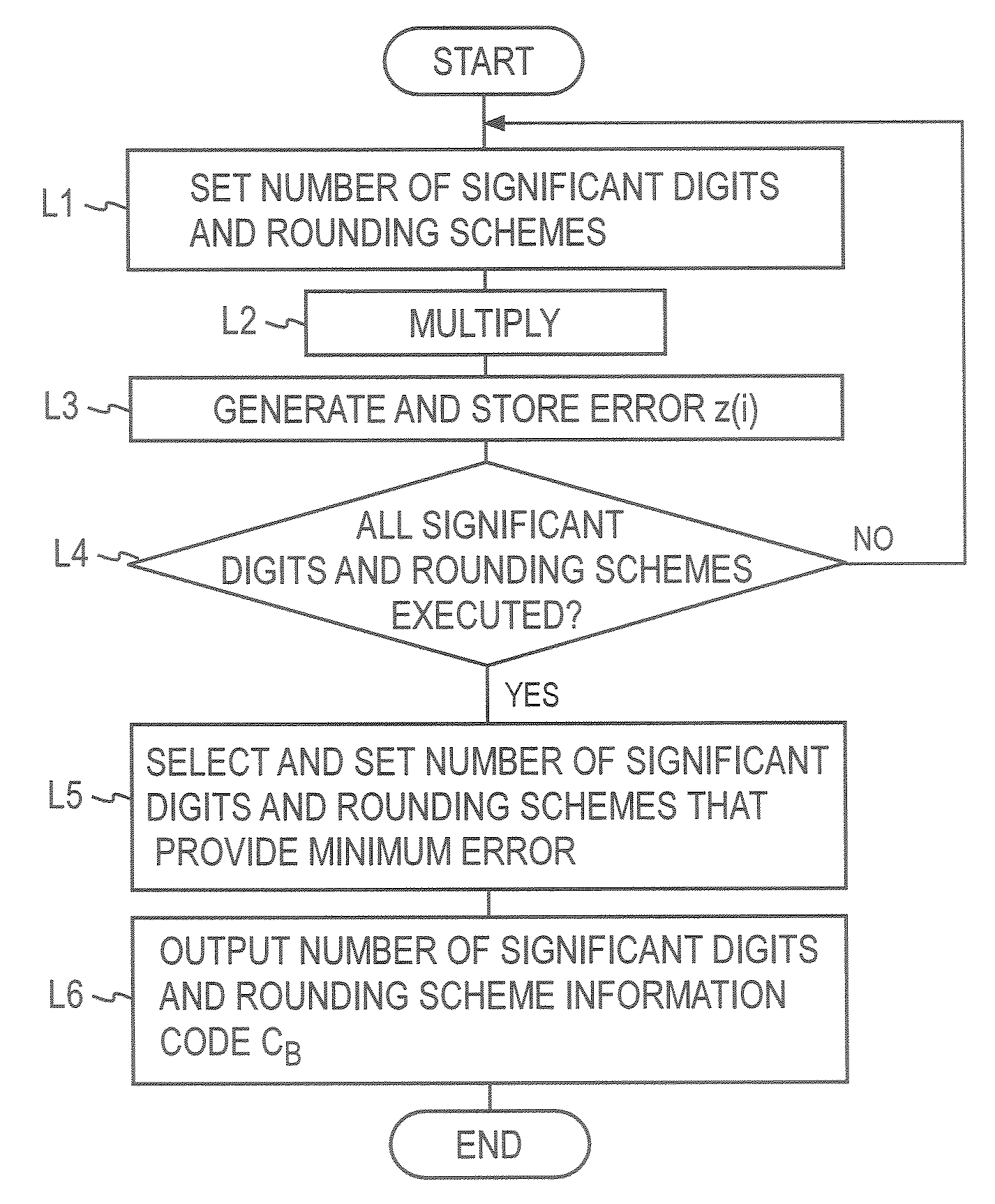

ActiveUS20070257824A1Avoid quality lossSmall increase in amount of informationElectric signal transmission systemsSpeech analysisDecoding methodsNegative error

An object of the present invention is to provide a method for encoding signals by separating a signal by using a common multiplier so as to improve the efficiency of compression of audio signals and a method for calculating a common multiplier of a set of numeric values including errors. A common multiplier A, of the input signal samples x(i) in each frame is estimated. Each sample x(i) is divided by A, the quotient is rounded to the number of significant digits, and the rounded quotient y(i) is encoded. The quotient y(i) is multiplied by A and the product is subtracted from x(i) to obtain an error signal z(i), which is then encoded. The multiplier A is encoded and the code of y(i), the code of z(i), and the code of A are combined together and outputted. To estimate the common multiplier, each numeric value is divided by a determined representative value. Irreducible fractions between the maximum positive error and the maximum negative error are obtained by dividing each numeric value by a correct representative value using rational approximation. Among the obtained irreducible fractions, the one having the smallest common denominator of the numeric values is obtained and the common denominator is corrected using the representative value to obtain a common multiplier.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP

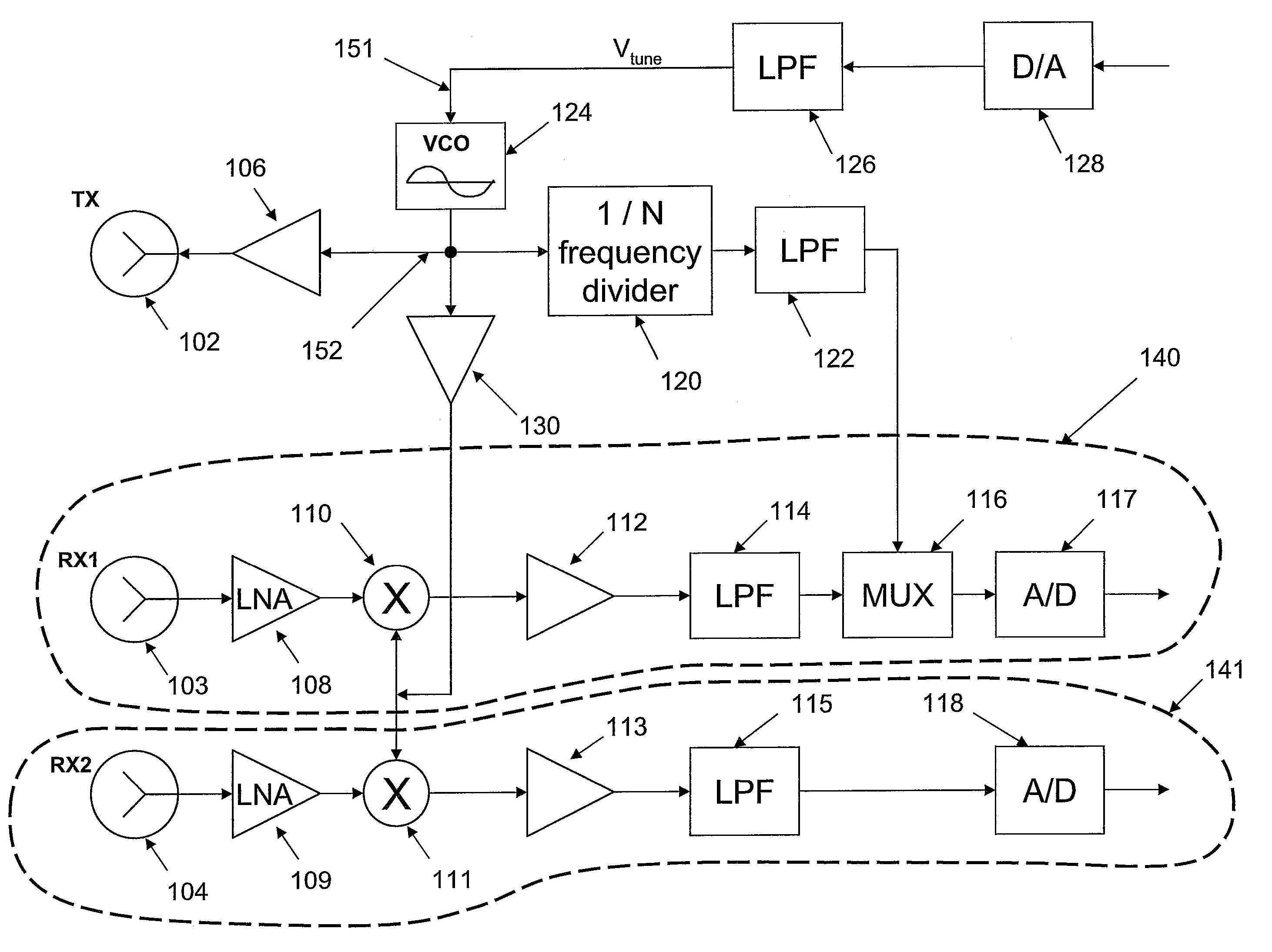

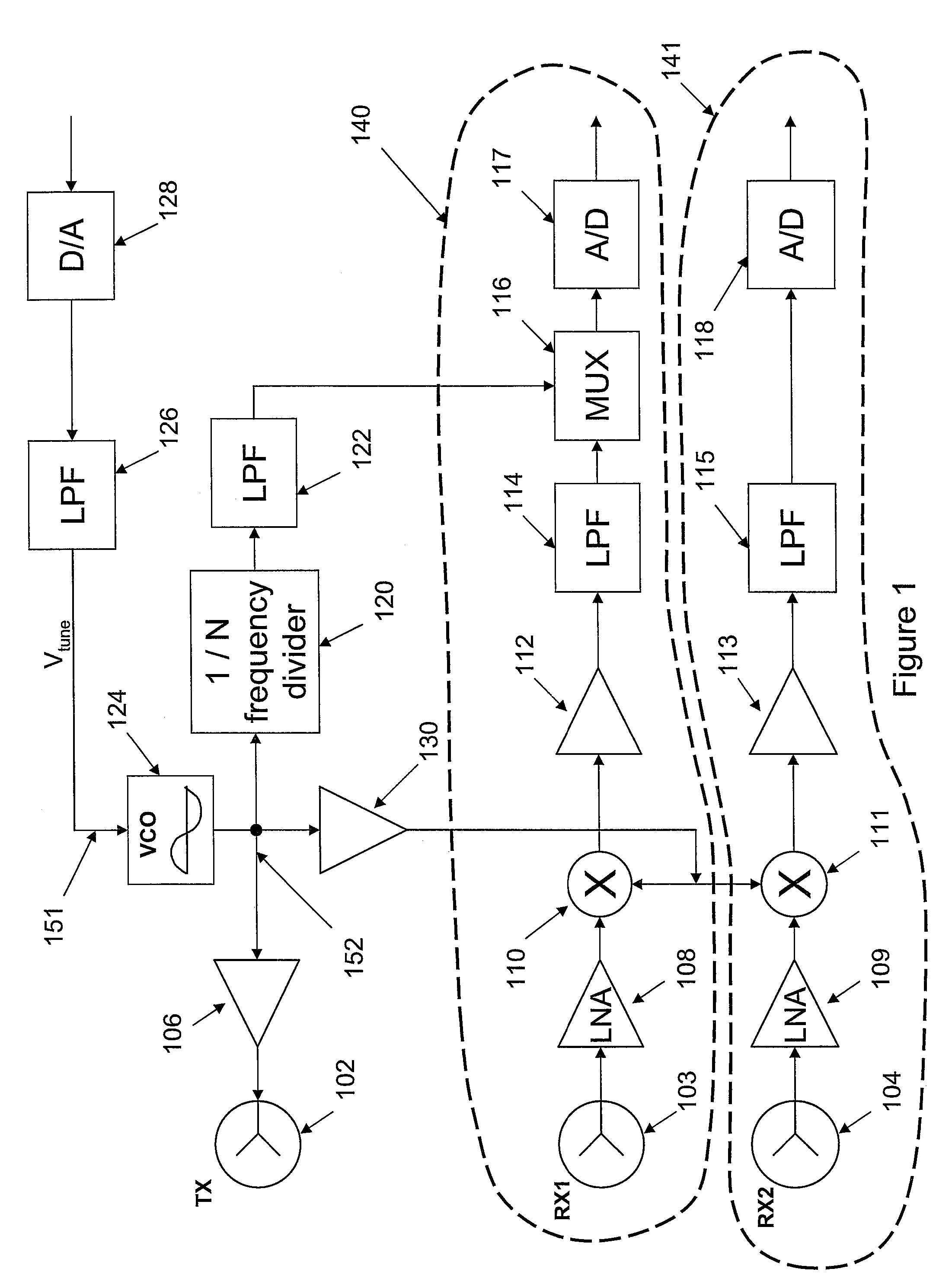

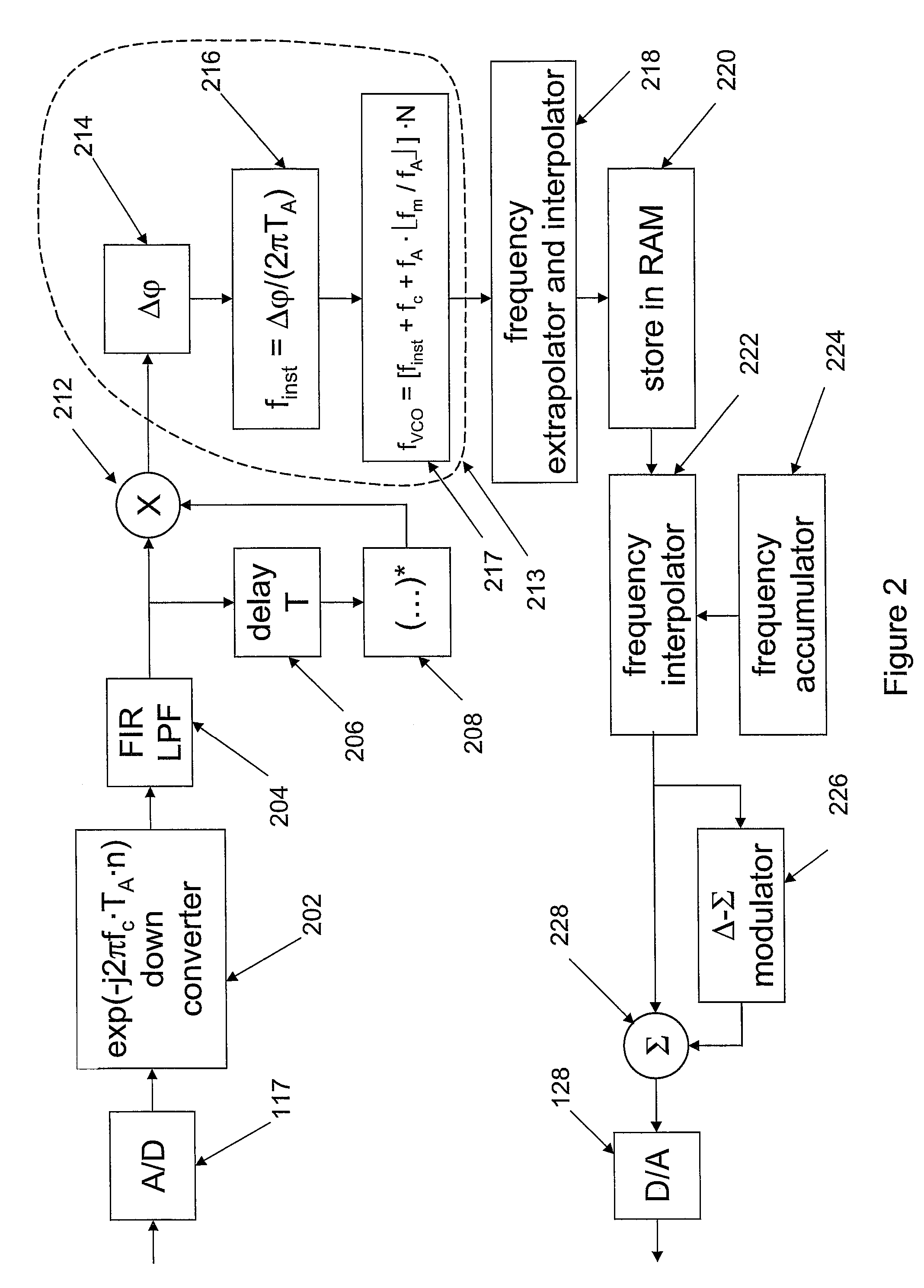

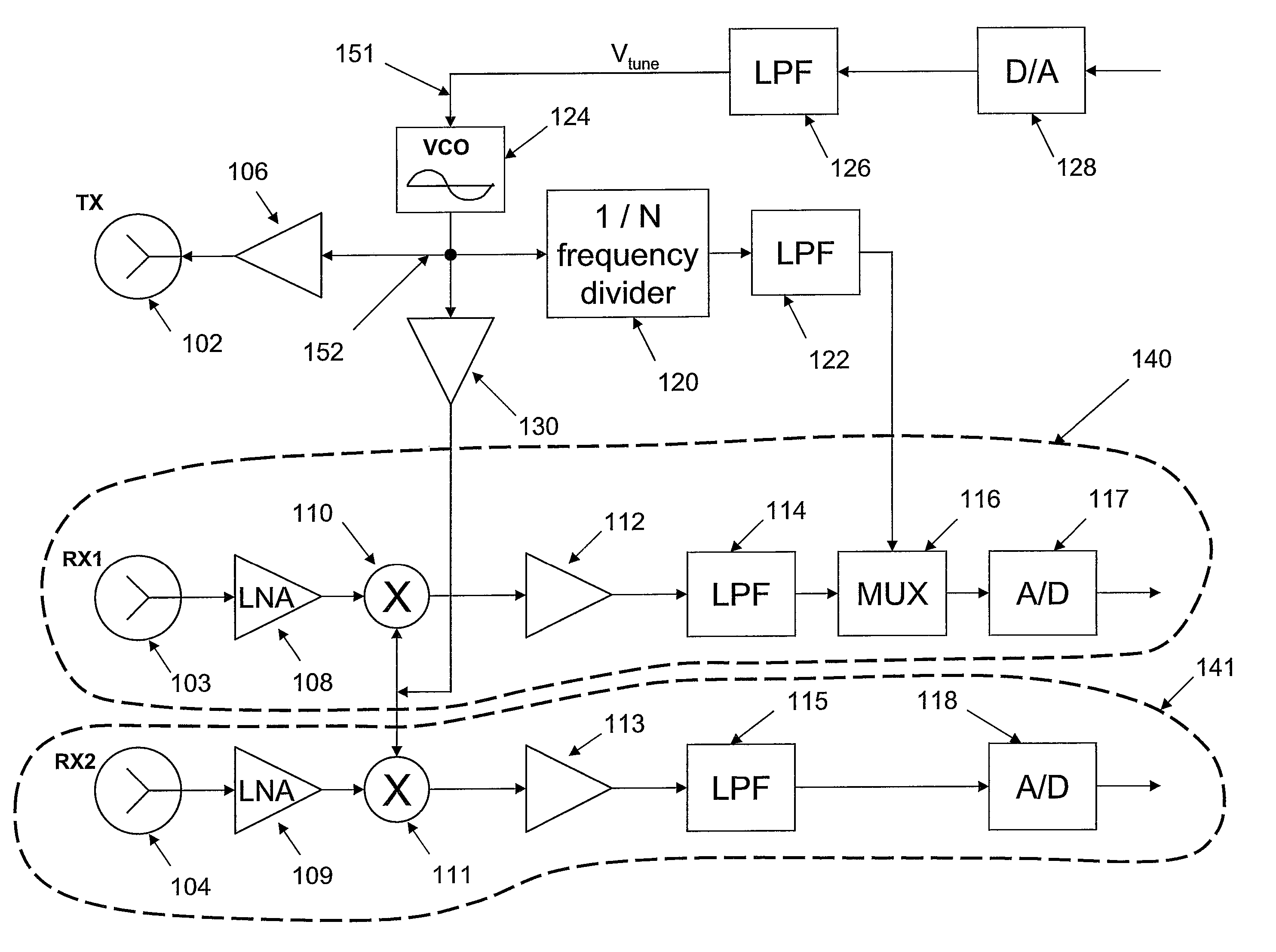

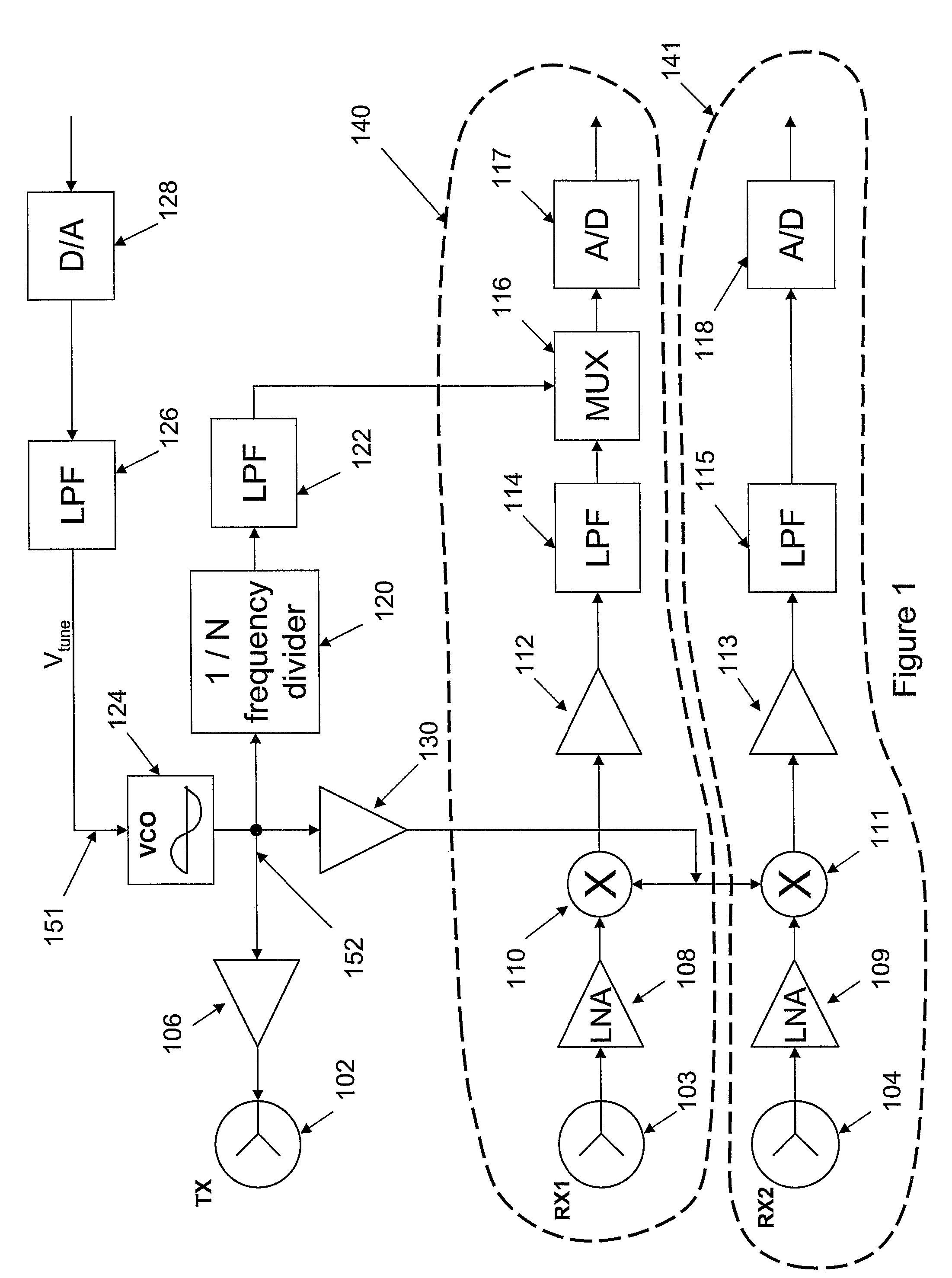

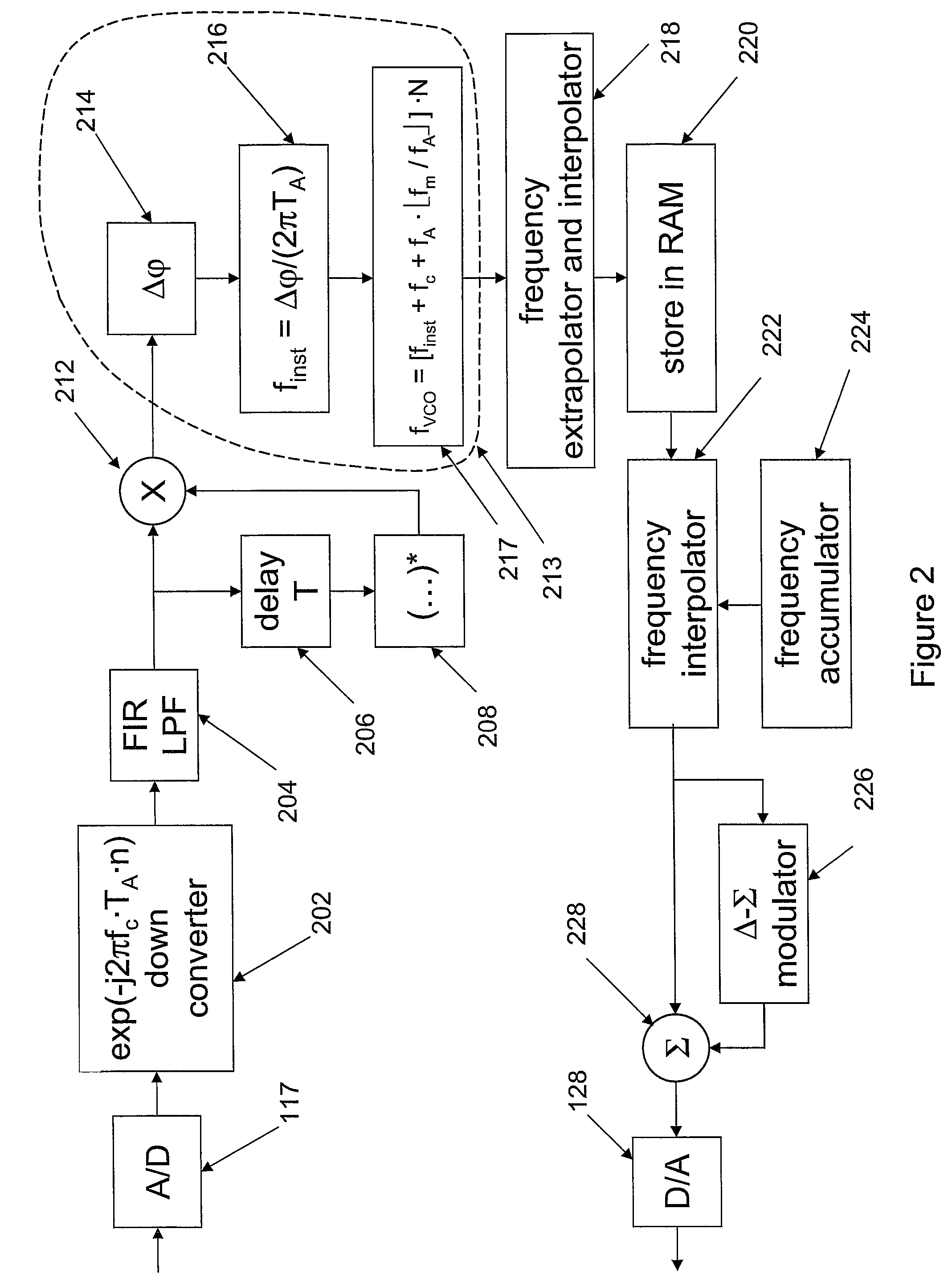

Ramp Linearization for FMCW Radar Using Digital Down-Conversion of a Sampled VCO Signal

InactiveUS20090033538A1Electrical apparatusRadio wave reradiation/reflectionRadar systemsDigital down conversion

The invention relates to an FMCW radar system and a method of operating an FMCW radar system to produce a linear frequency ramp. The FMCW radar system includes a VCO, a frequency divider coupled to the VCO output, followed by an A / D converter. A down-converter shifts the digitally converted signal to baseband samples, followed by a low-pass filter coupled to an output thereof. A VCO frequency estimator produces instantaneous VCO frequency estimates from phase differences determined from the filtered baseband samples. A D / A converter coupled to an output of the VCO frequency estimator produces an input signal for the VCO to produce therewith a linear VCO frequency ramp. A Δ-Σ modulator is coupled between the VCO frequency estimator and the input of the D / A converter to produce a dithered VCO control signal, thereby increasing the effective number of bits of the D / A converter.

Owner:INFINEON TECH AG

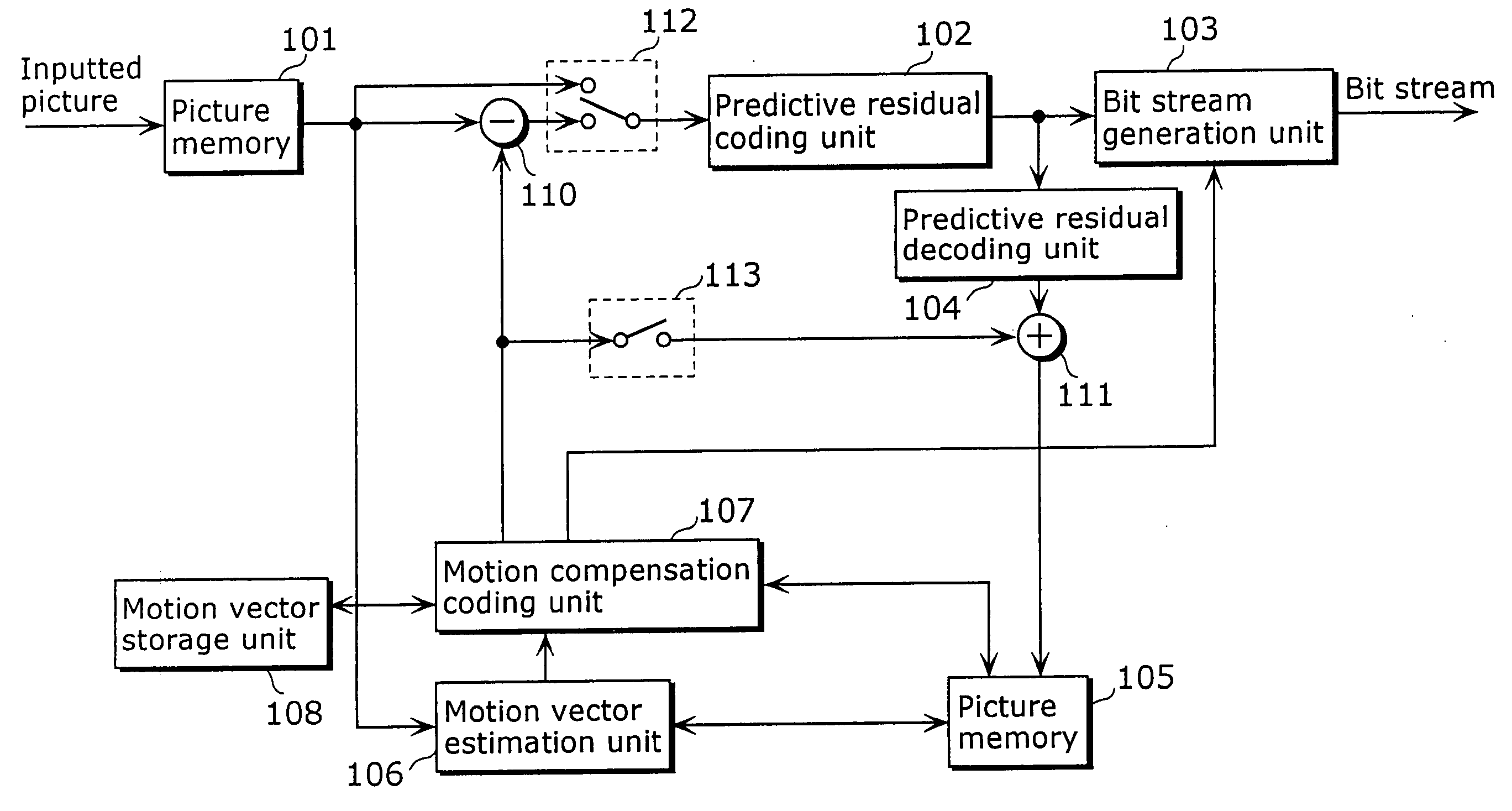

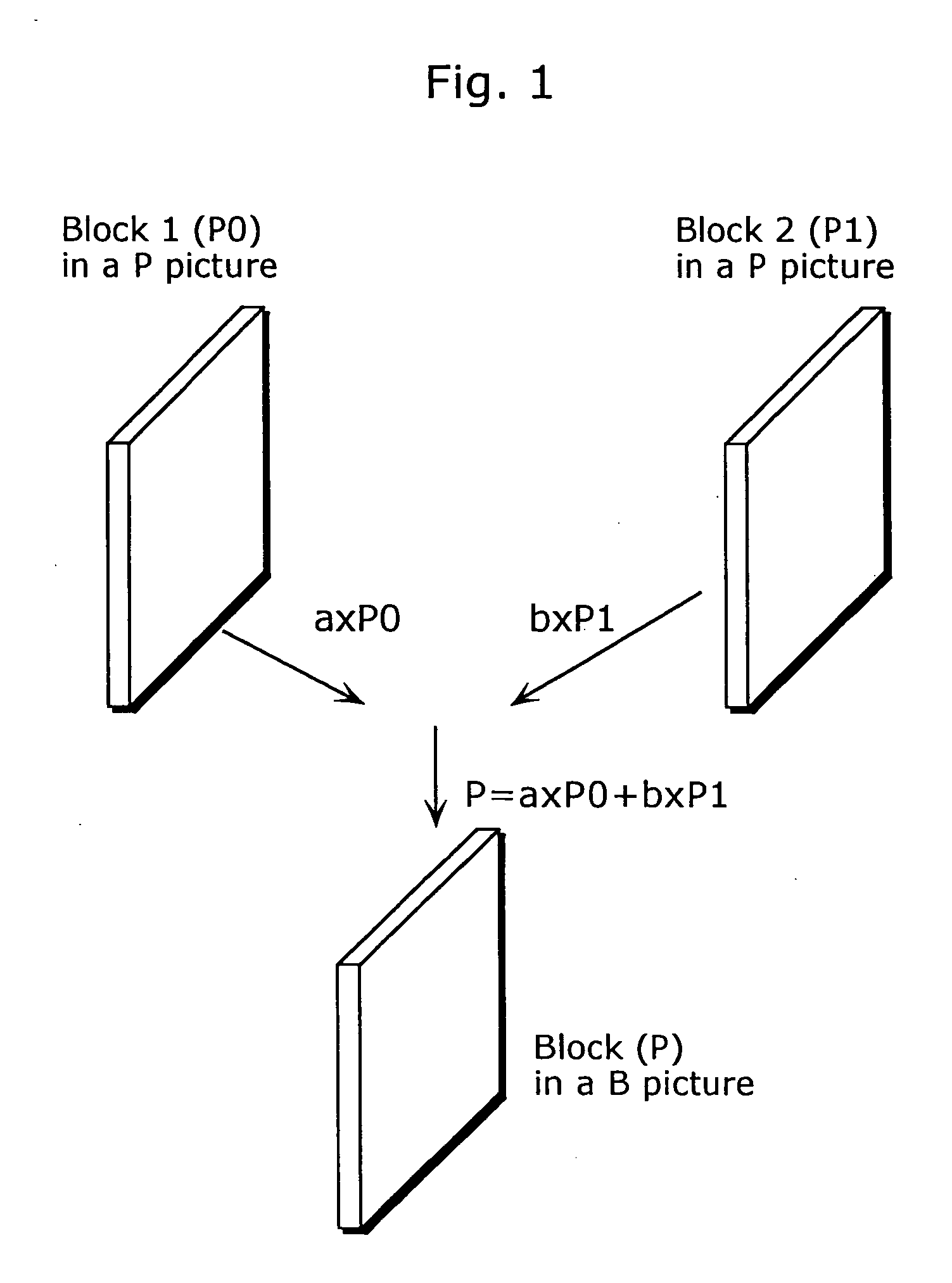

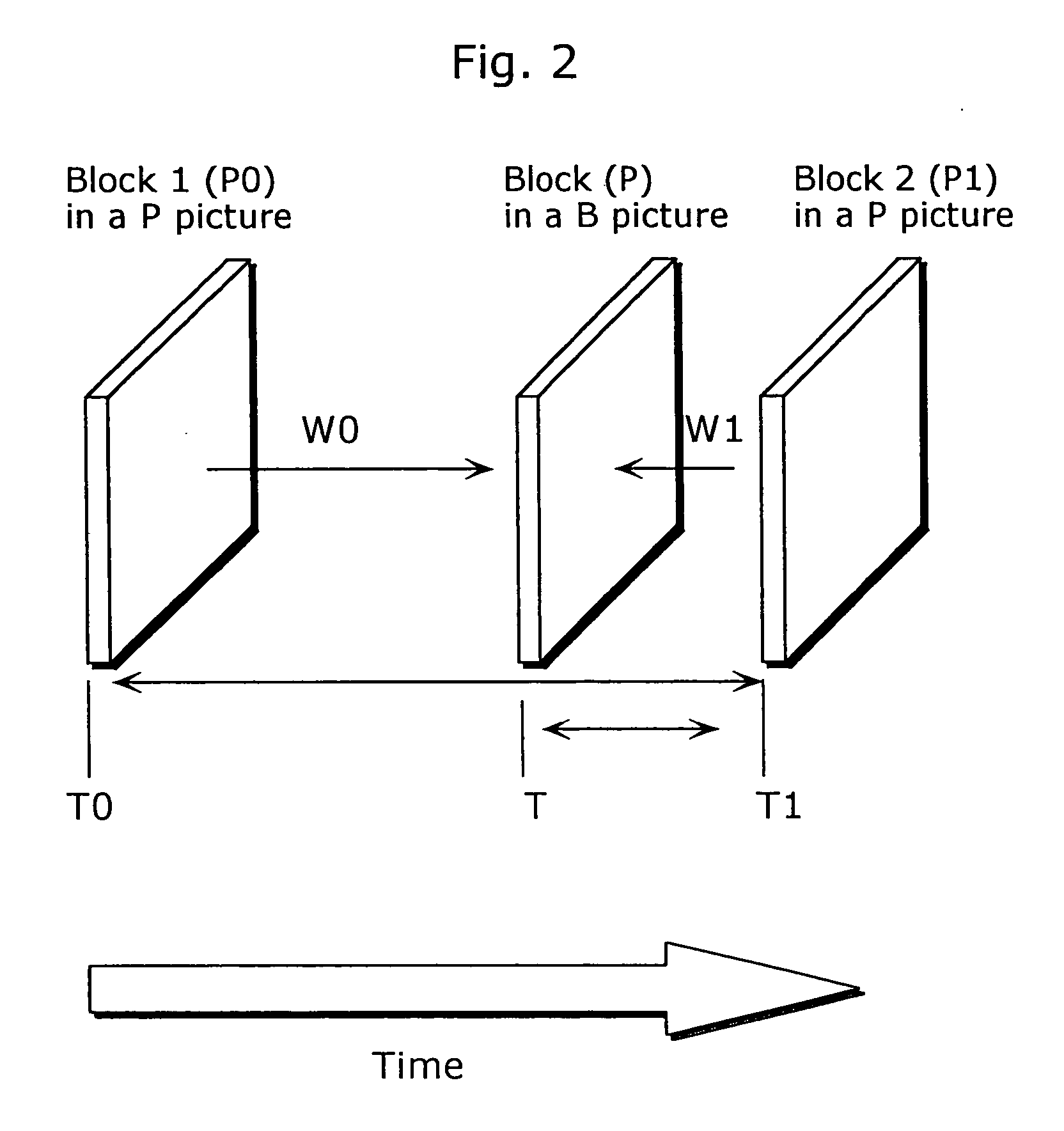

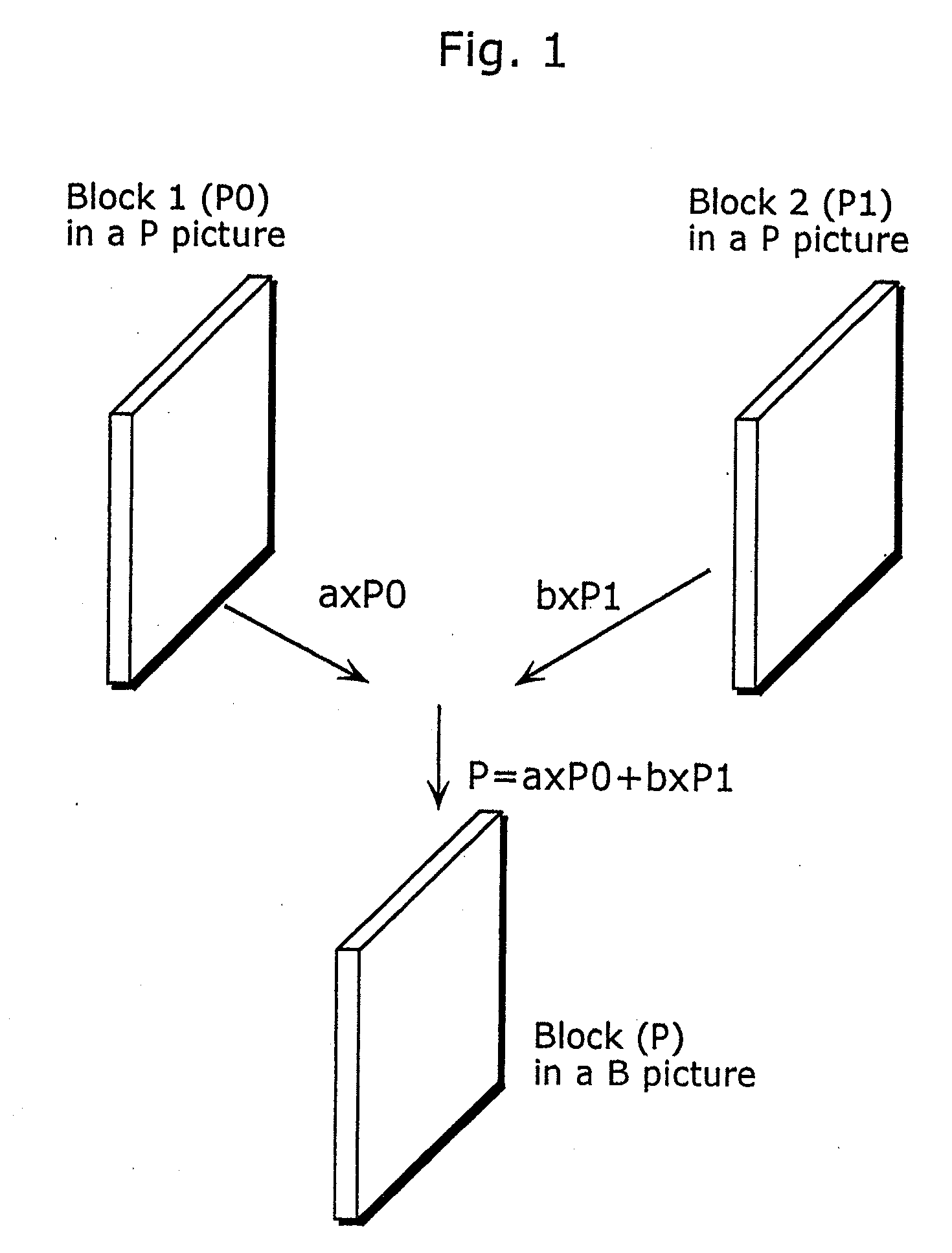

Moving picture predicting method, moving image encoding method and device, and moving image decoding method and device

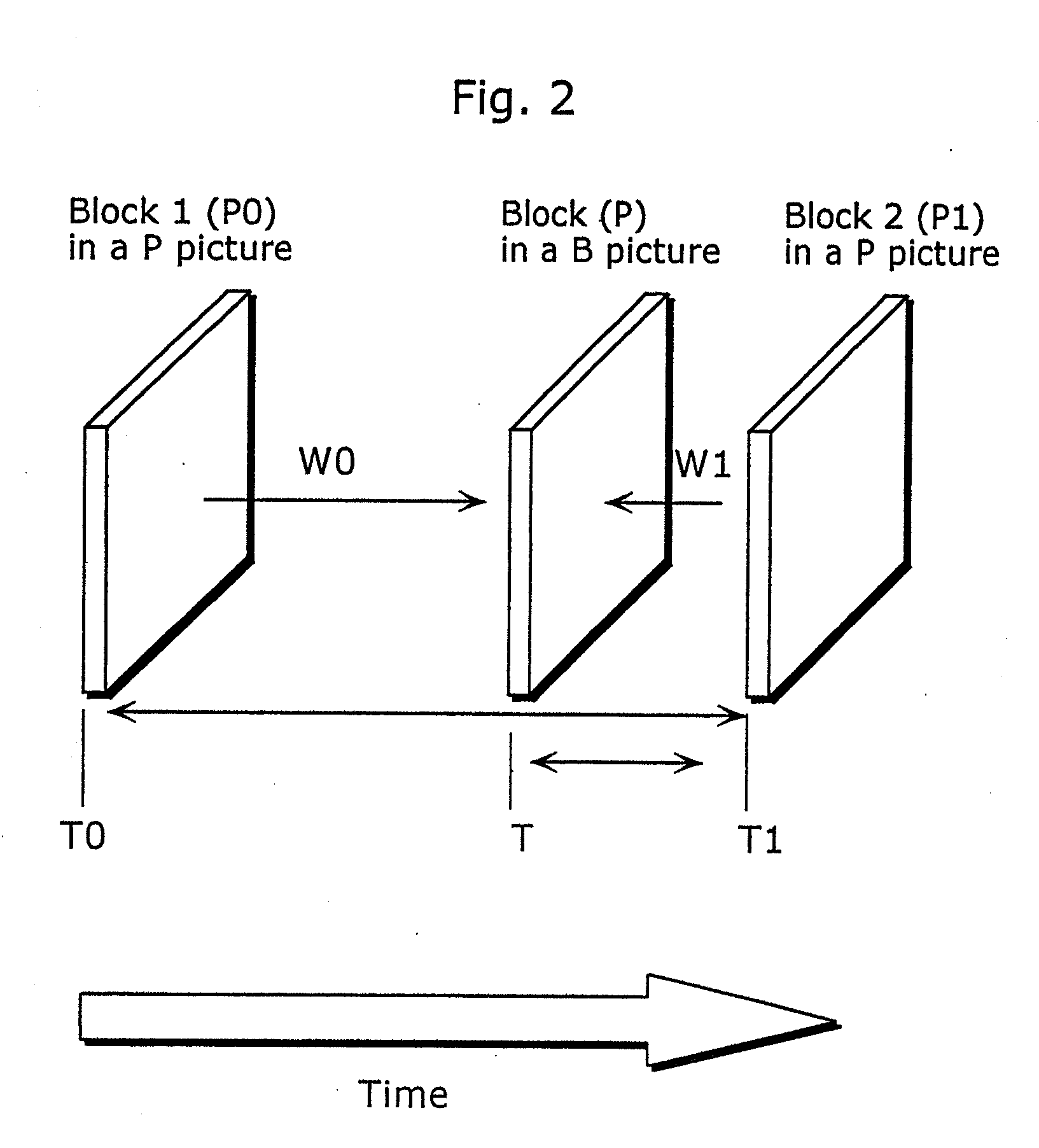

ActiveUS20050047506A1Reduce memory sizeIncrease in circuit sizeColor television with pulse code modulationColor television with bandwidth reductionAlgorithmPredictive value

A moving picture prediction method for enabling a calculation amount and a storage capacity to be reduced in a prediction about a moving picture by scaling processing is provided. A method for predicting the value P of Time T from the value P0 of Time P0 and the value P1 of Time P1 includes a step of judging whether it is possible to generate a predictive value with a predetermined significant number of bits by scaling using Time T0, T1 and T (Step S90); a step of predicting the value P from the values P0 and P1 by scaling using Time T0, T1 and T when it is possible to generate a predictive value with the predetermined significant number of bits (Step S92); and a step of predicting the value P form the values P0 and P1 without using Time T0, T1 and T when it is impossible to generate a predictive value with the predetermined significant number of bits (Step S91).

Owner:GK BRIDGE 1

Image compressor, image expander and image processing apparatus

InactiveUS20090016627A1Code conversionCharacter and pattern recognitionImaging processingObject code

Owner:KK TOSHIBA

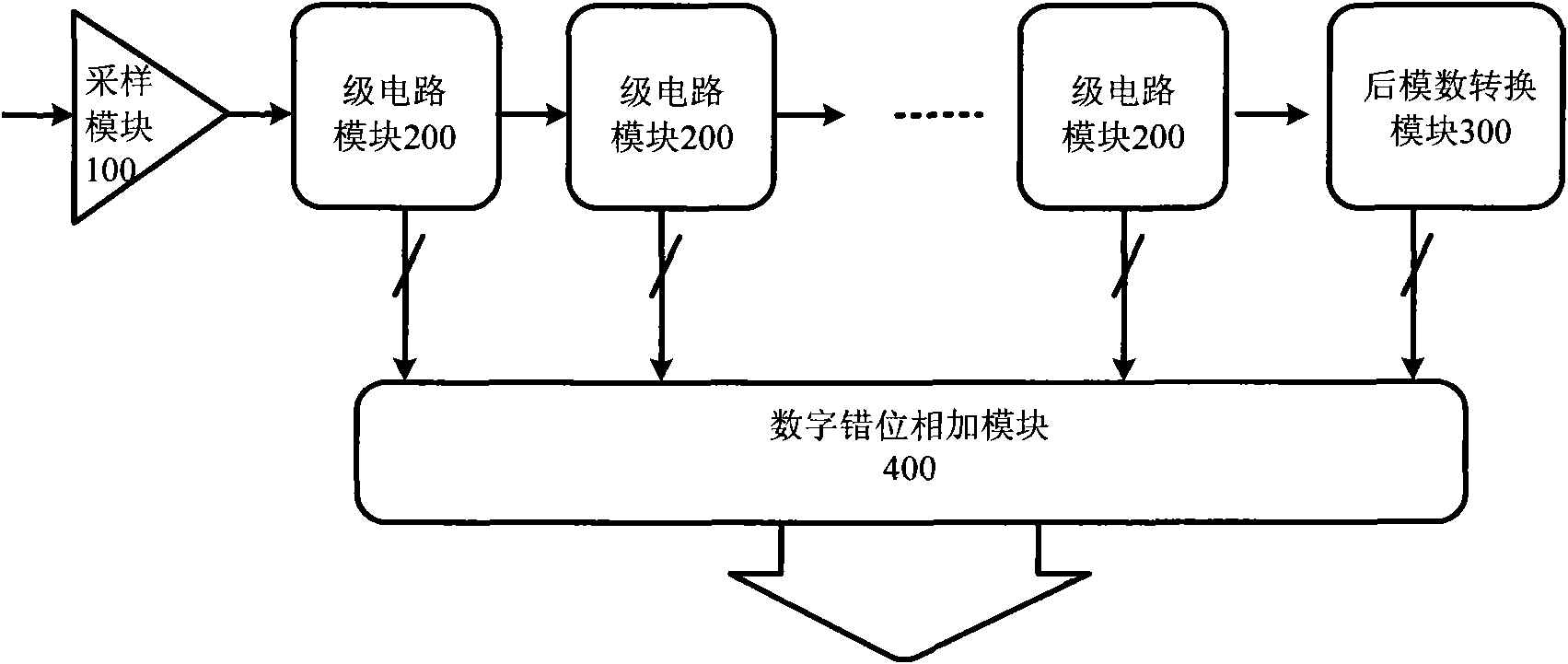

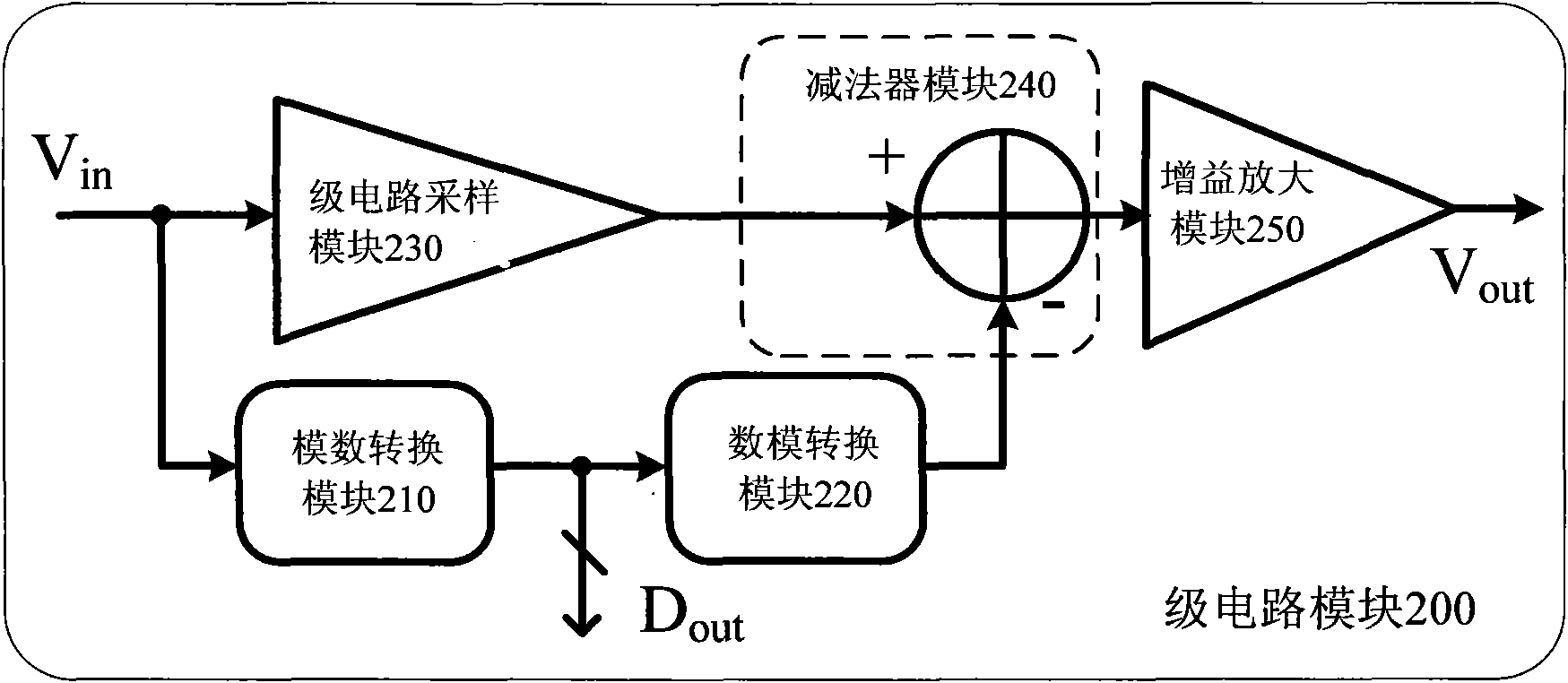

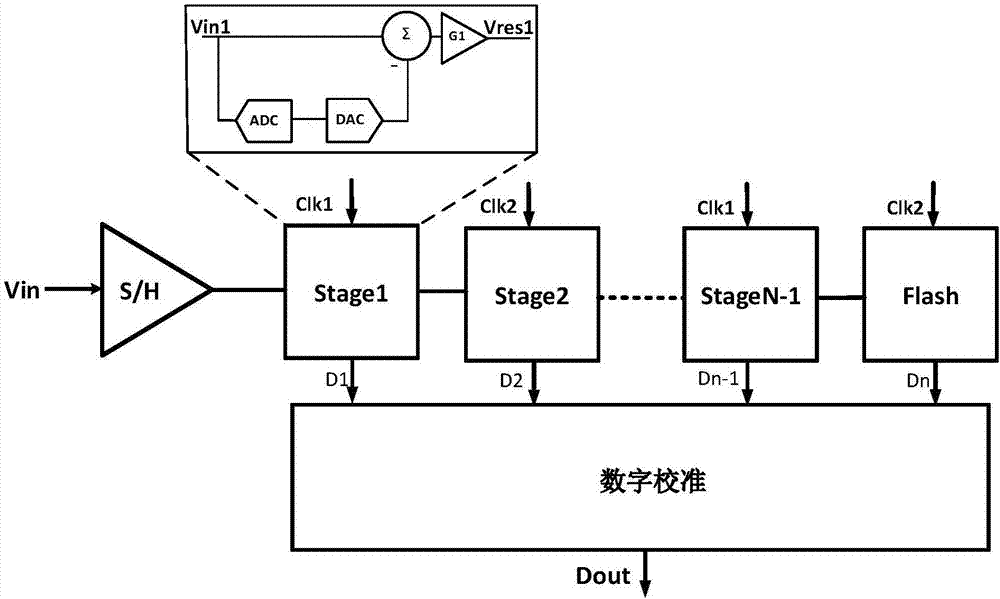

Pipeline analog-to-digital converter and quick calibration method of capacitance mismatch thereof

ActiveCN101777917AReduce calibration timeImprove linearityAnalogue-digital convertersAnalogue/digital conversion calibration/testingCapacitanceTransfer switch

The invention relates to a pipeline analog-to-digital converter and a quick calibration method of capacitance mismatch thereof. The quick calibration method is characterized by carrying out inverted order calibration from a level circuit module of the last level. The calibration method of the level circuit module of each level comprises the following steps of: 1. starting calibration: closing thesecond transfer switch and the fourth transfer switch and cutting off the first transfer switch and the third transfer switch to enable the level circuit modules to work in the calibration state; 2. measuring quantitative results: setting input signals for the level circuit modules, and carrying out analog-to-digital conversion by the level circuit modules following the corresponding level and the back analog-to-digital conversion module of the pipeline analog-to-digital converter to obtain a set of corresponding quantitative results; and 3. measuring quantitative step length: subtracting thecorresponding quantitative results to obtain the actual quantitative step length of the level circuit modules and storing the step length in a storage module. Roughly quantitative calibration resultsare added by the invention, thereby improving the linearity of the transmission function of the pipeline analog-to-digital converter and increasing the significant digit of analog-to-digital conversion.

Owner:上海迦美信芯通讯技术有限公司

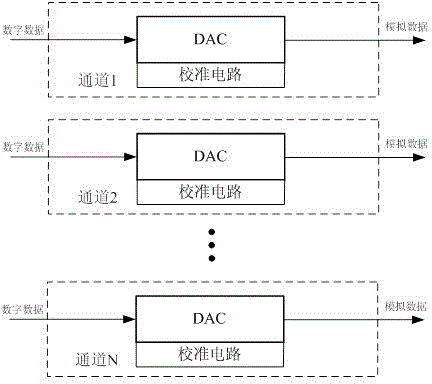

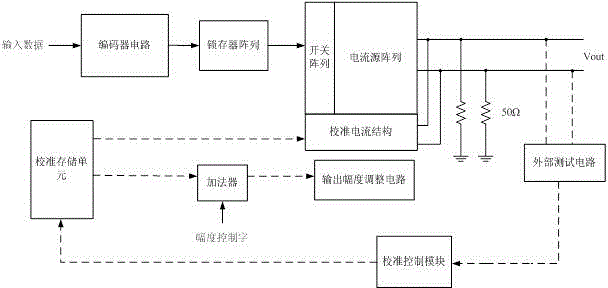

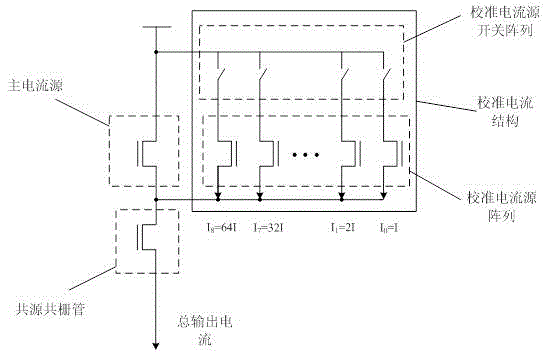

Calibration system and method suitable for current source array in multichannel sectional type current steering DAC (digital to analog converter)

ActiveCN104617953AImprove linearityIncrease the number of effective digitsAnalogue/digital conversion calibration/testingProcess deviationsBit field

The invention discloses a calibration system and a calibration method suitable for a current source array in a multichannel sectional type current steering DAC (digital to analog converter). The calibration method suitable for the current source array in the multichannel sectional type current steering DAC includes steps: firstly, calibrating a channel, and then sequentially calibrating other channels, and enabling output among all the channels to tend to be uniform, wherein when the channels are calibrated, switches in a current source switch array are by selectively closed and calibrated, and an output amplitude adjustment circuit is adjusted so as to sequentially calibrate a low data bit segment and a high data bit segment of the current source array segment by segment. The calibration method suitable for the current source array in the multichannel sectional type current steering DAC can calibrate each current source at the low data bit segment of the sectional type current steering DAC, and thereby achieves high calibration accuracy, remedies deviation and a mismatch, among the current sources in the current source array of the sectional type current steering DAC, improves linearity of the single DAC, and then improves performance indexes such as the significant number of digits of the DAC and a spurious free dynamic range, and improves linear performance of the multichannel sectional type current steering DAC and amplitude consistency among all the channels.

Owner:CHENGDU CORPRO TECH CO LTD

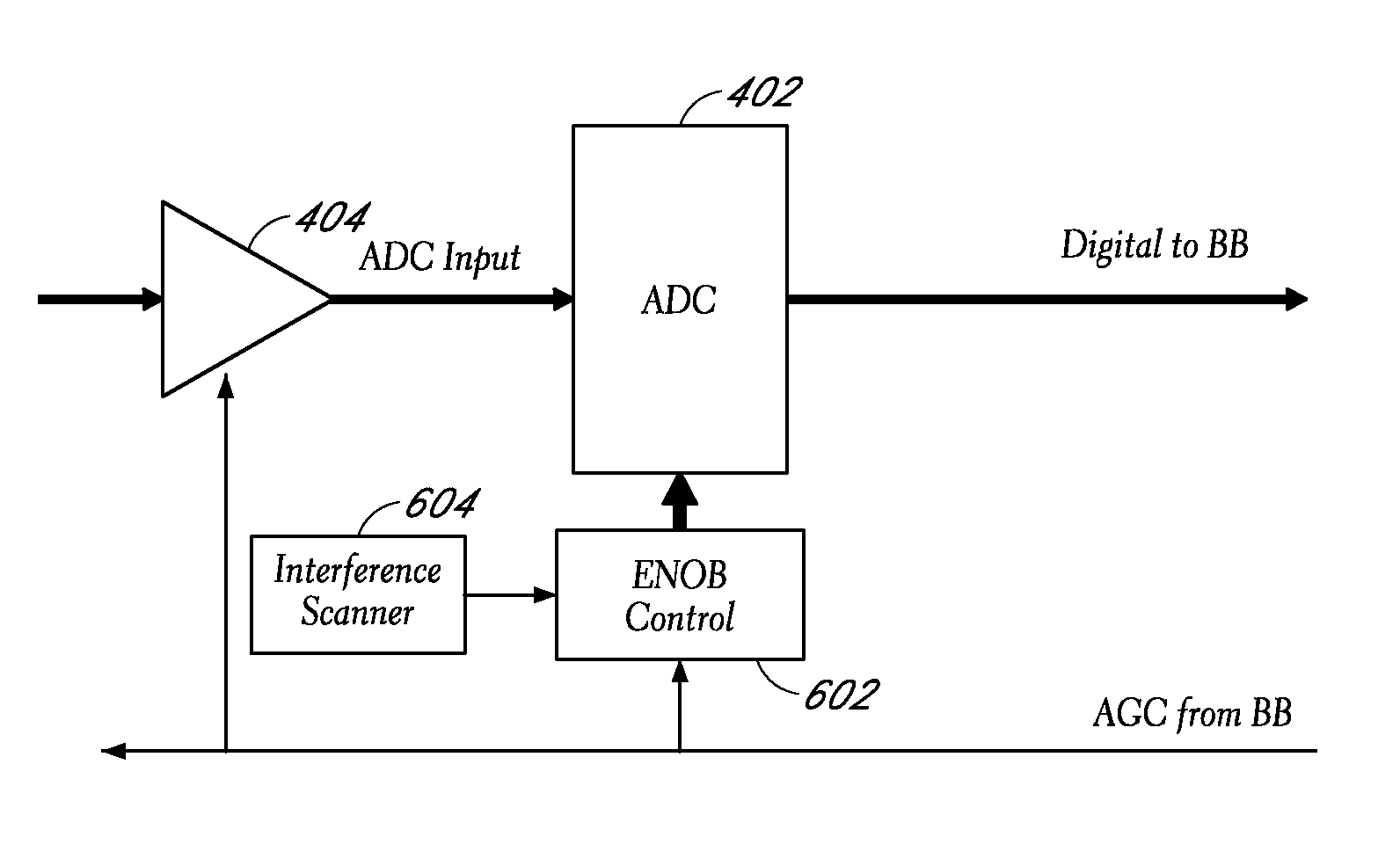

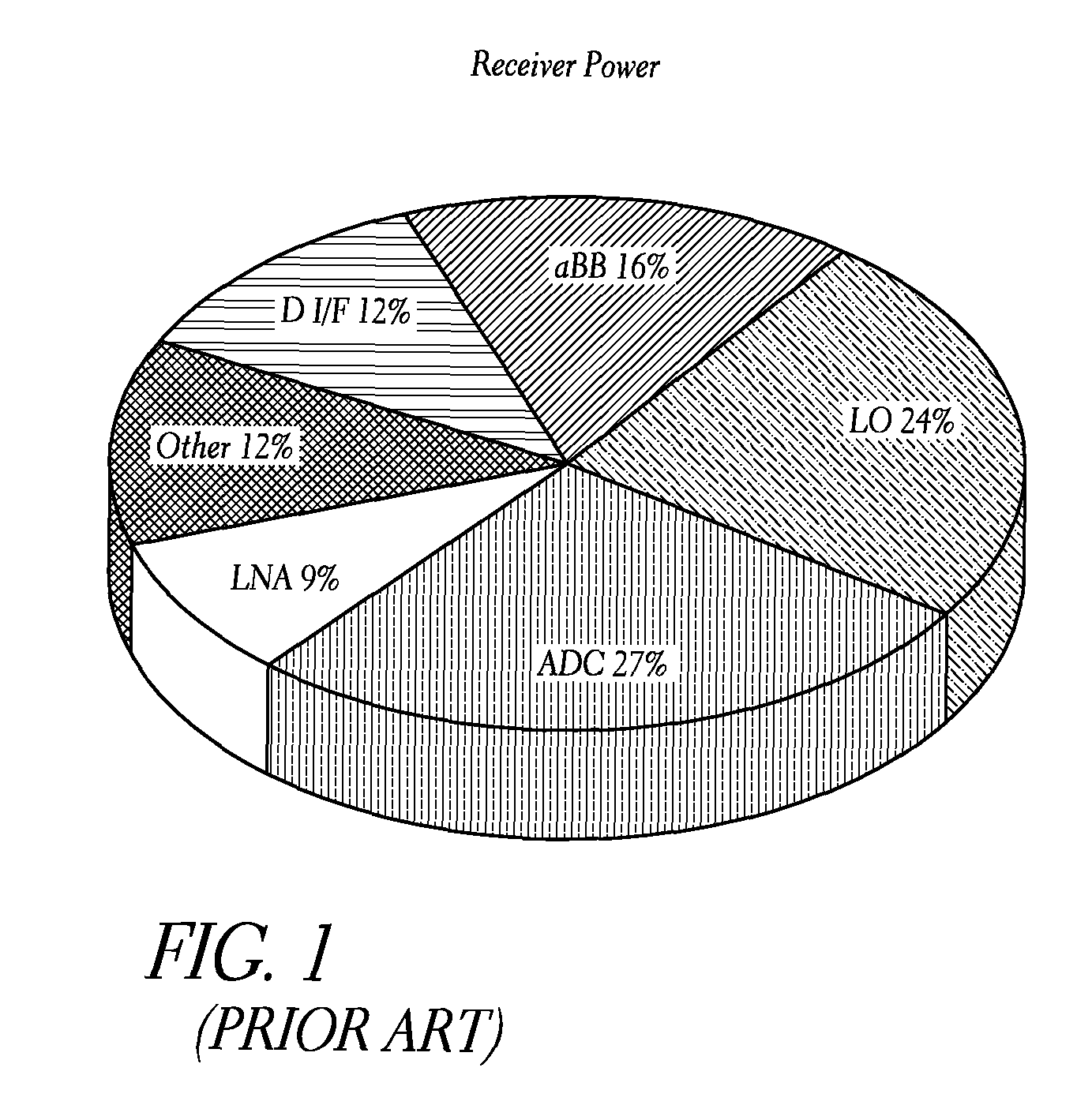

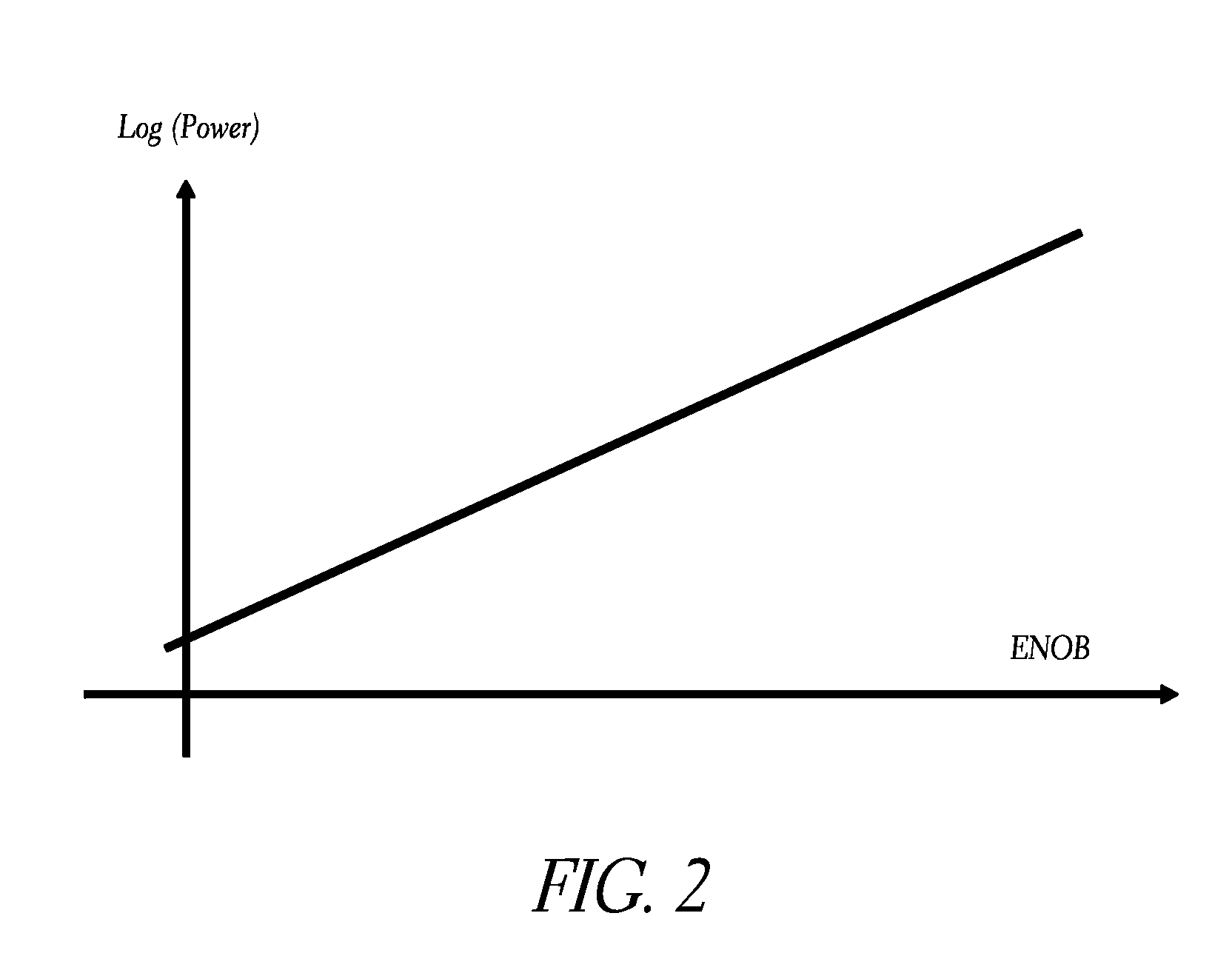

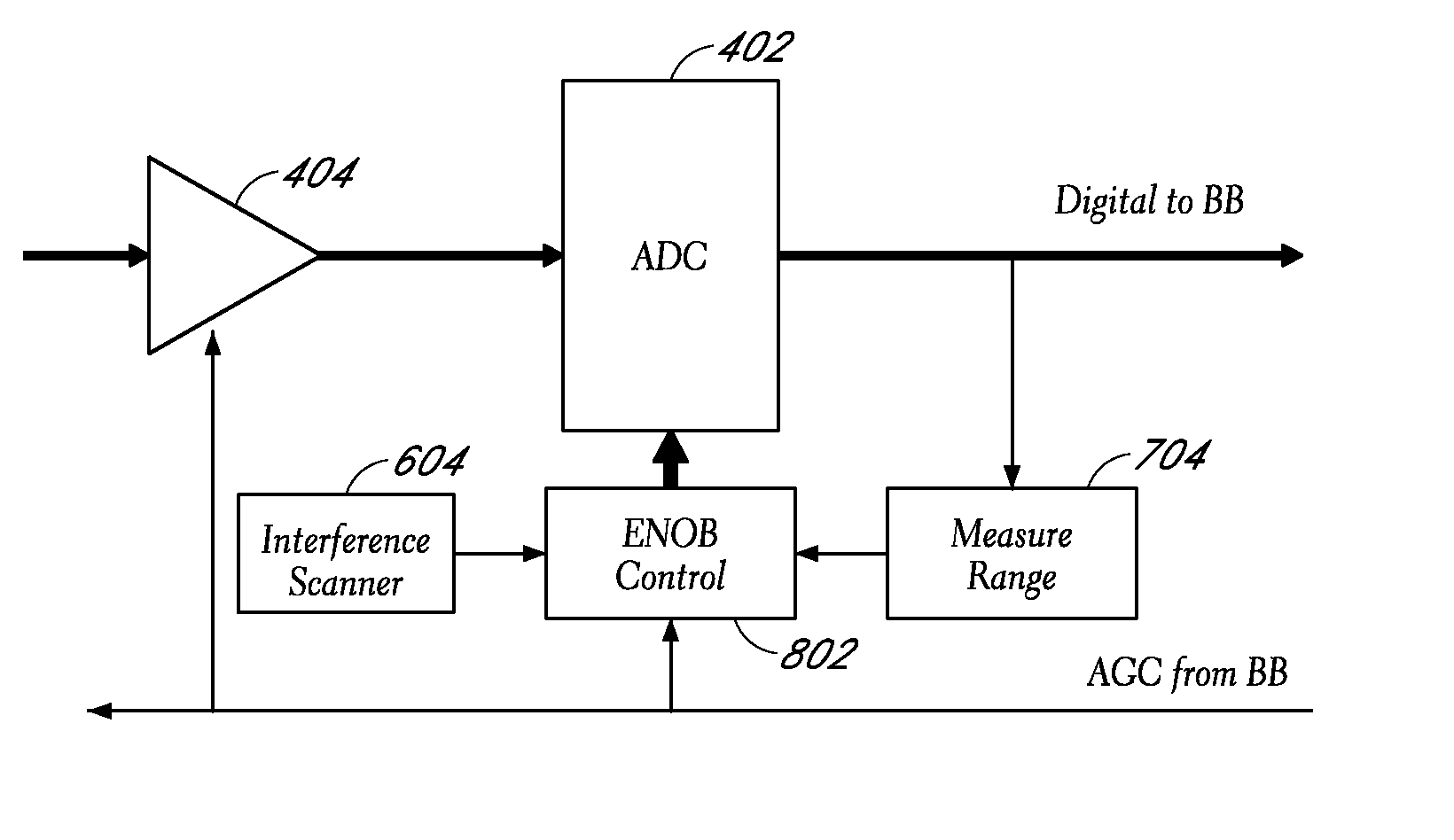

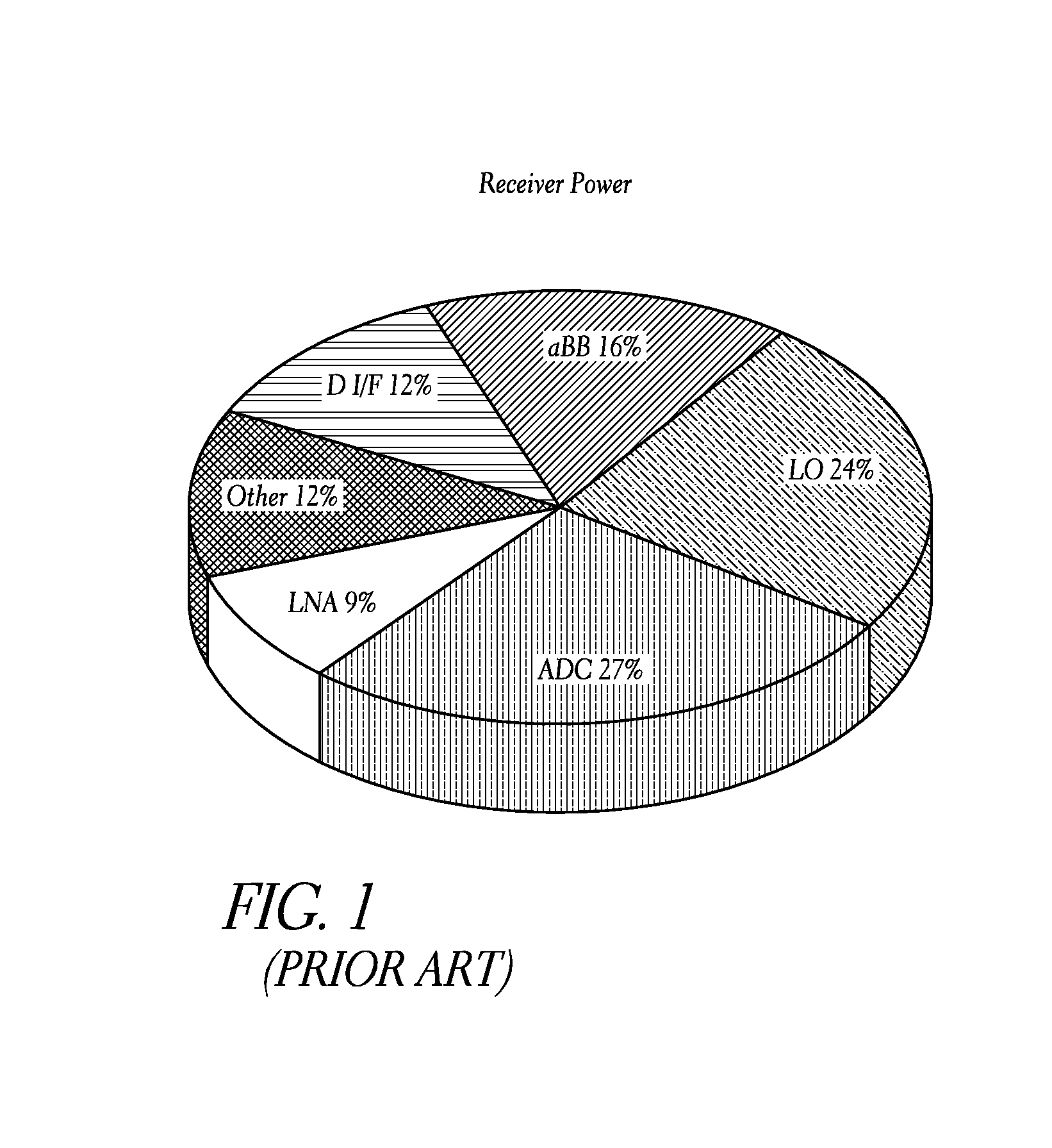

Power optimized ADC for wireless transceivers

ActiveUS7760122B1Reduce power consumptionIncrease powerPower saving provisionsElectric signal transmission systemsWireless transceiverRadio reception

An analog-to-digital converter (ADC) of a radio receiver can consume a relatively large amount of power. It is typically desirable to minimize power consumption, particularly with battery-powered devices, such as in wireless receivers. In certain conditions, the effective number of bits (ENOB) required from an ADC of a receiver can vary. The power consumption of certain ADC topologies, such as pipelined converter topologies, can vary with the number of bits. One embodiment dynamically varies the ENOB of an ADC to more optimally consume power. This can extend battery life.

Owner:MAXLINEAR ASIA SINGAPORE PTE LTD

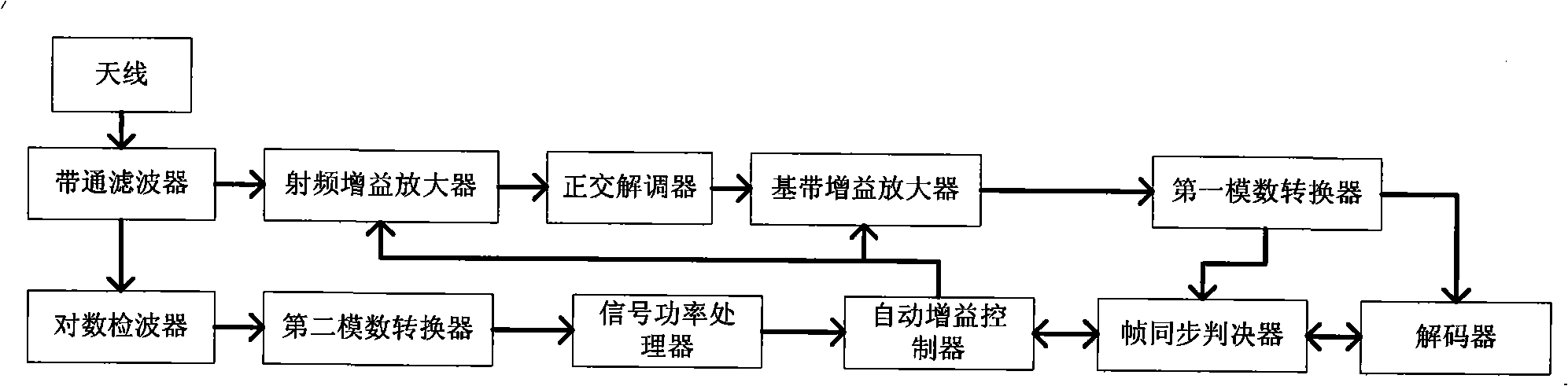

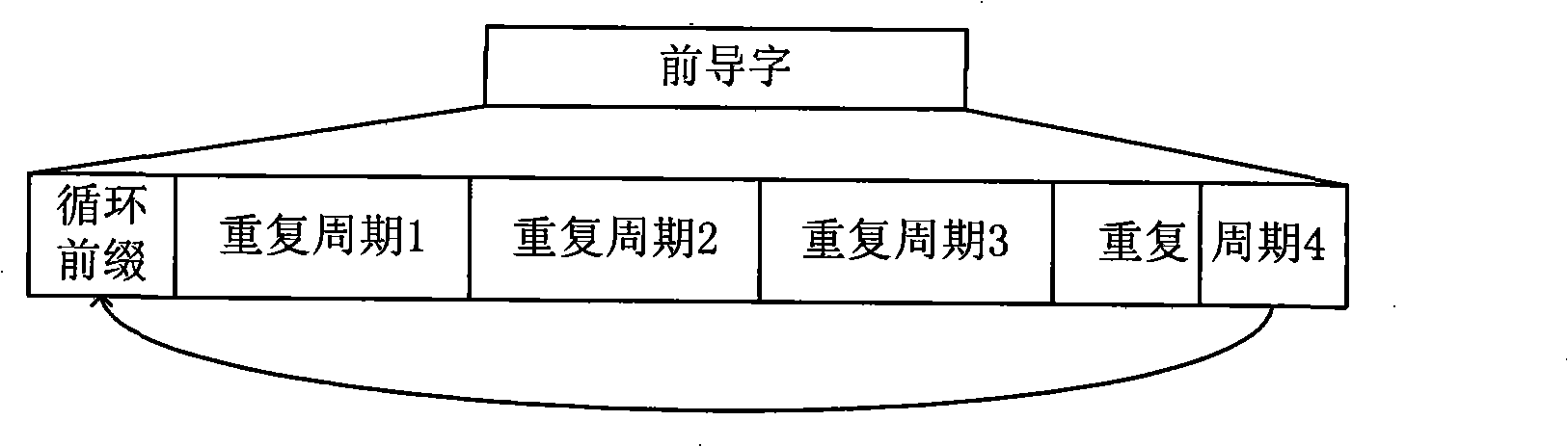

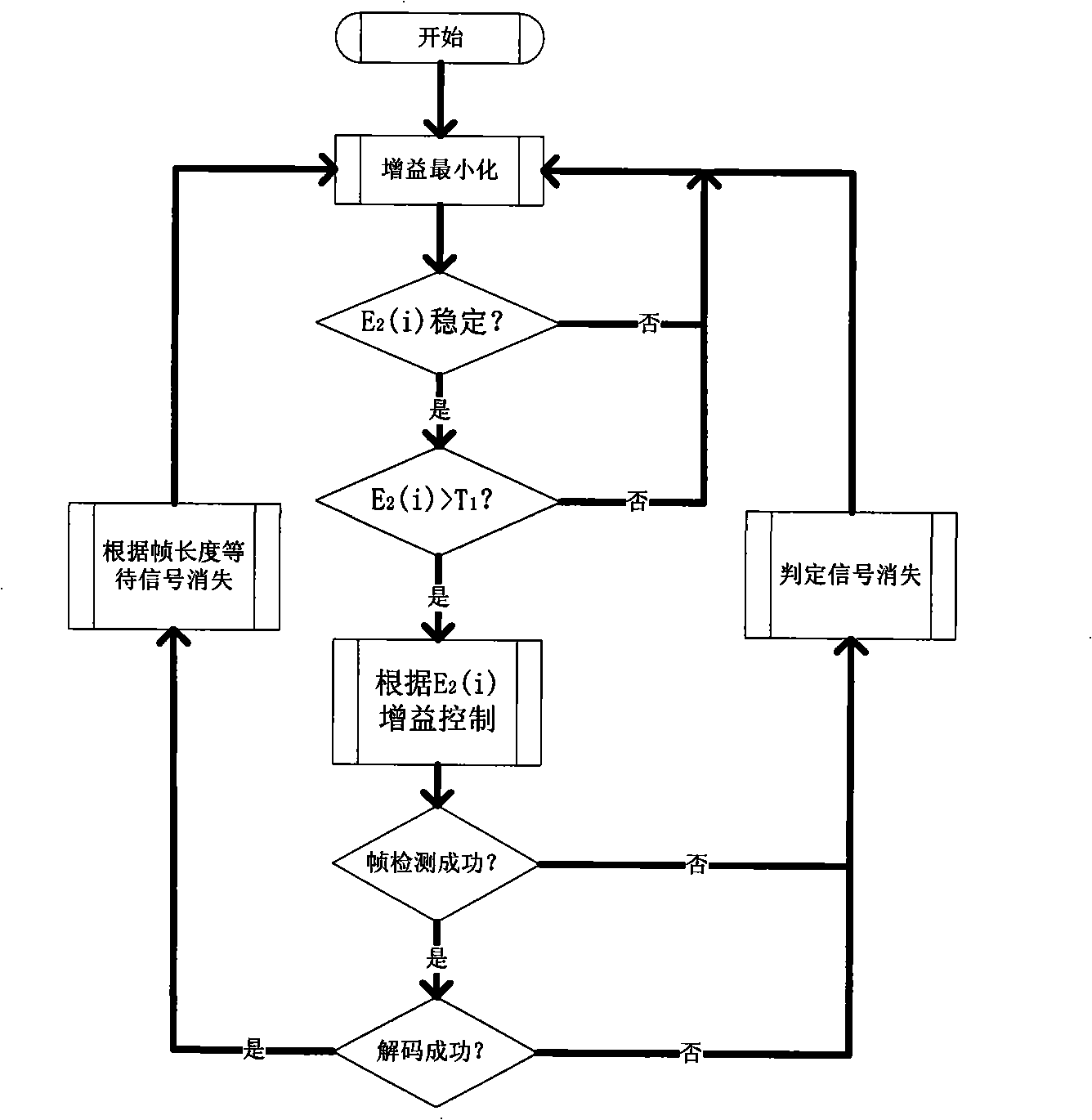

Orthogonal frequency division multiplexing receiver system and its automatic gain control method

InactiveCN101257472AEasy to detectIncrease success rateMulti-frequency code systemsComputation complexityBand-pass filter

The invention provides an orthogonal frequency division multiplexing receiving system and an automatic gain control method. The antenna of the system is connected with a band-pass filter, a radio frequency gain amplifier, an orthogonal demodulator, a baseband gain amplifier, a first digital-to-analog converter, a decoder, a frame alignement judging device, an automatic gain controller, a signal power processor, a second digital-to-analog converter, a ogarithmic detector, a band-pass filter in turn, wherein the automatic gain controller is respectively connected with the baseband gain amplifier, the radio frequency gain amplifier, while the first digital-to-analog converter is connected with the frame alignement judging device. The gain control method is that the receiver carries the logarithm demodulation on the received signals, to control the system gain according to the power detecting result and the state of the two modules of frame synchronization and the decoder, to reach the aim of correctly adjusting the system gain. The invention has high detecting precision, small computation complexity, short response time, which is suitable to orthogonal frequency division multiplexing receiving system and can effectively increase the significant figure of the analog-to-digital converter.

Owner:ZHEJIANG UNIV

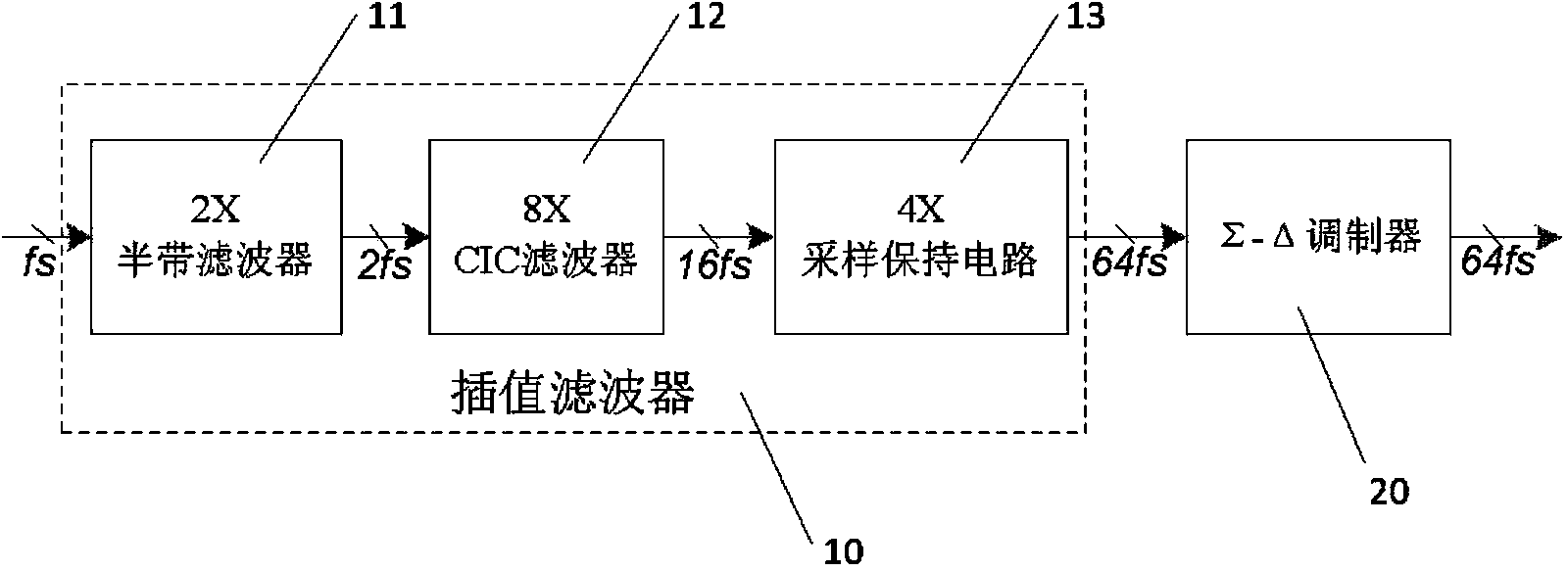

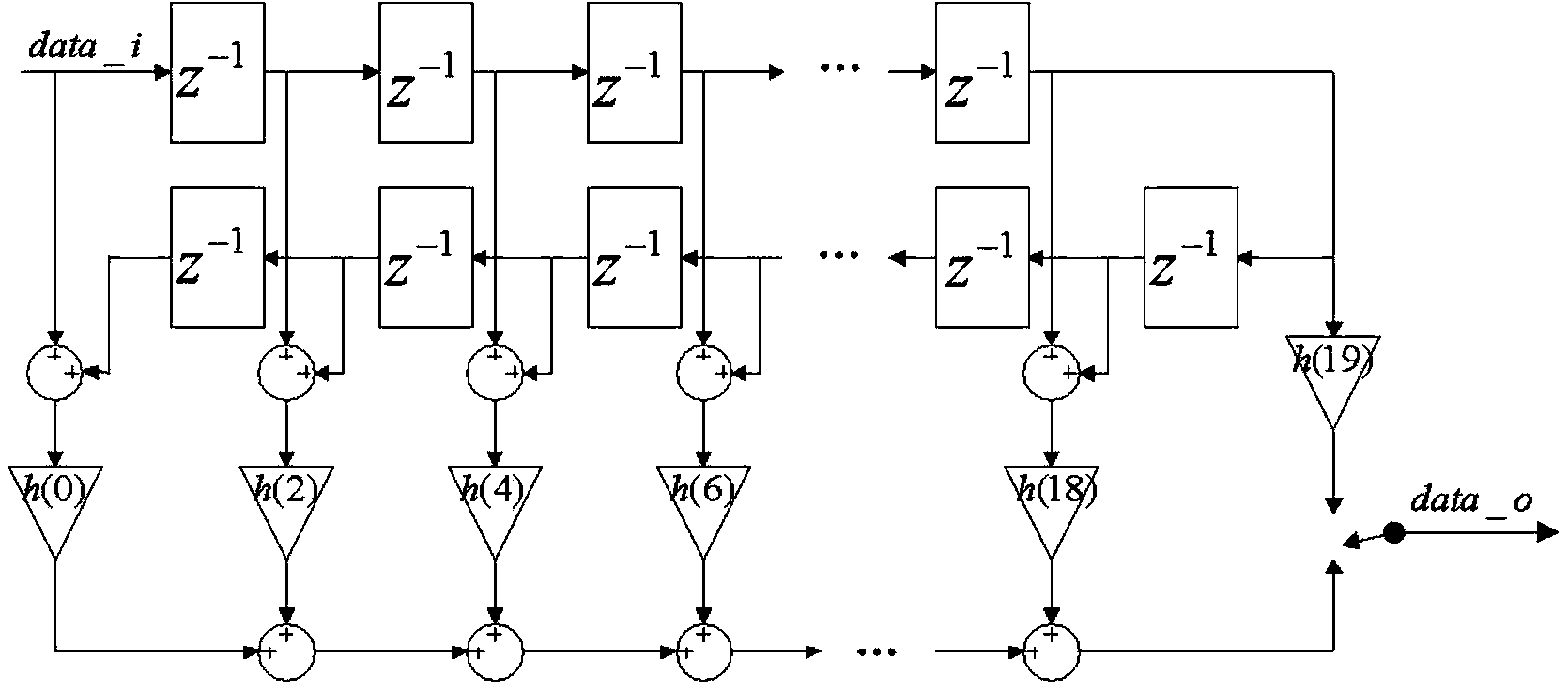

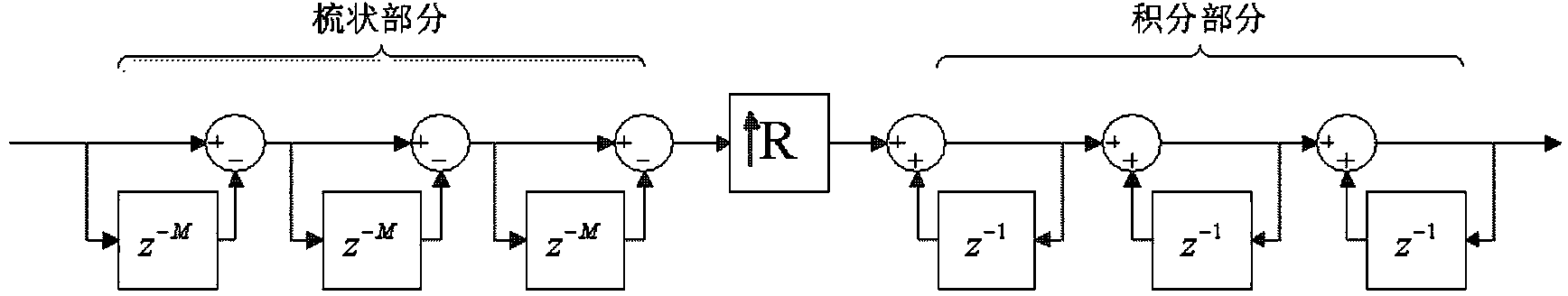

Oversampling 64-time sigma-delta modulation circuit with effective bit being 18

InactiveCN103944575ASimple structureReduce the occupied areaAnalogue conversionReconstruction filterSignal-to-noise ratio (imaging)

The invention provides an oversampling 64-time sigma-delta modulation circuit with an effective bit being 18. The circuit comprises an interpolation filter and a sigma-delta modulator. The interpolation filter is used for conducting oversampling interpolation and filtering on digital input signals. The input end of the sigma-delta modulator is connected with the output end of the interpolation filter, the sigma-delta modulator is used for modulating oversampled digital signals, shaping quantized noise introduced by a quantizer, moving noise in the signal bandwidth out of the bandwidth, and meanwhile guaranteeing that transmission of the signals is not affected, and output 1-bit 0 / 1 code streams need to be restored through a backward-stage analog reconstruction filter so as to acquire analog signals. An improved structure is adopted in a half-band filter in the interpolation filter so that the area of the half-band filter can be greatly reduced; for the sigma-delta modulator, a monocycle high-order structure easier to achieve is adopted, the stability problem is analyzed, the high signal to noise ratio is achieved, and meanwhile stability of the modulator is guaranteed.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

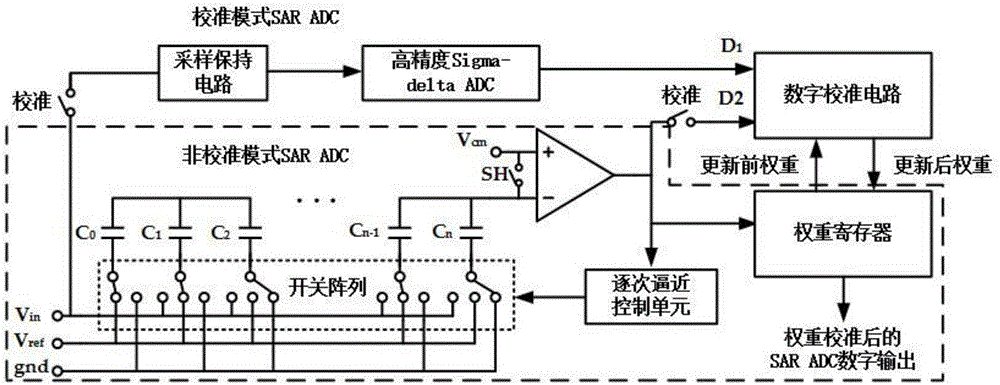

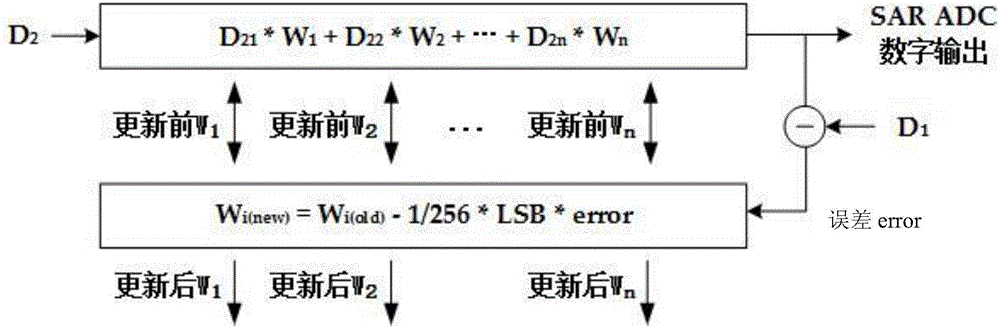

In-plate digital self calibration capacitive successive approximation analog-to-digital converter and self calibration method thereof

ActiveCN107437944AValid calibrationAnalogue/digital conversionElectric signal transmission systemsEngineeringAnalog-to-digital converter

The invention discloses an in-plate digital self calibration capacitive successive approximation (SAR) analog-to-digital converter and a self calibration method thereof. The analog-to-digital converter comprises a weight register, a capacitive SAR ADC and a calibration unit, wherein the calibration unit comprises a sigma-delta ADC, a sample hold circuit and a digital calibration circuit, an input end of the sample hold circuit is connected with a signal input end, an output end of the sample hold circuit is connected with the digital calibration circuit through the sigma-delta ADC, a comparator output end of the capacitive SAR ADC is connected with the digital calibration circuit, the digital calibration circuit is connected with the weight register and is used for carrying out update weight values of the weight register according to D1 and D2, and the weight register is connected with the comparator output end of the capacitive SAR ADC. The analog-to-digital converter is advantaged in that the valid bit number of an analog to digital conversion circuit is improved, and area cost of a calibration circuit is reduced.

Owner:北京大学(天津滨海)新一代信息技术研究院

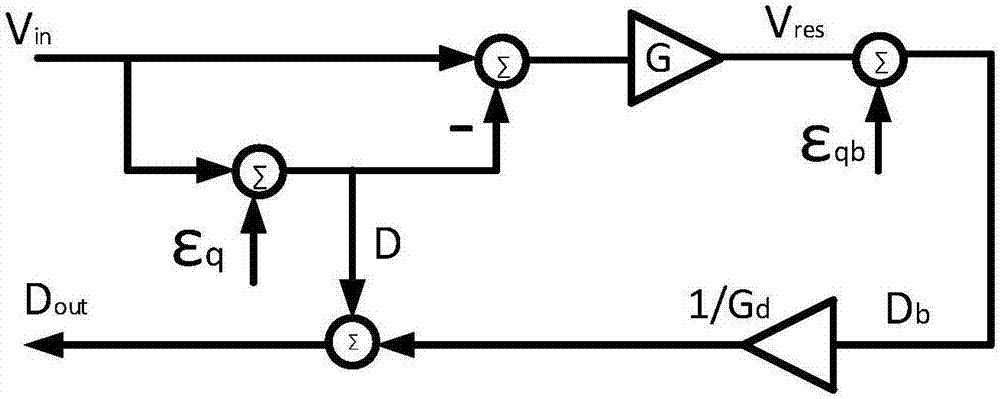

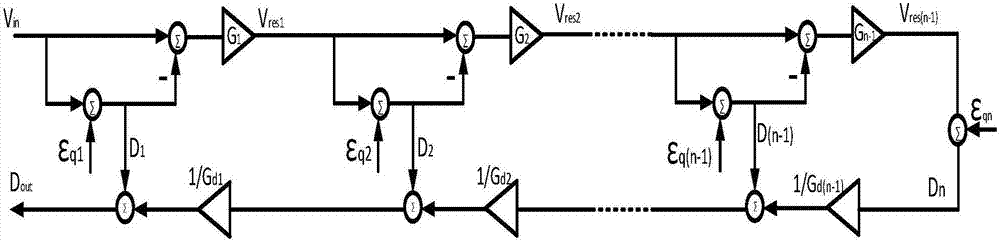

Front-end calibration method for assembly line ADC based on minimum quantization error

ActiveCN107359878AReduce non-linearityImprove the shortcomings of low precision of traditional calibrationAnalogue/digital conversion calibration/testingFourier transform on finite groupsAssembly line

The invention, which belongs to the technical field of the analog integrated circuit, provides a front-end calibration method for an assembly line ADC. Correction is carried out by starting with a first-stage gain of an assembly line ADC until completion of a previous (N-1)th-stage gain of the assembly line ADC to realize front-end calibration once. When the gains from the first stage to the (N-1)th stage are obtained, an error between a restored signal and an original signal is obtained. Before calibration, an analog output of the previous (N-1)th stage of the assembly line ADC is obtained by using a digital output of a flash memory type ADC. During the calibration process, the gain at each stage of the assembly line ADC is searched based on an MATLAB program; the output data are stored of the assembly line ADC and a fast fourier transform analysis is carried out on the restored signal; and when indexes like an effective bit number meet requirements, gain searching is determined to be corrected to realize assembly line ADC calibration. Therefore, a defect of low traditional calibration precision in the high-speed high-precision assembly line ADC is overcome; rapid, correct and high-efficiency calibration is realized; and the front-end calibration method is suitable for calibration of a high-speed high-precision assembly line ADC.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

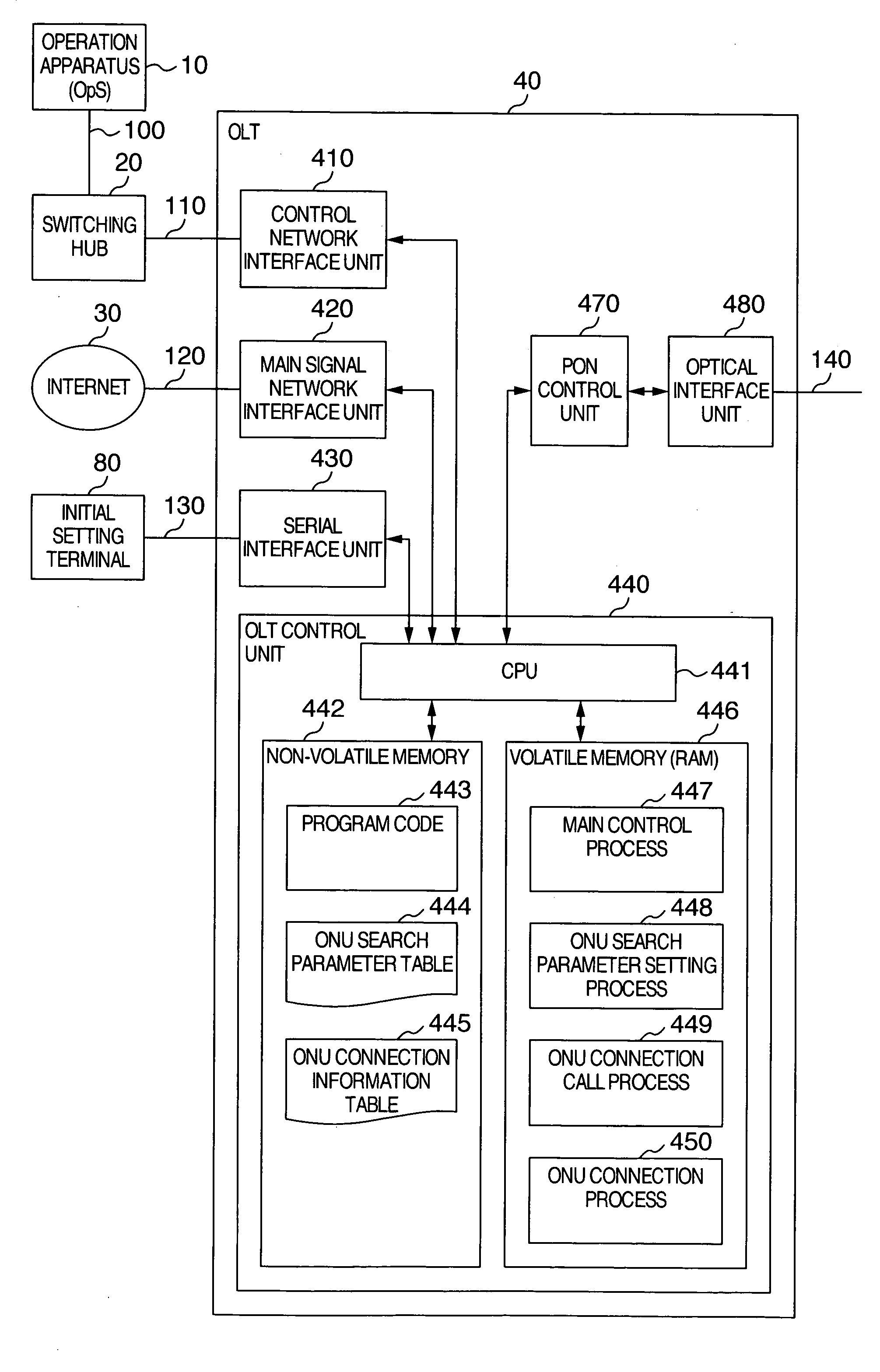

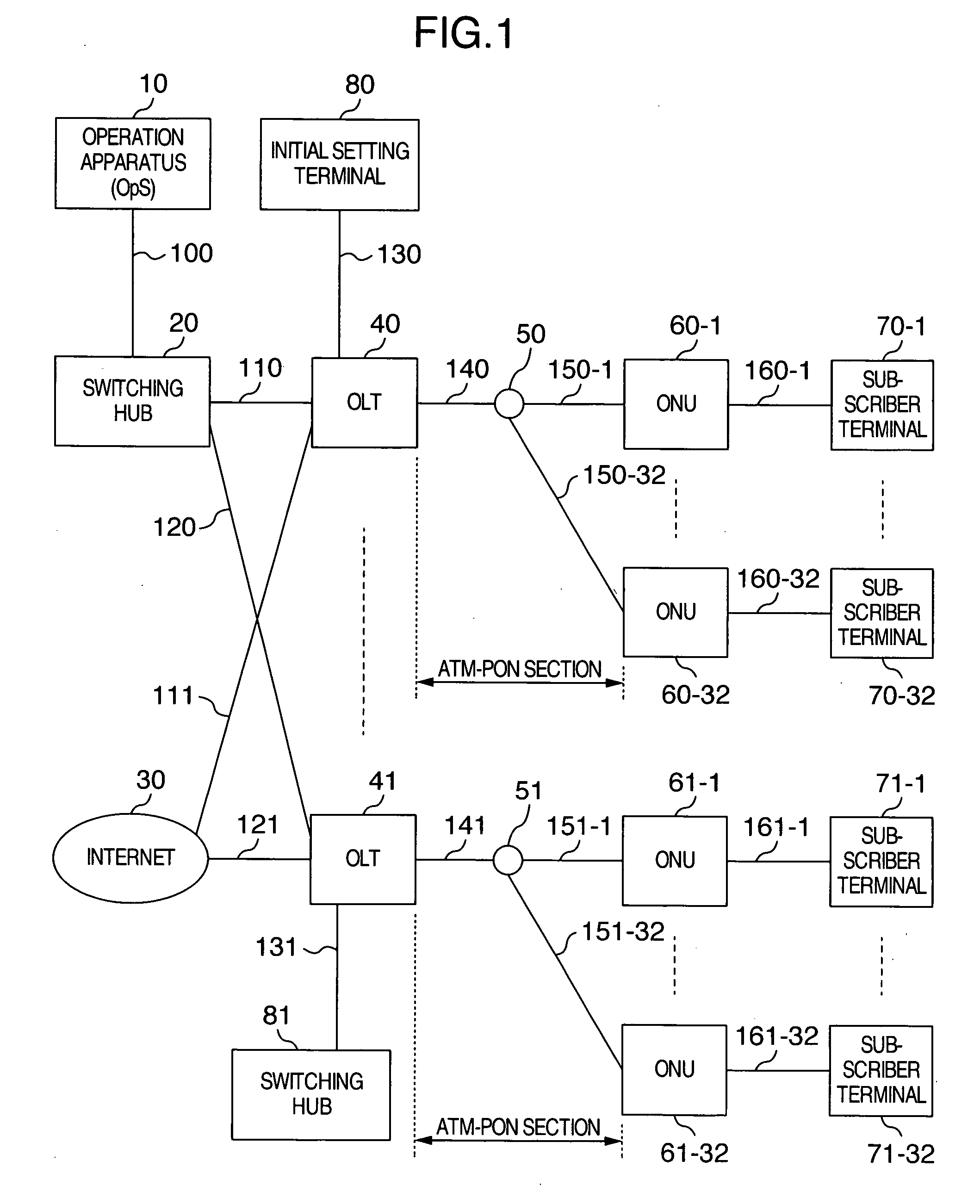

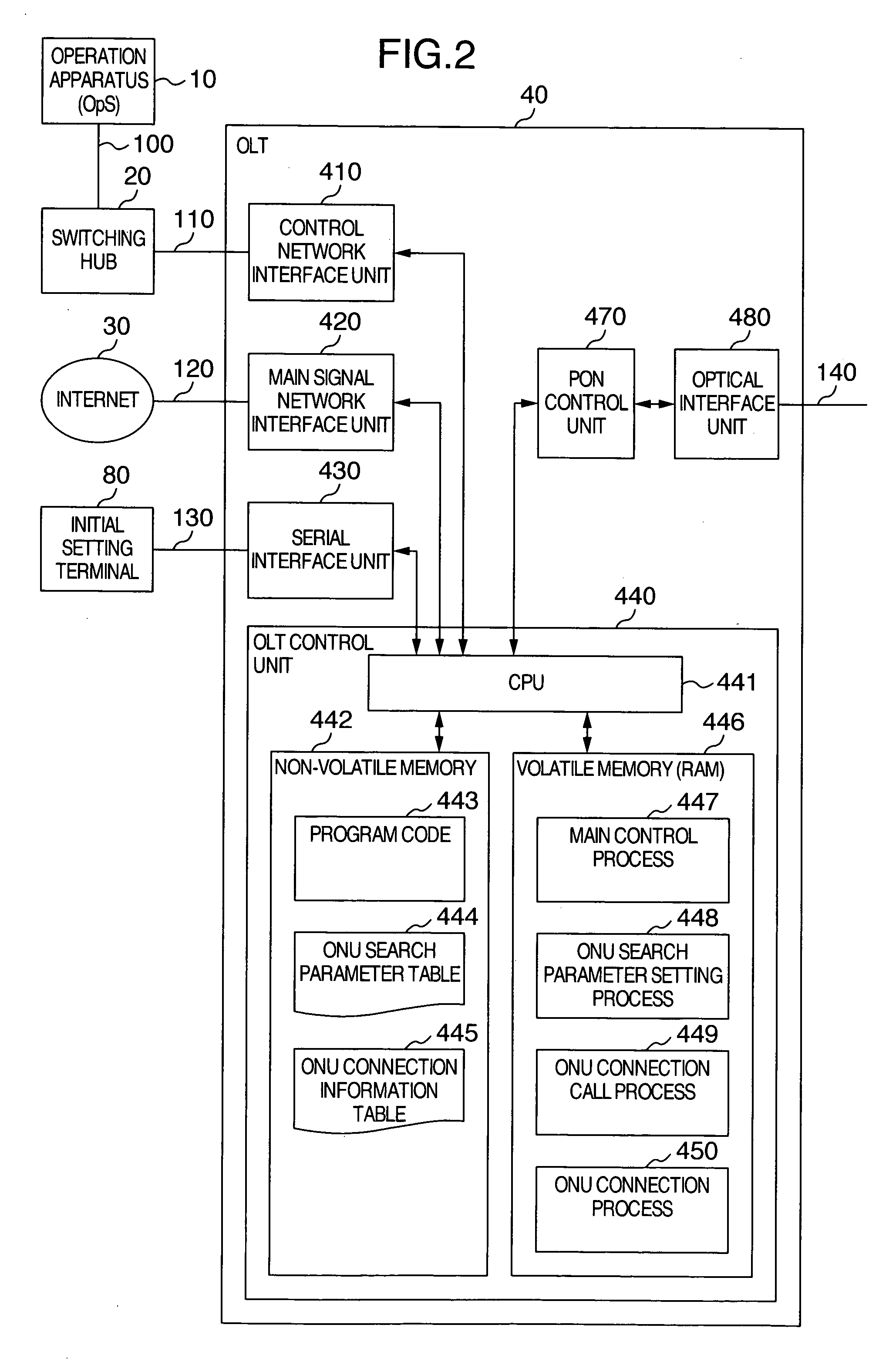

ATM-PON system and ONU automatic connection method

InactiveUS20060256811A1Reduce loadMultiplex system selection arrangementsTime-division multiplexSerial codeEffective number of bits

OLT is provided with a field for storing the number of effective bits for searching ONU serial numbers, a field for storing a search start serial number and a field for storing a search end serial number, and ONU serial numbers are searched from the search start serial number to the search end serial number within the number of effective bits to automatically perform acquisition of the ONU serial number and ONU connection. An ONU automatic connection method for an ATM-PON system is provided by which an ONU serial number is searched efficiently without registering the ONU serial number from OpS to OLT.

Owner:HITACHI LTD

Power optimized ADC for wireless transceivers

ActiveUS7982651B1Reduce power consumptionIncrease powerPower saving provisionsElectric signal transmission systemsWireless transceiverRadio reception

Owner:MAXLINEAR ASIA SINGAPORE PTE LTD

Ramp linearization for FMCW radar using digital down-conversion of a sampled VCO signal

InactiveUS7737885B2Electrical apparatusRadio wave reradiation/reflectionRadar systemsDigital down conversion

The invention relates to an FMCW radar system and a method of operating an FMCW radar system to produce a linear frequency ramp. The FMCW radar system includes a VCO, a frequency divider coupled to the VCO output, followed by an A / D converter. A down-converter shifts the digitally converted signal to baseband samples, followed by a low-pass filter coupled to an output thereof. A VCO frequency estimator produces instantaneous VCO frequency estimates from phase differences determined from the filtered baseband samples. A D / A converter coupled to an output of the VCO frequency estimator produces an input signal for the VCO to produce therewith a linear VCO frequency ramp. A Δ-Σ modulator is coupled between the VCO frequency estimator and the input of the D / A converter to produce a dithered VCO control signal, thereby increasing the effective number of bits of the D / A converter.

Owner:INFINEON TECH AG

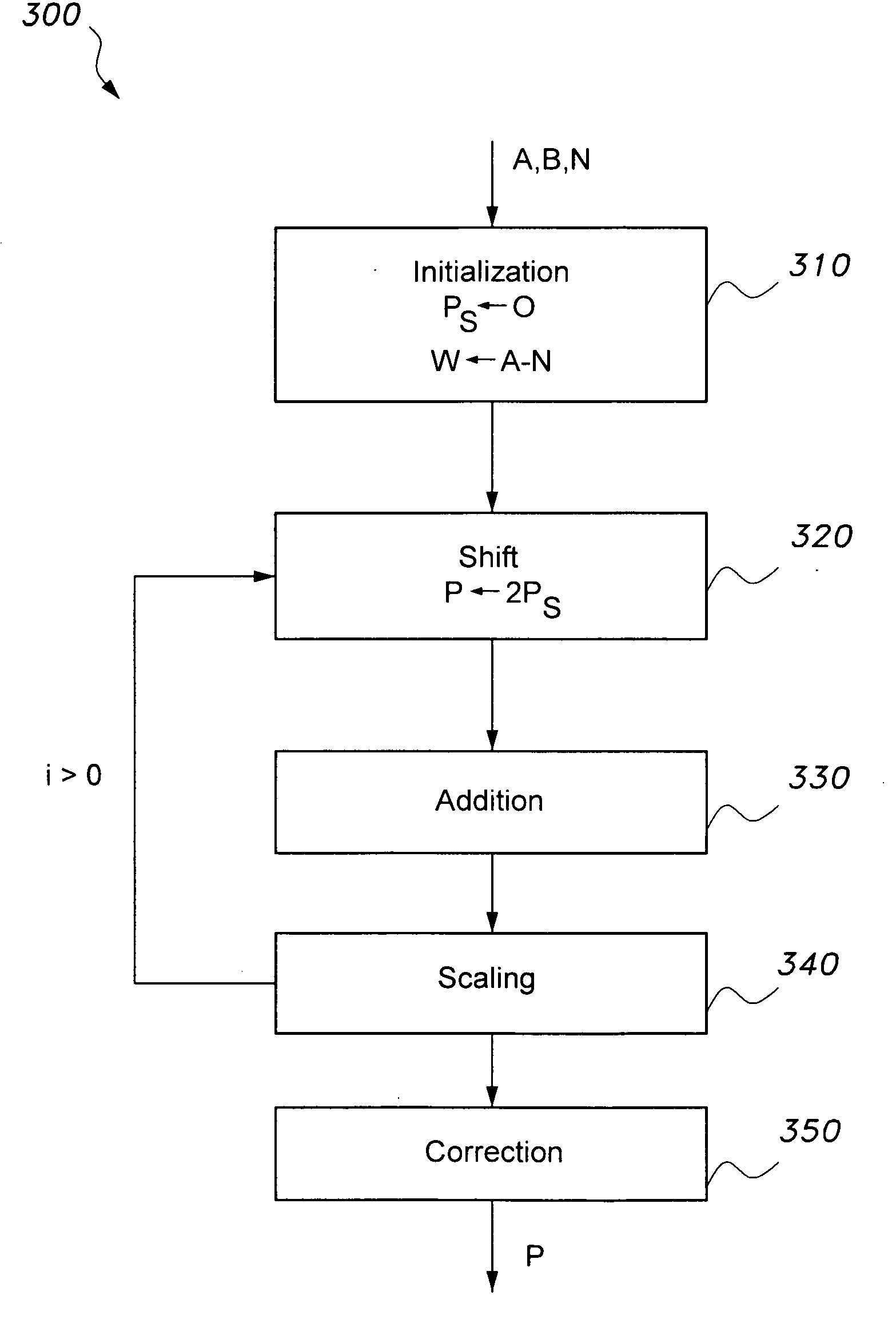

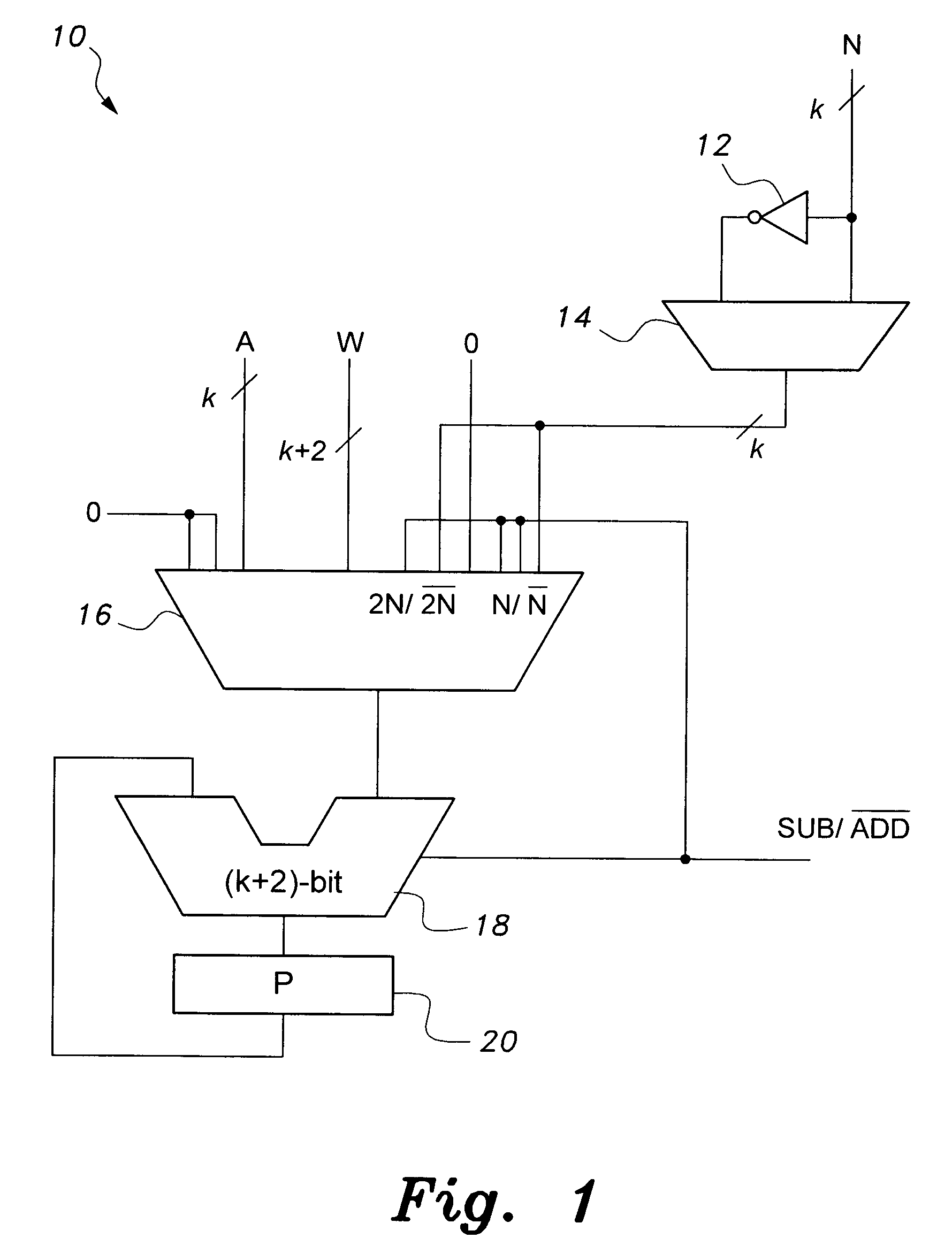

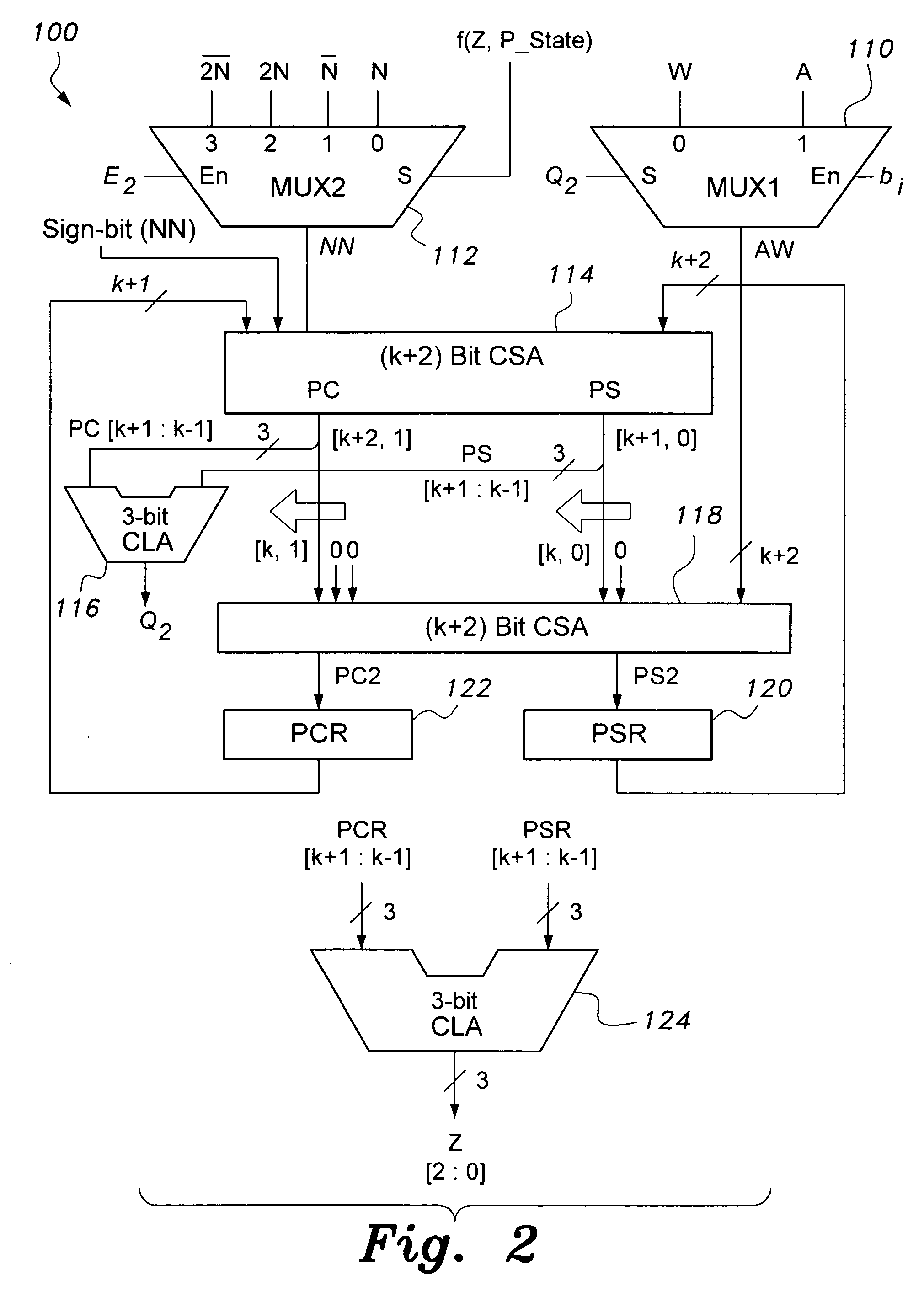

Apparatus and method for high-speed modulo multiplication and division

InactiveUS20080114820A1Increase speedWeakening rangeDigital computer detailsComputations using residue arithmeticHardware implementationsComputer science

The method for high-speed modulo multiplication is a method for multiplying integers A and B modulus N that is optimized for high speed implementation in an electronic device, which may be implemented in software, but is preferably implemented in hardware. The multiplication is performed on devices requiring no more than k+2 bits, where k is the number of significant bits in A, B, and N. The method computes the running product biiAW, where AW is either A when the previous running product is negative, or W when the previous running product is positive, W being the N-conjugate of A formed by A−N. On each iteration, the magnitude of the running product is reduced by a scaling factor no greater than 2N according to the state of the two most significant bits of the running product when carry propagate adders are used.

Owner:KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS

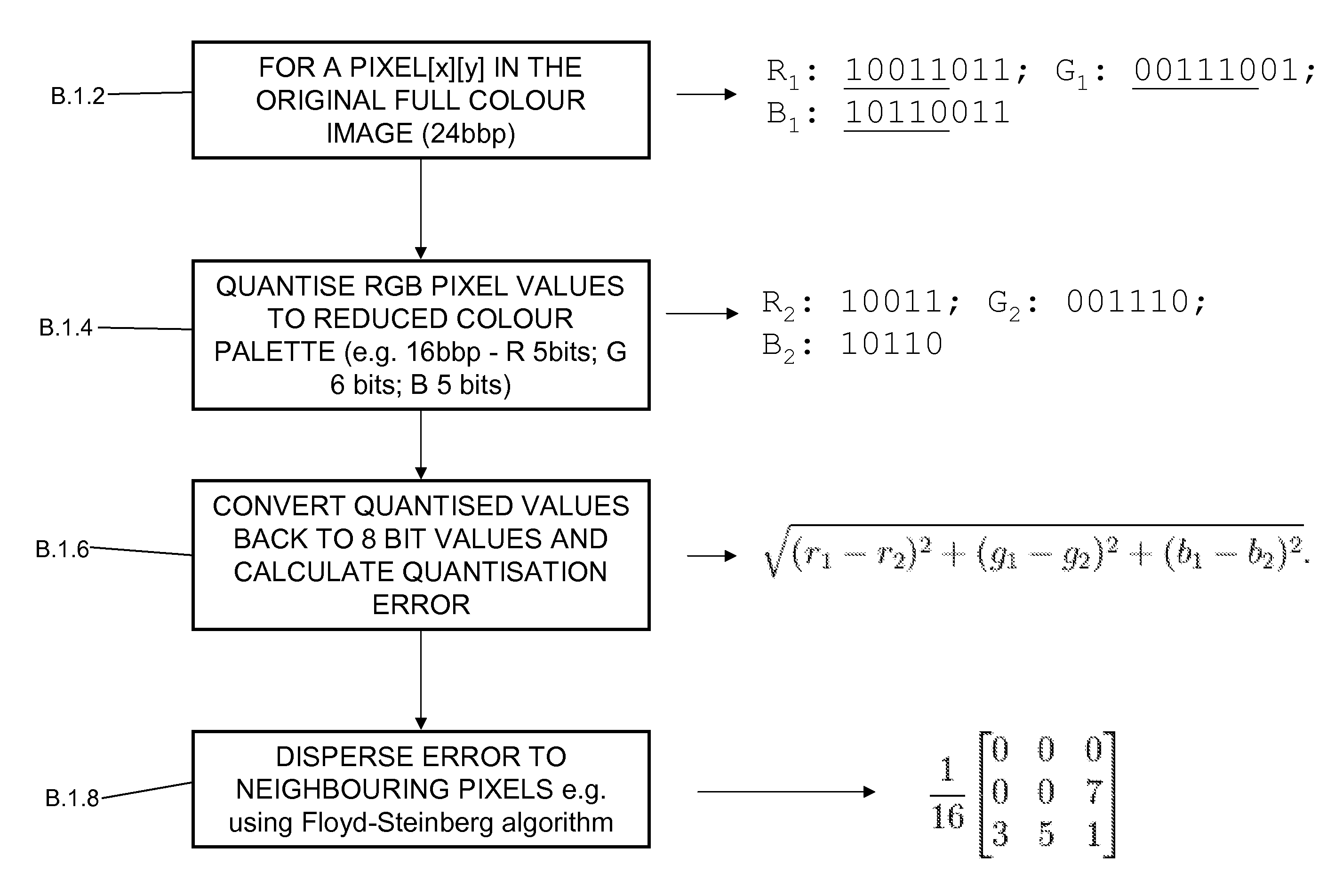

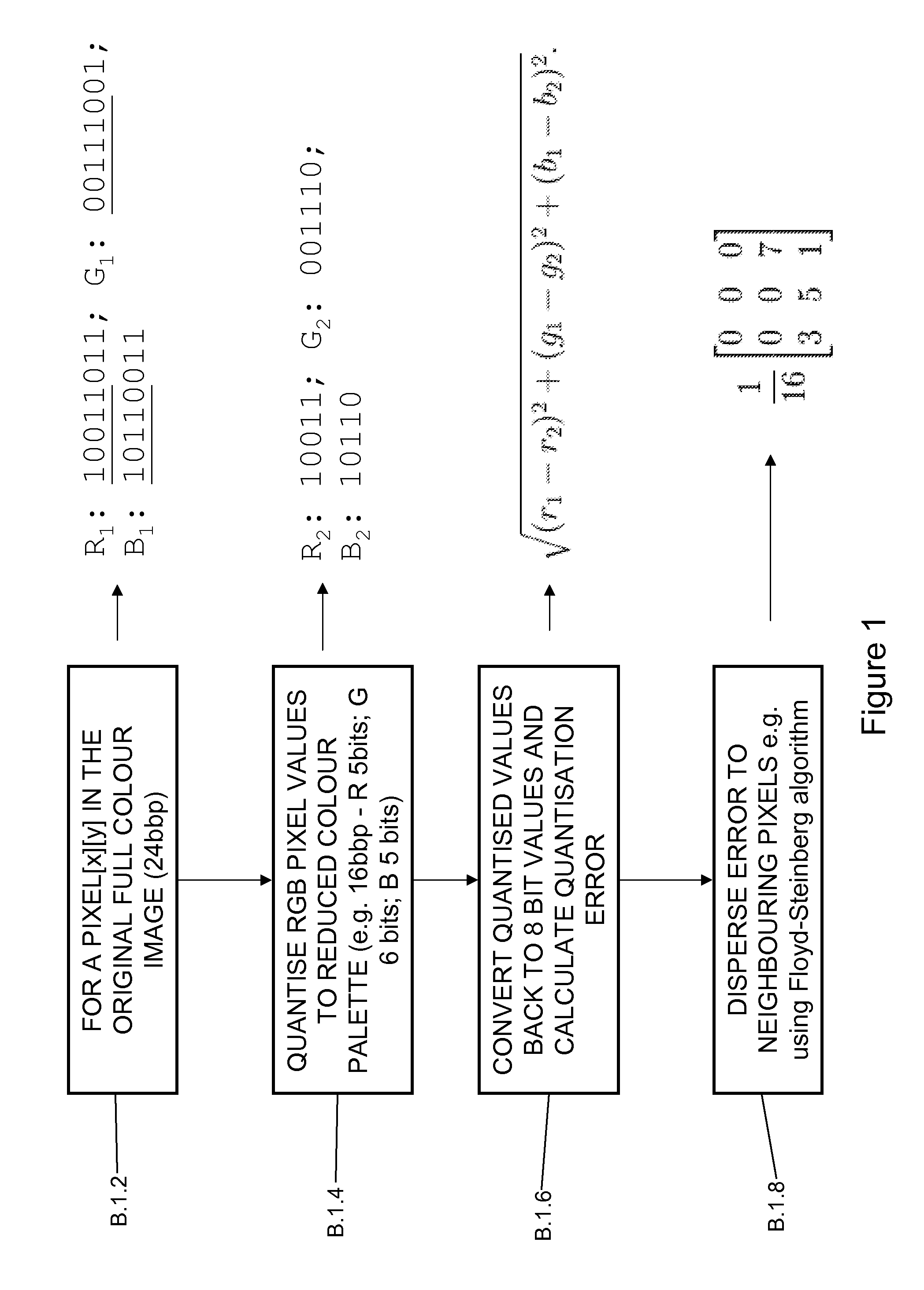

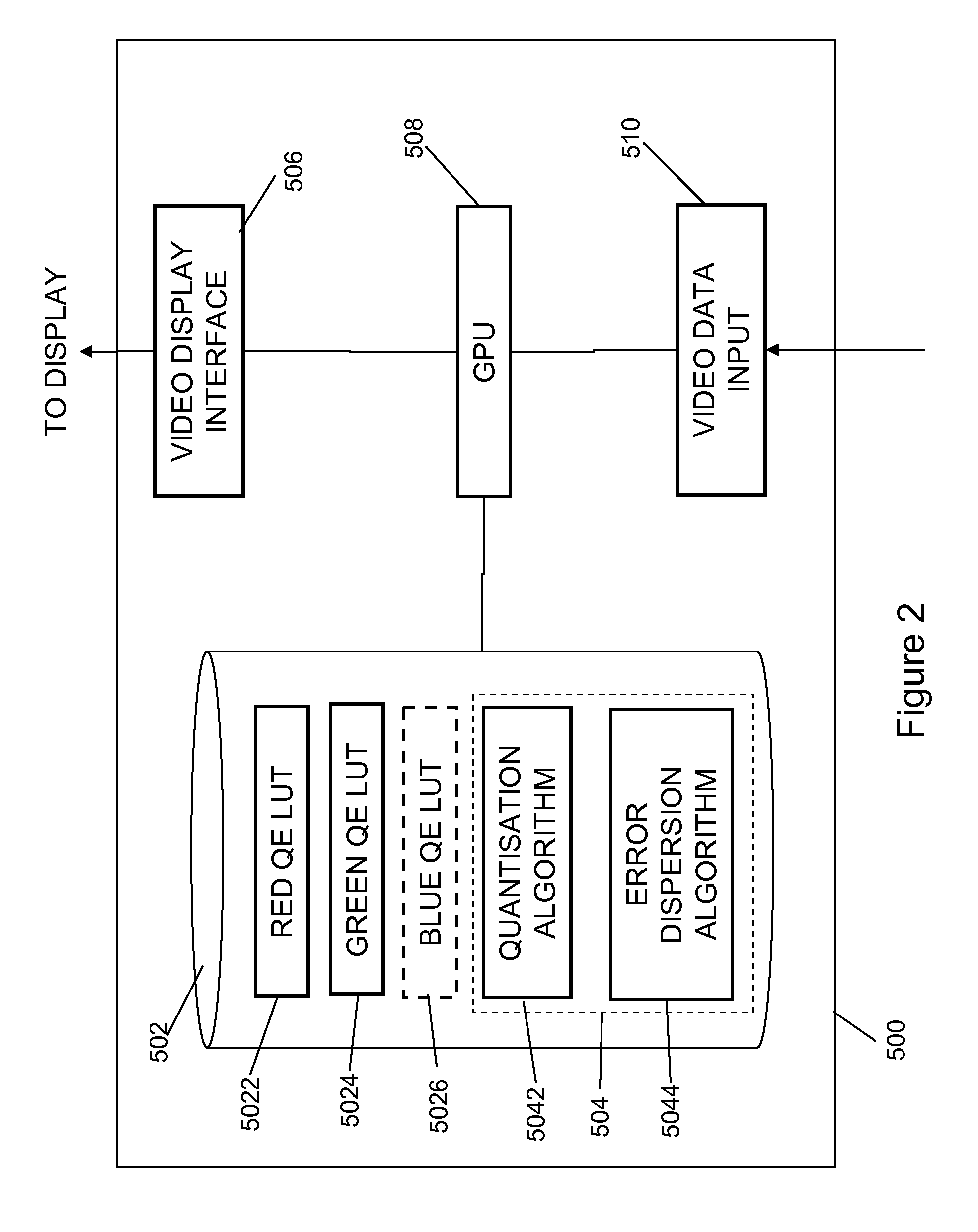

Method and Apparatus for Finding Data Quantisation Error

ActiveUS20130011076A1Reduce in quantityCharacter and pattern recognitionDigital video signal modificationComputer hardwareEffective number of bits

Owner:RPX CORP

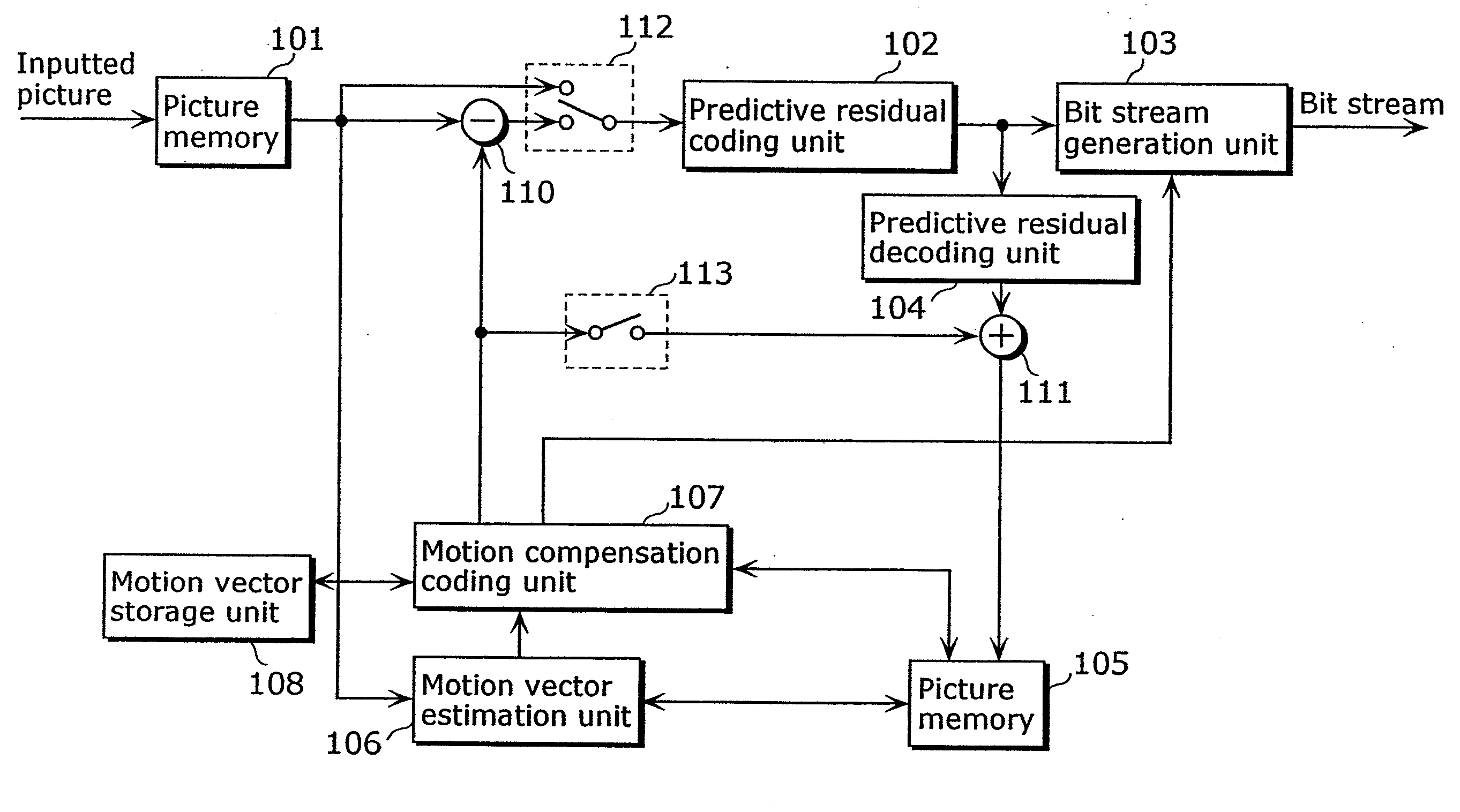

Moving picture prediction method, moving picture coding method and apparatus, and moving picture decoding method and apparatus

InactiveUS20090110072A1Increase the number ofSmall sizeColor television with pulse code modulationColor television with bandwidth reductionDecoding methodsPredictive value

A moving picture prediction method for enabling a calculation amount and a storage capacity to be reduced in a prediction about a moving picture by scaling processing is provided. A method for predicting the value P of Time T from the value P0 of Time T0 and the value P1 of Time T1 includes a step of judging whether it is possible to generate a predictive value with a predetermined significant number of bits by scaling using Time T0, T1 and T (Step S90); a step of predicting the value P from the values P0 and P1 by scaling using Time T0, T1 and T when it is possible to generate a predictive value with the predetermined significant number of bits (Step S92); and a step of predicting the value P from the values P0 and P1 without using Time T0, T1 and T when it is impossible to generate a predictive value with the predetermined significant number of bits (Step S91).

Owner:GK BRIDGE 1

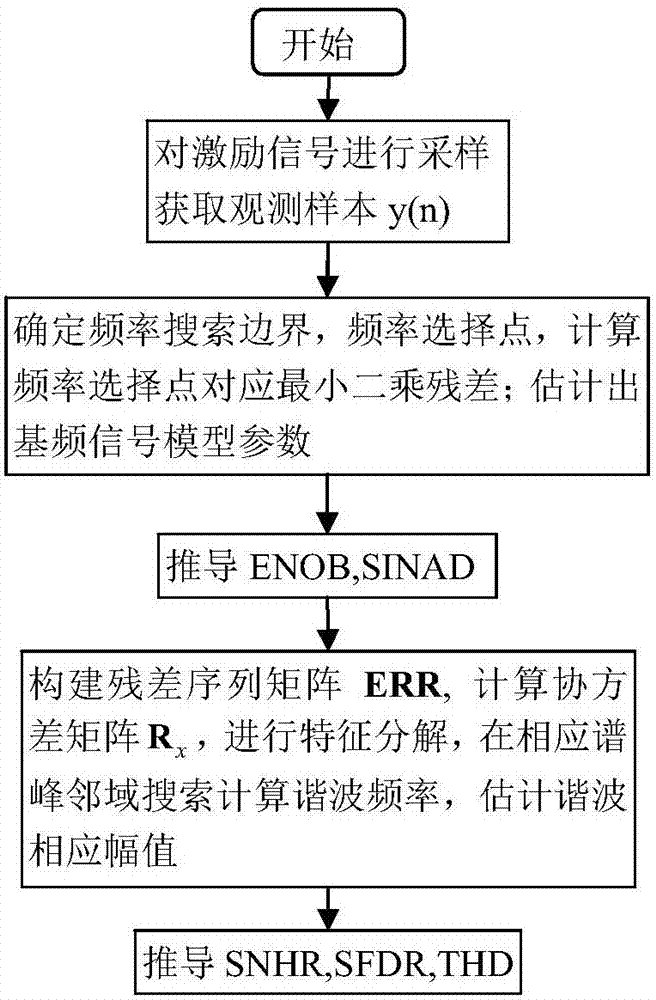

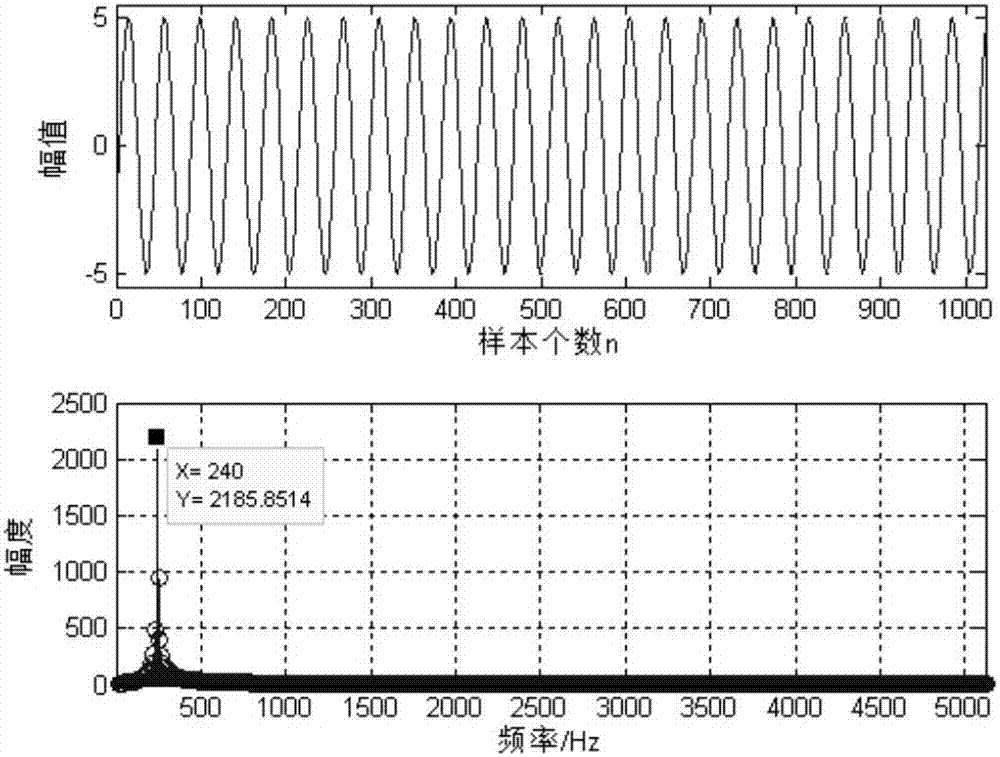

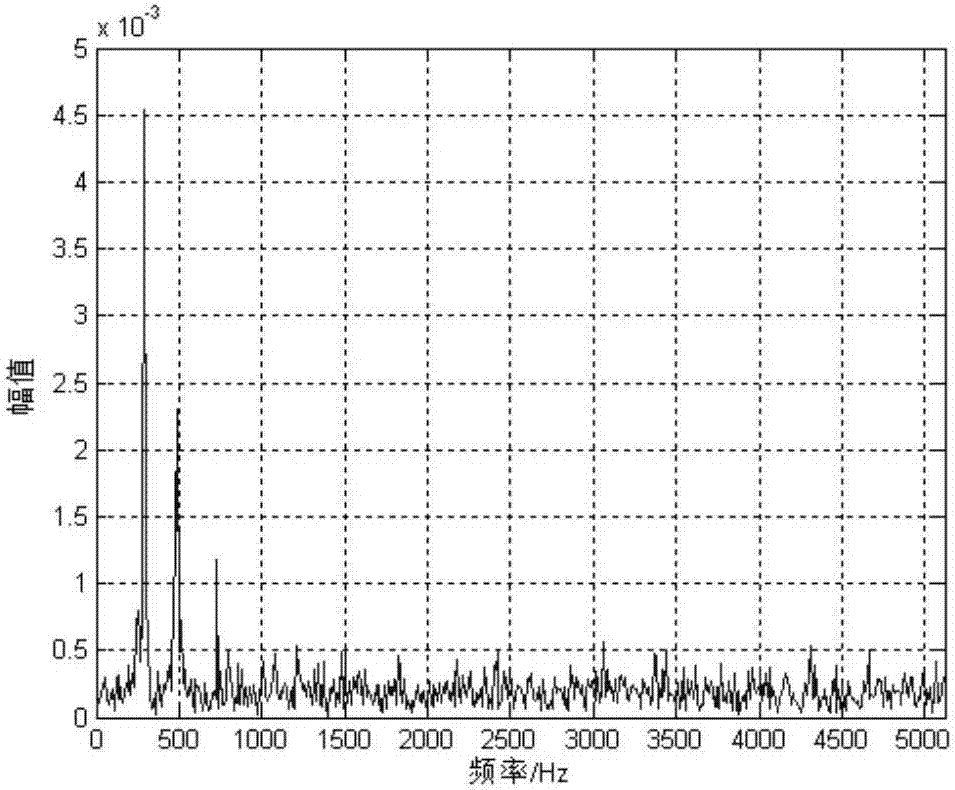

Single ADC acquisition channel dynamic characteristic test method

ActiveCN107102255AHigh frequency resolutionAccurate estimateElectronic circuit testingDecompositionCovariance matrix

A single ADC acquisition channel dynamic characteristic test method belongs to the field of electronic measurement. The test flow comprises steps of sampling the excitation signals to obtain an observation sample; determining the frequency search boundary and the frequency selection point, calculating the least squares residual corresponding to the frequency selection point, and determining the model of the base frequency signal; estimating the signal to noise ratio SINAD and the effective number of bits ENOB; constructing the residual sequence matrix, calculating the covariance matrix, performing the feature decomposition, searching and calculating the harmonic frequency in the neighborhood of the corresponding peak, and estimating the harmonic amplitude; and estimating the signal non-harmonic ratio SNHR, the spurious-free dynamic range SFDR and total harmonic distortion THD. The method firstly adopts a method of combining time-frequency domain analysis and spatial spectrum analysis, can accurately estimate the excitation signal, the noise component and the harmonic distortion component contained in the observation sample, and can effectively improve the spectrum leakage and fence effect in the spectrum analysis. The estimation is highly precise, the calculating amount is small, and the hardware implementation is easy.

Owner:TAIYUAN UNIVERSITY OF SCIENCE AND TECHNOLOGY

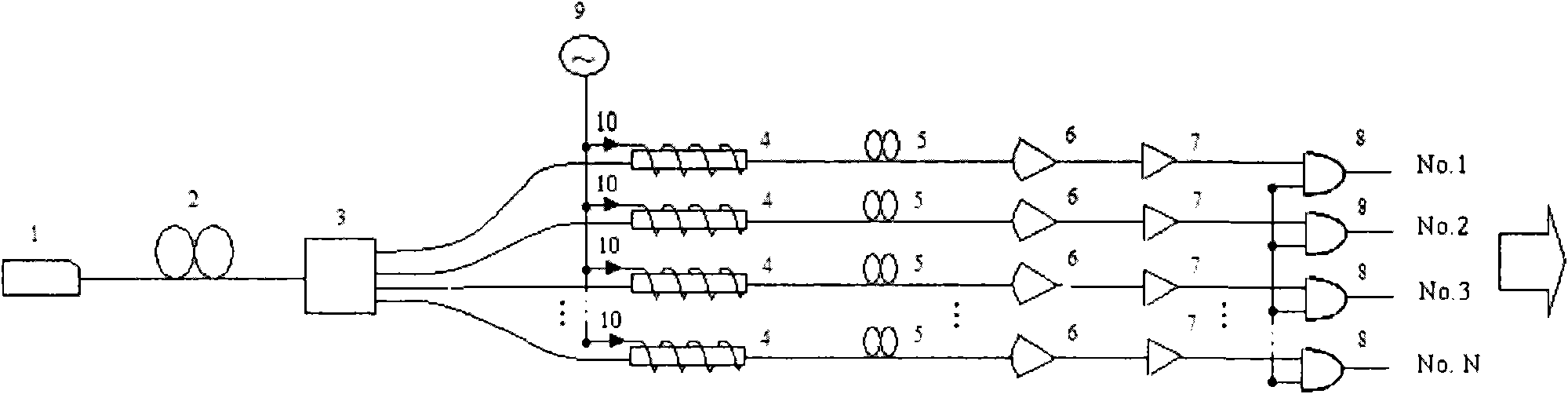

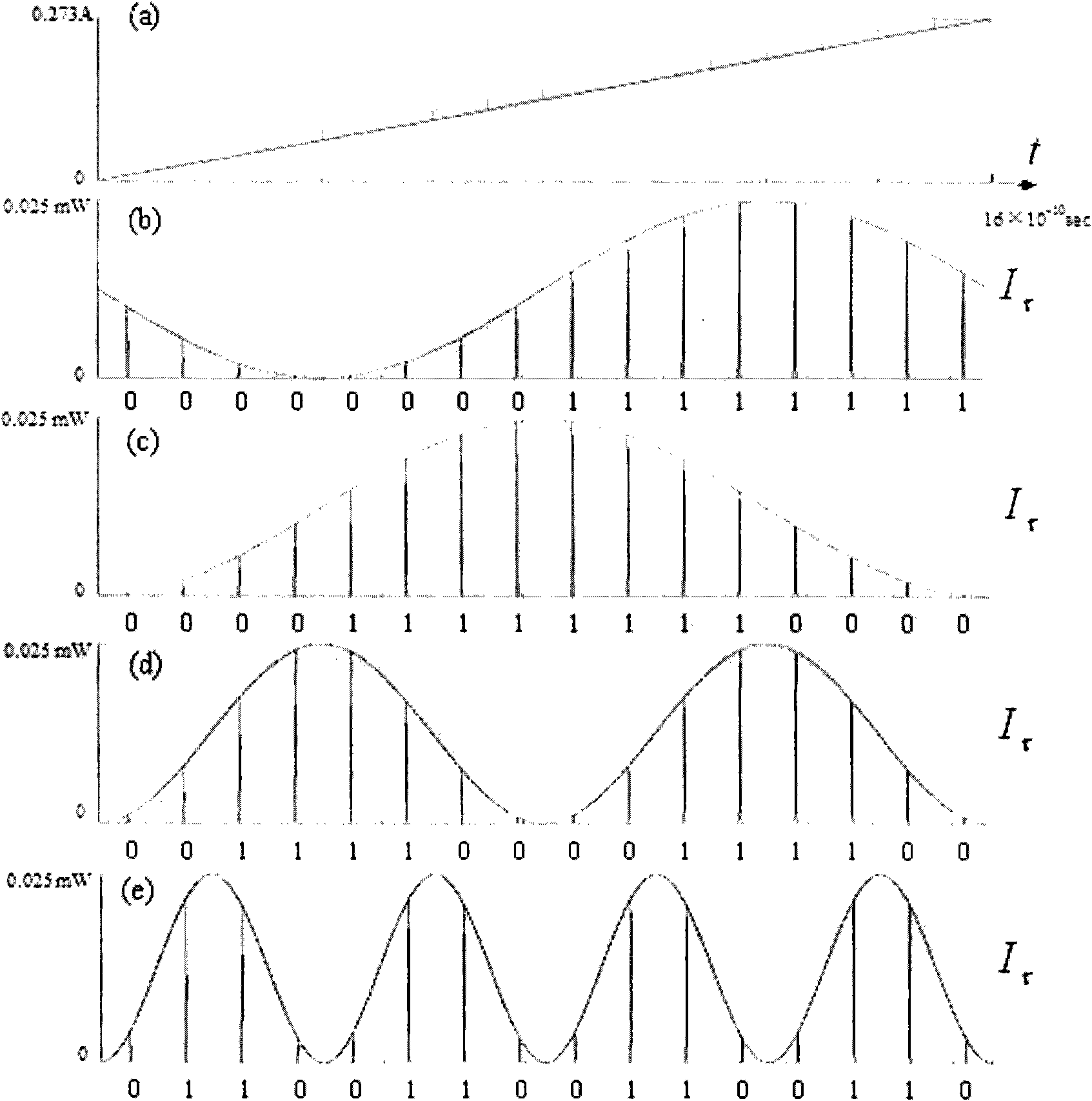

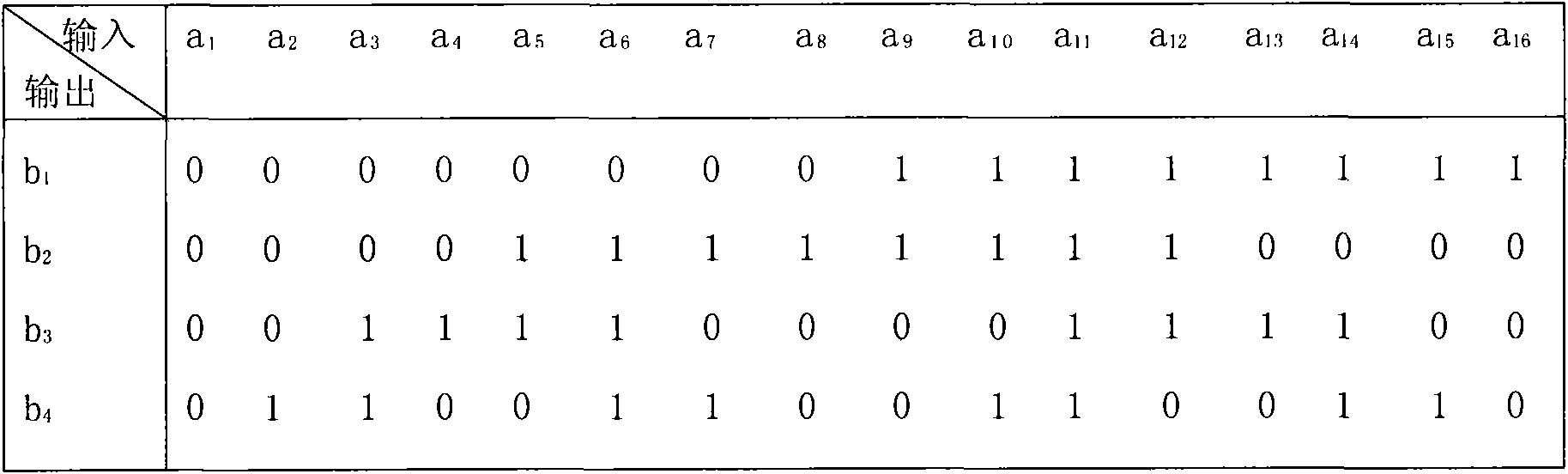

Optical analog-to-digital converter based on polarization modulation

InactiveCN101625501AFast samplingIncrease the number of effective digitsOptical analogue/digital convertersBeam splitterDigital down converter

The invention provides an optical analog-to-digital converter based on polarization modulation, belonging to the field of photoelectric technology, and relates to a photoelectric signal processing and optical analog-to-digital converter. N-path current modulation signals uniformly divided by a sampling analog current signal are respectively input to a magnetic induction coil by an amplifying circuit; pulsed light emitted by a laser is polarized into a linearly polarized light by a polarizer, and the linearly polarized light is divided into N light path signals by a beam splitter, and the N light path signals are respectively input to N photoelectric branch circuits; the optical signal of each photoelectric branch circuit firstly passes through magneto optic effect material in the magnetic induction coil, and then is analyzed by an analyzer into an optical signal which is converted into an electrical signal by a photoelectric detector, the electrical signal is amplified by an amplifier and is input to the corresponding comparer to carry out threshold value judgment, and a digital signal is finally output by the comparer. The converter can realize the output of the digital signal with the traditional binary code and Gray code, and has the advantages of rapid sampling speed, more effective number bits, no restriction of the binary code and the Gray code, simple structure and low cost.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

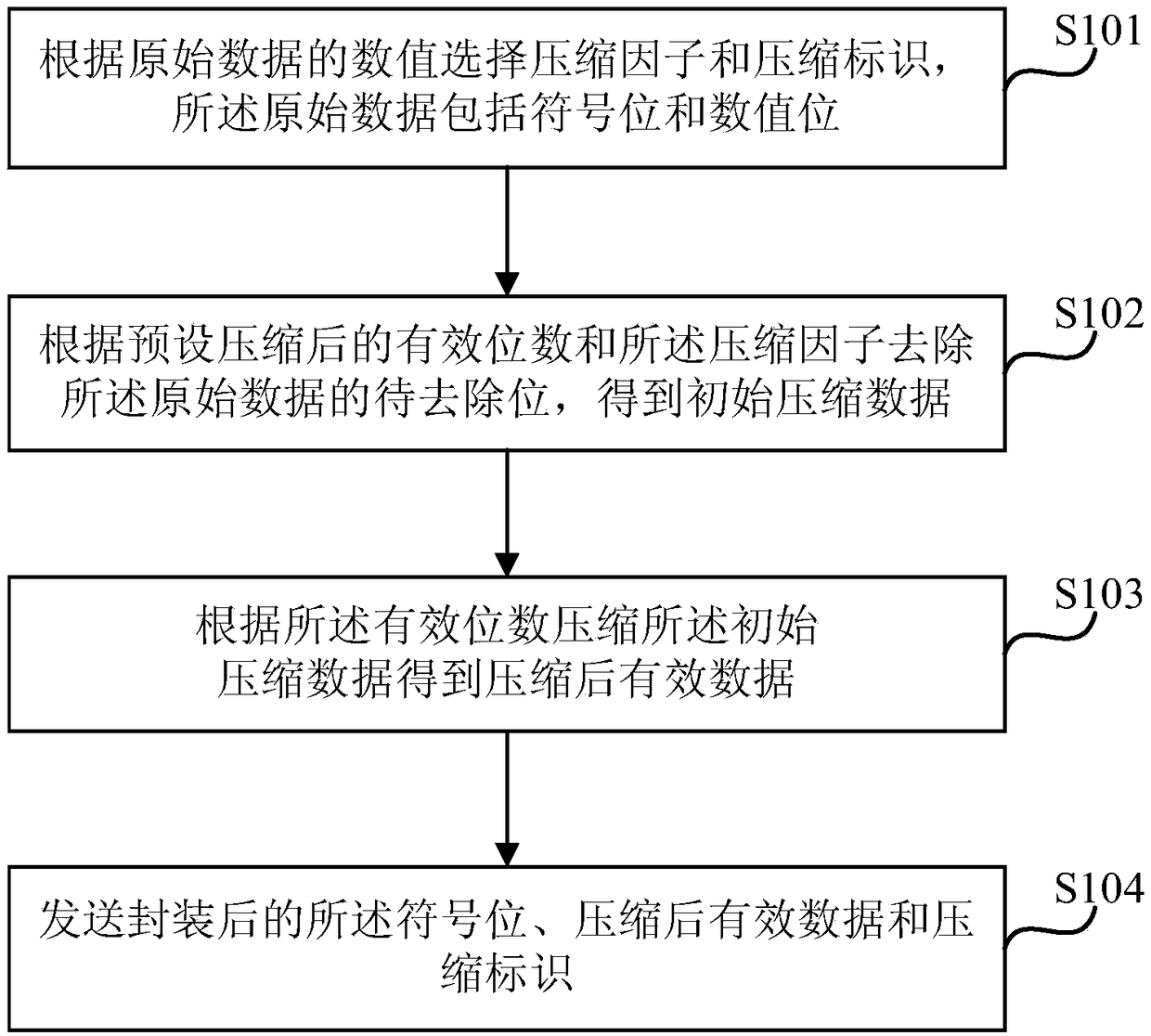

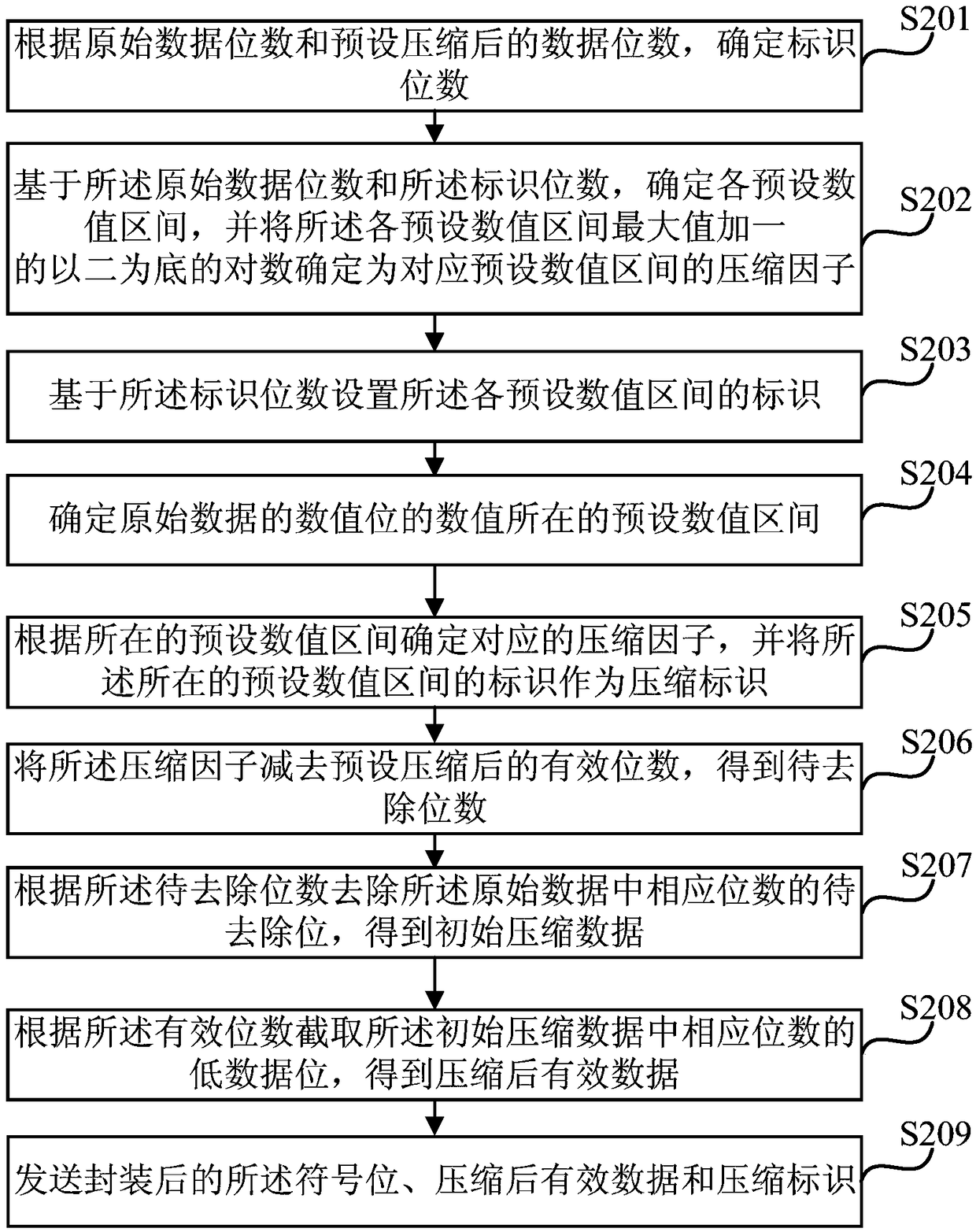

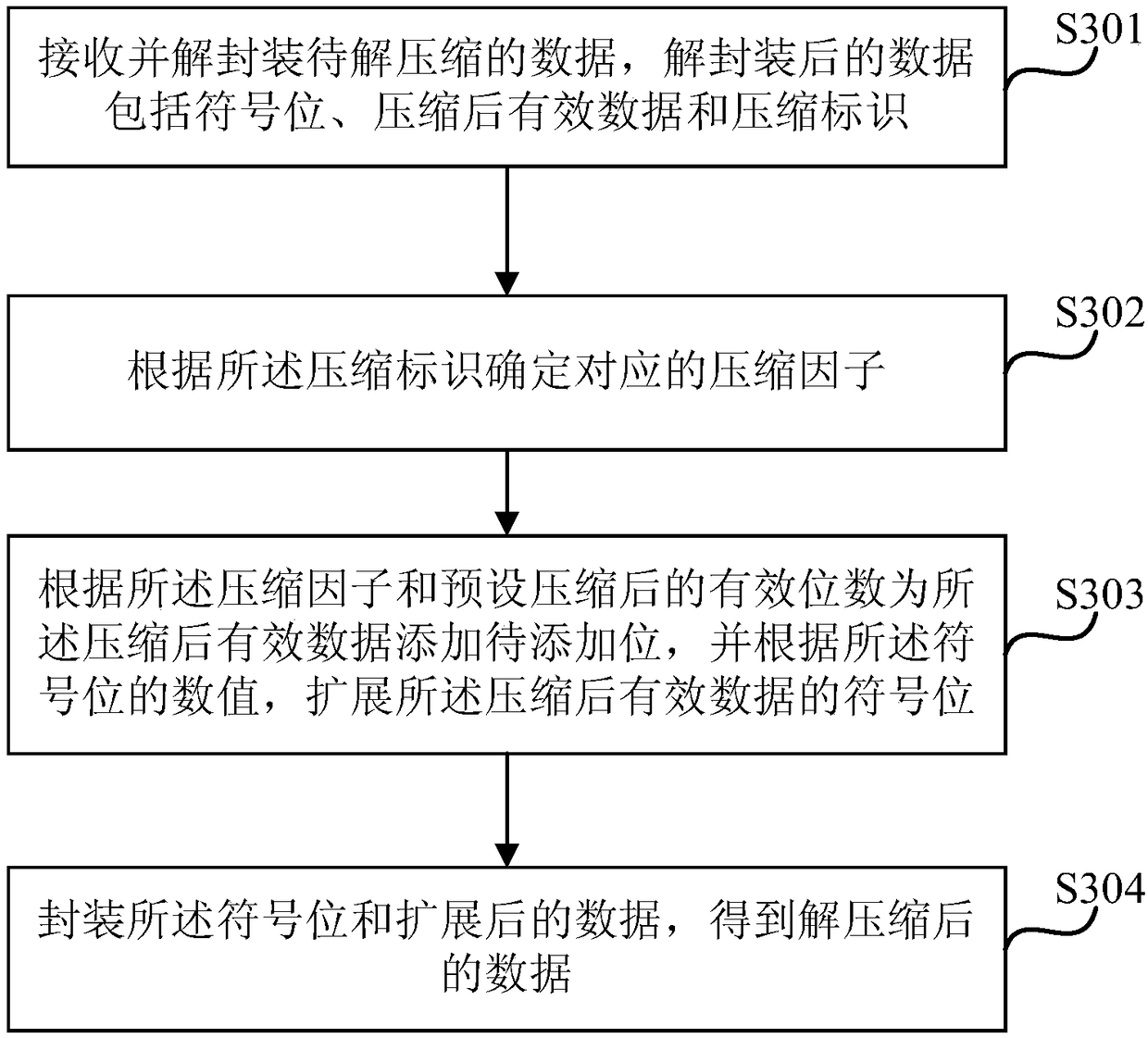

Data transmitting and receiving method and device

ActiveCN108616927AExtended sign bitQuick compressionNetwork traffic/resource managementTransmissionData compressionOriginal data

The invention discloses a data transmitting and receiving method and device. The method comprises the steps that the compression factor and the compression identifier are selected according to the numerical value of the original data, wherein the original data include the sign bit and the numerical bit; the bit to be removed of the original data is removed according to the preset compressed effective number of bits and the compression factor so as to obtain the initial compression data; the initial compression data are compressed according to the effective number of bits so as to obtain the compressed effective data; and the packaged sign bit, the compressed effective data; and the compression identifier are transmitted. With application of the method, the original data can be rapidly compressed so that the problem of excessively high data transmission pressure caused by high transmission data volume can be solved, the data compression time can be effectively reduced, implementation issimpler, resource occupation is low and the data transmission form is simple and feasible.

Owner:RUN TECH CO LTD BEIJING

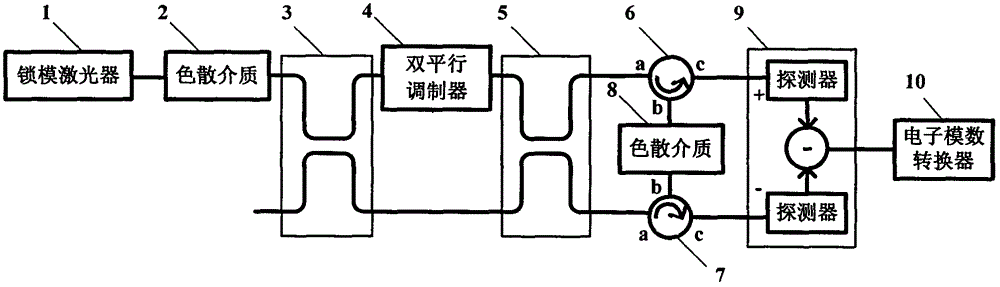

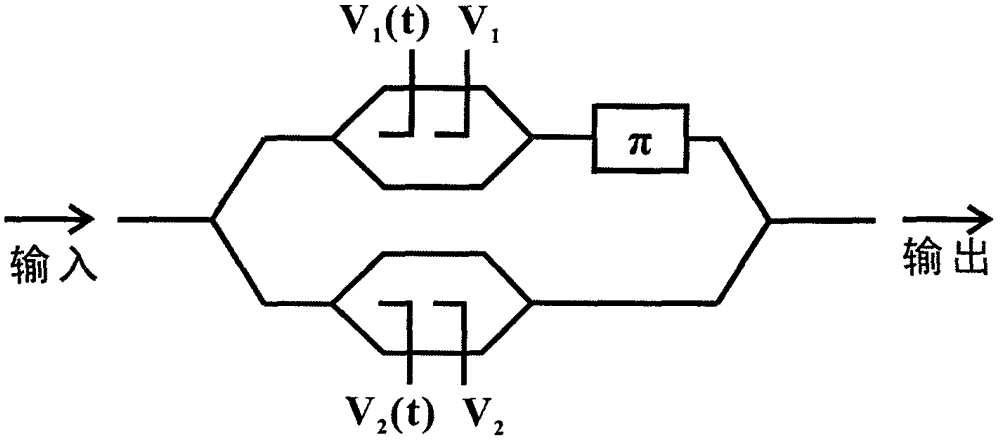

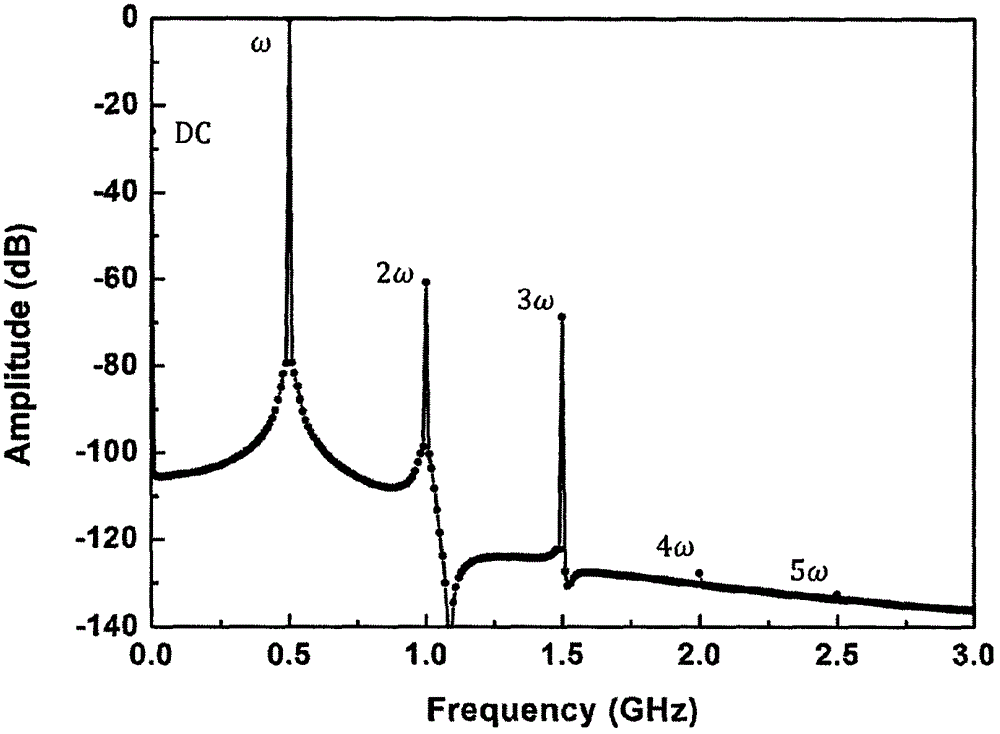

Method and device improving microwave signal time stretching linearity

InactiveCN105842952ASuppress optical carrierSuppression of even harmonic distortion termsOptical analogue/digital convertersCarrier signalLinearity

The invention belongs to the field of optoelectronic technology, and in particular relates to a method and a device for improving the linearity of microwave signal time stretching. The method of the invention utilizes the carrier suppression modulation of the double parallel modulator to realize the suppression of the DC component of the output signal, increases the sensitivity of the detector, effectively eliminates the even-order harmonic distortion, and improves the linearity of the system. By setting the optimal optical power coupling ratio and microwave signal power coupling ratio of the dual parallel modulators, combined with the modulation signal and reference signal interference and balanced detection, the third harmonic and third-order intermodulation distortion can be effectively suppressed, and the system can be significantly improved. The signal-to-noise-distortion ratio and effective number of bits are used to realize the linearization of microwave signal time-stretching analog-to-digital conversion systems.

Owner:成都卓力致远科技有限公司

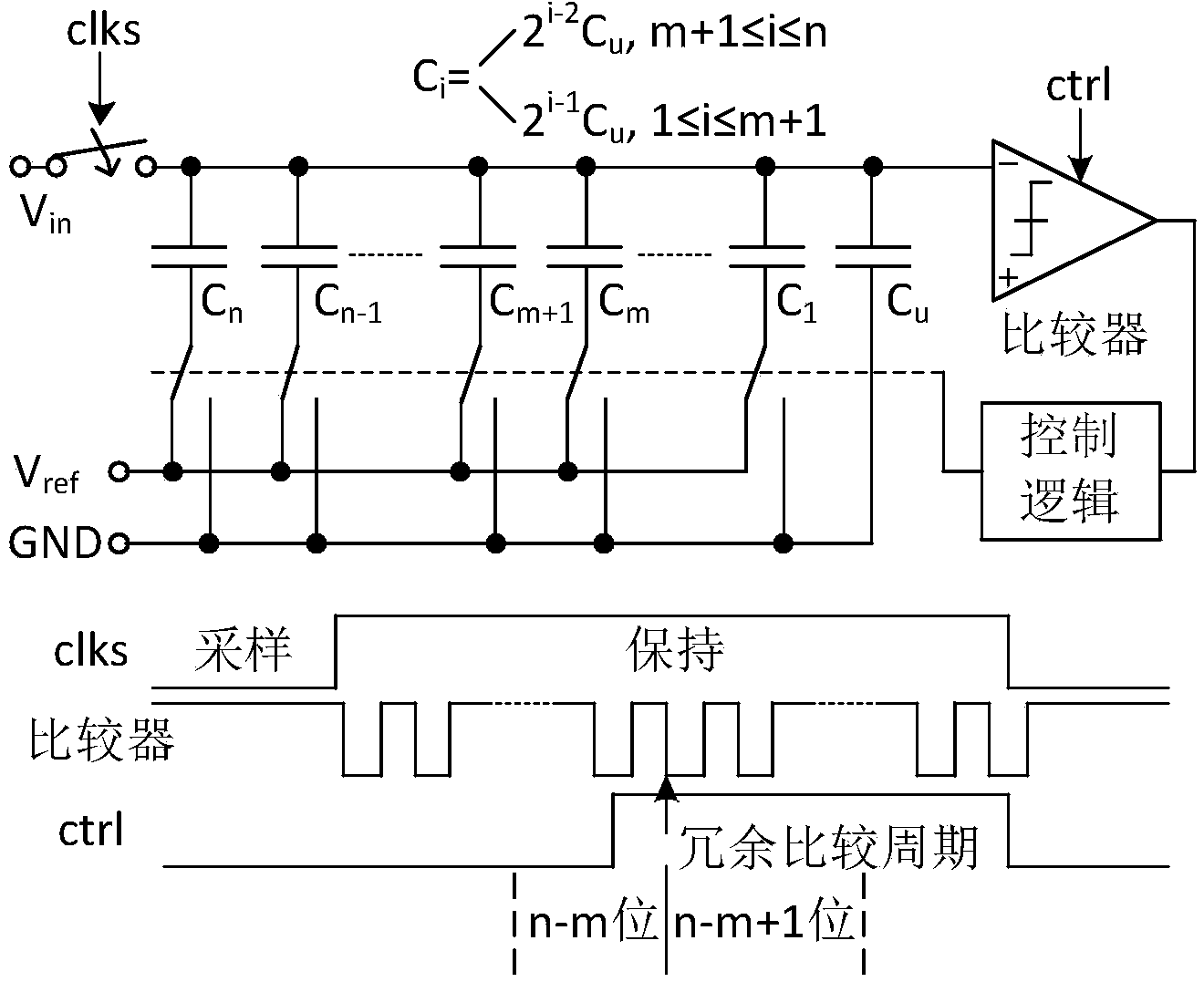

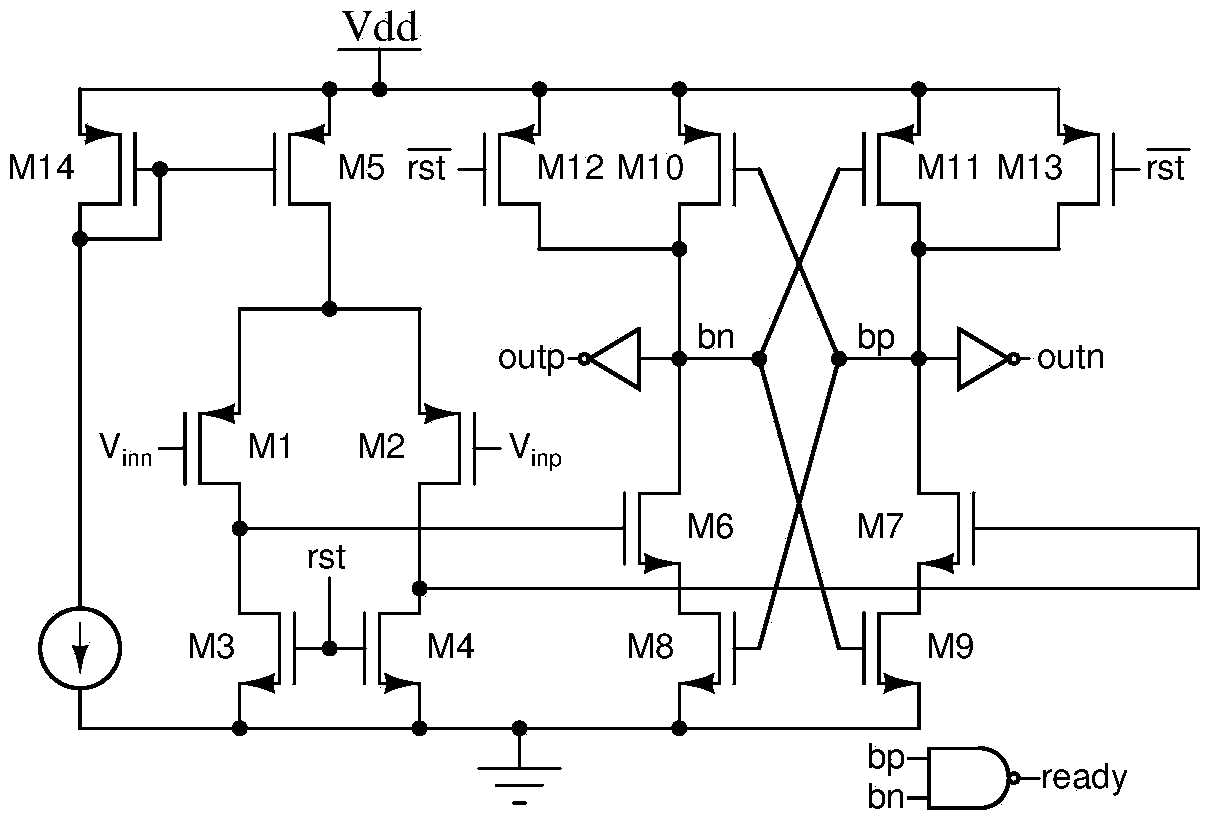

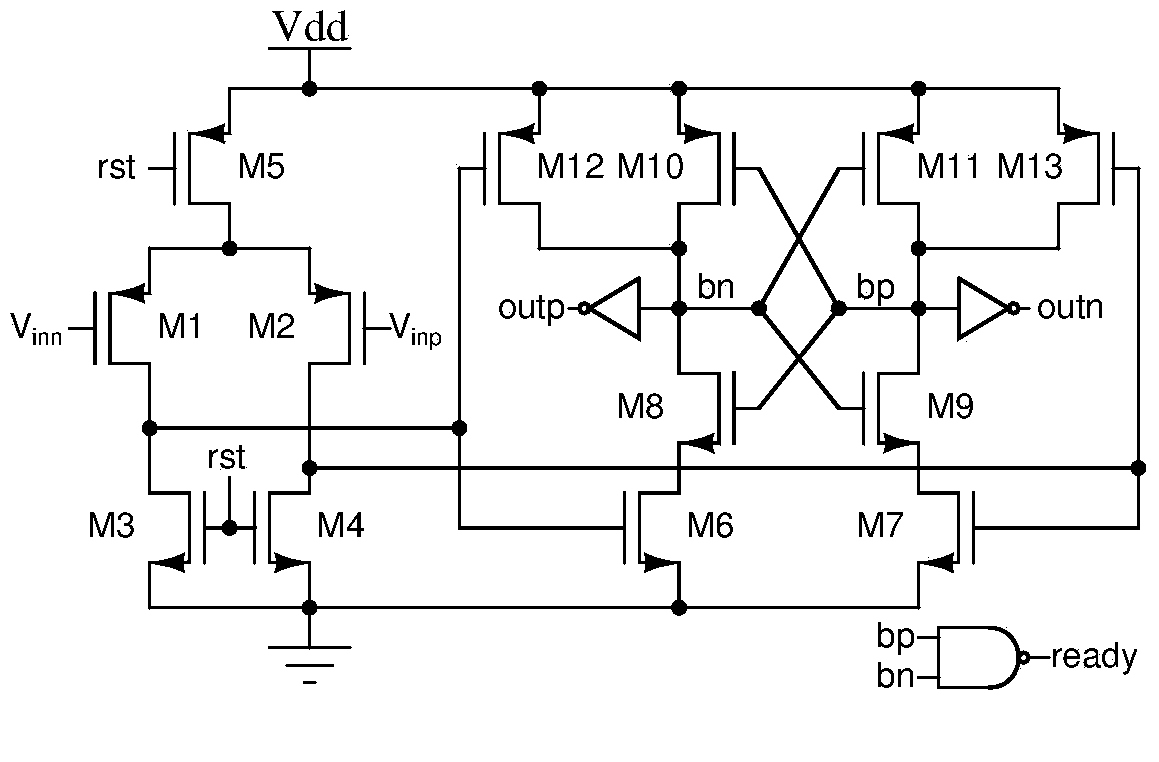

Successive approximation type analog-digital converter for monotonic switching mode

InactiveCN104283563AImprove performanceReduce power consumptionAnalogue/digital conversionElectric signal transmission systemsEngineeringLoad distribution

The invention discloses a successive approximation type analog-digital converter for a monotonic switching mode, belongs to the field of high-speed successive approximation type analog-digital converters, and particularly relates to the field of comparator circuits. The successive approximation type analog-digital converter comprises an electric charge load distribution digital-analog converter, a comparator and a control logic unit. A redundant circuit is added to an electric charge load distribution digital-analog converter in an existing analog-digital converter, and the comparator is detuned and noise is adjusted by adding a tail current source capable of being controlled logically on an existing comparator and adjusting the proportion of tail currents inside different comparison cycles. The successive approximation type analog-digital converter has the advantages of being simple in structure, low in power consumption and high in speed. The 10-digit 100 MS / s verification successive approximation type analog-digital converter designed under the 0.13-micrometer technology can obtain the effective number of bits more than 9.3, the power consumption is only 1.7 mW, and the quality factor can reach 25.7 fJ / conv.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method of manufacturing piezoelectric wafers of saw identification tags

InactiveUS20070001857A1Increase the amount of dataIncrease volumeImpedence networksRecord carriers used with machinesEngineeringAcoustic wave

The invention provides a method of manufacturing piezoelectric wafers of surface acoustic wave (SAW) identification tags. In one embodiment, the method includes: (1) using a master reticle to form, on each of the piezoelectric wafers, wafer-independent patterns that encode digits of a first significance for SAW identification tags; and (2) using different ones of a library of coding reticles to form, on each of the piezoelectric wafers, wafer-dependent patterns that encode digits of a second significance for SAW identification tags.

Owner:RF SAW COMPONENTS INC

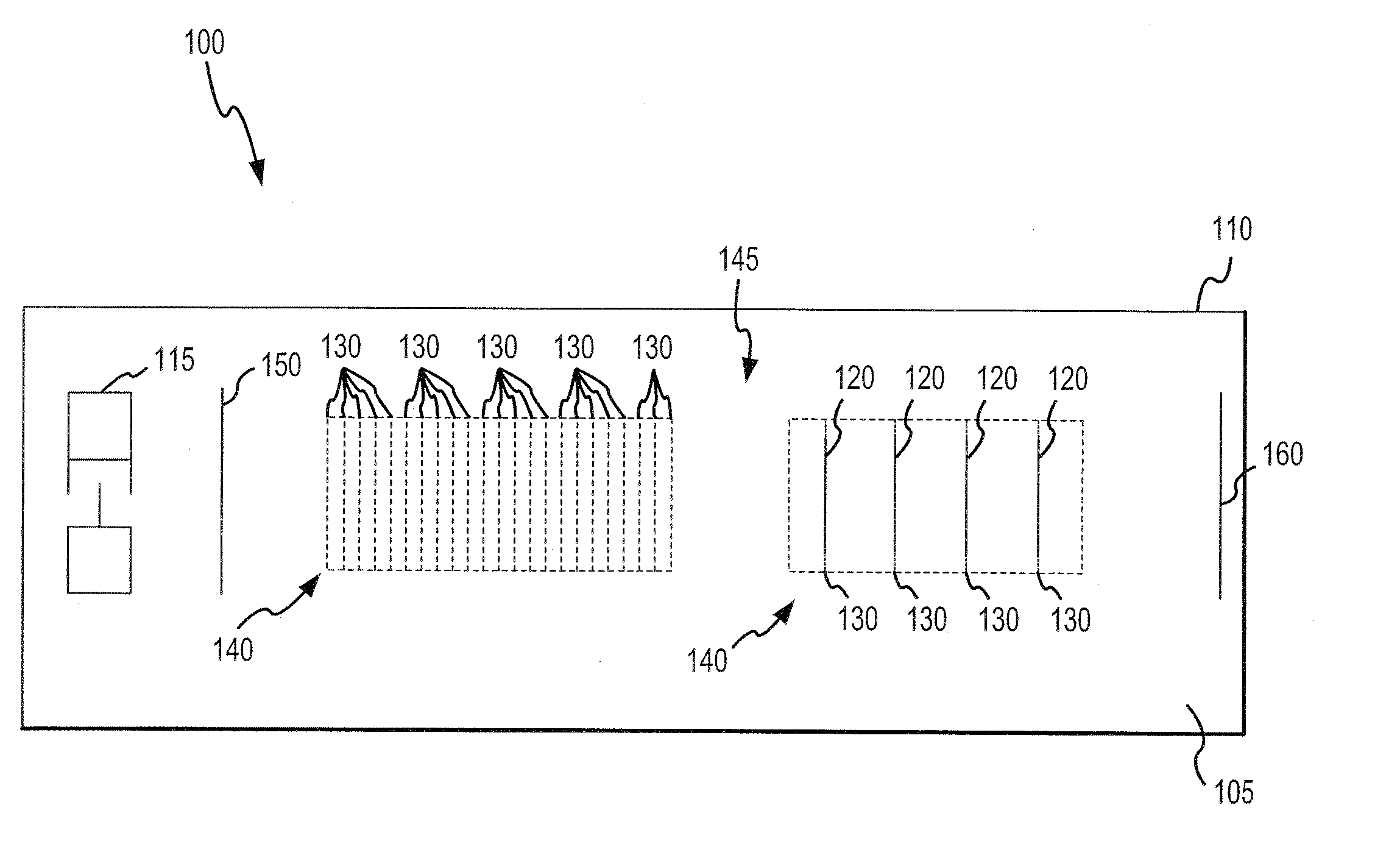

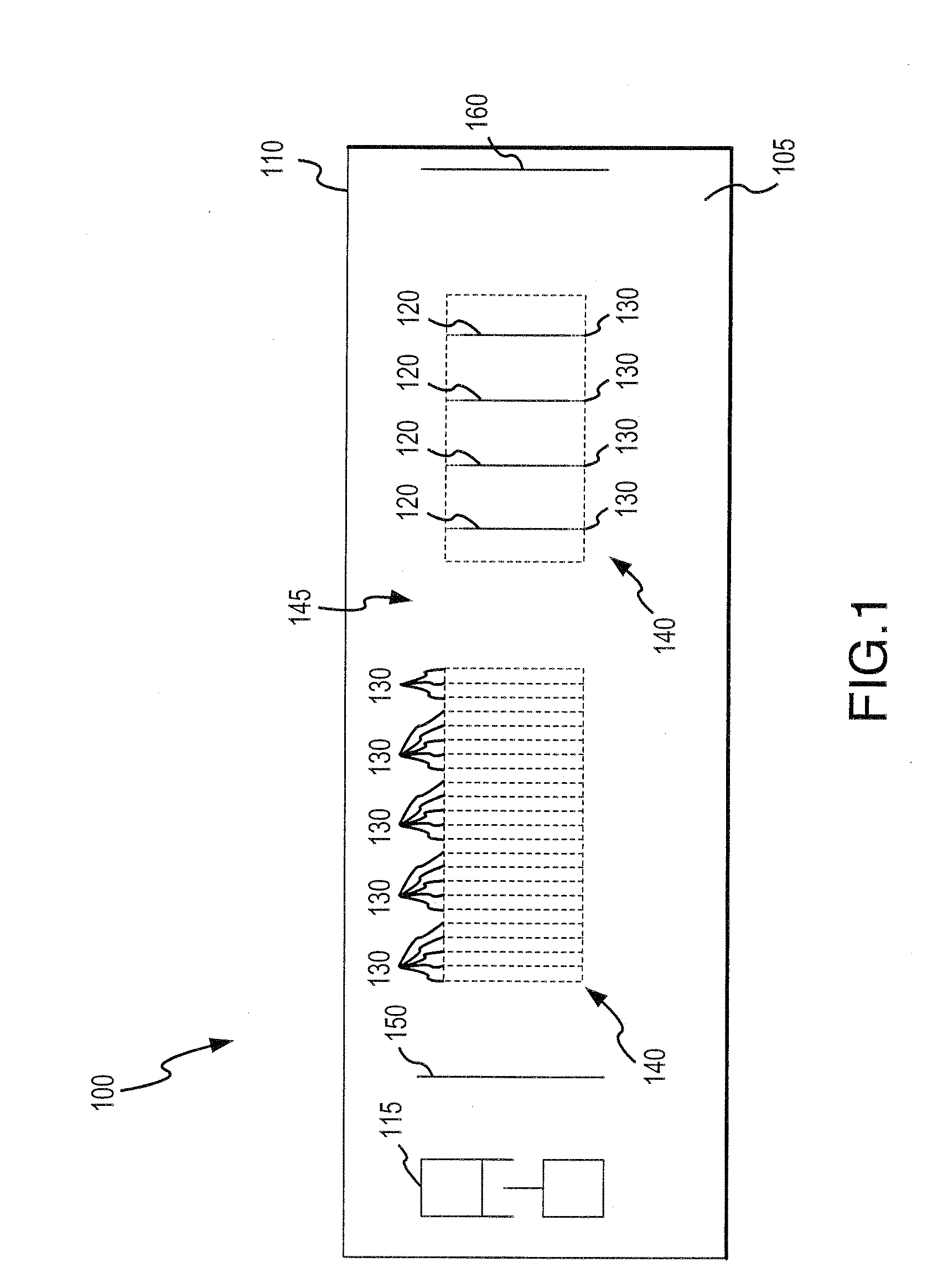

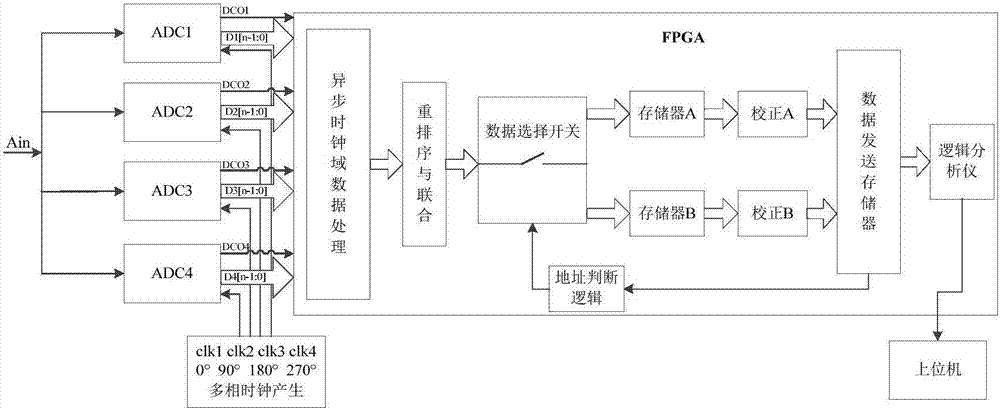

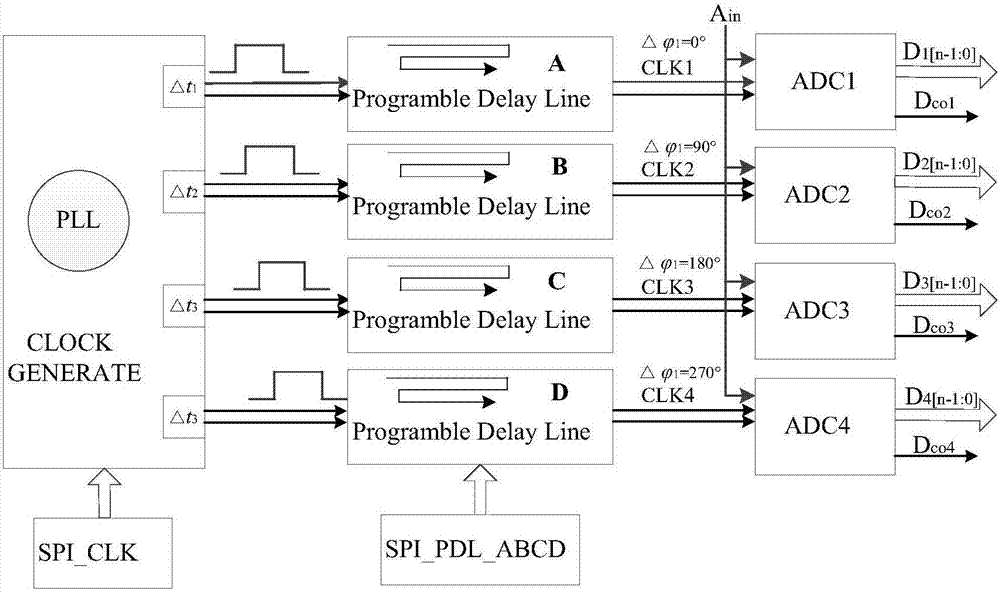

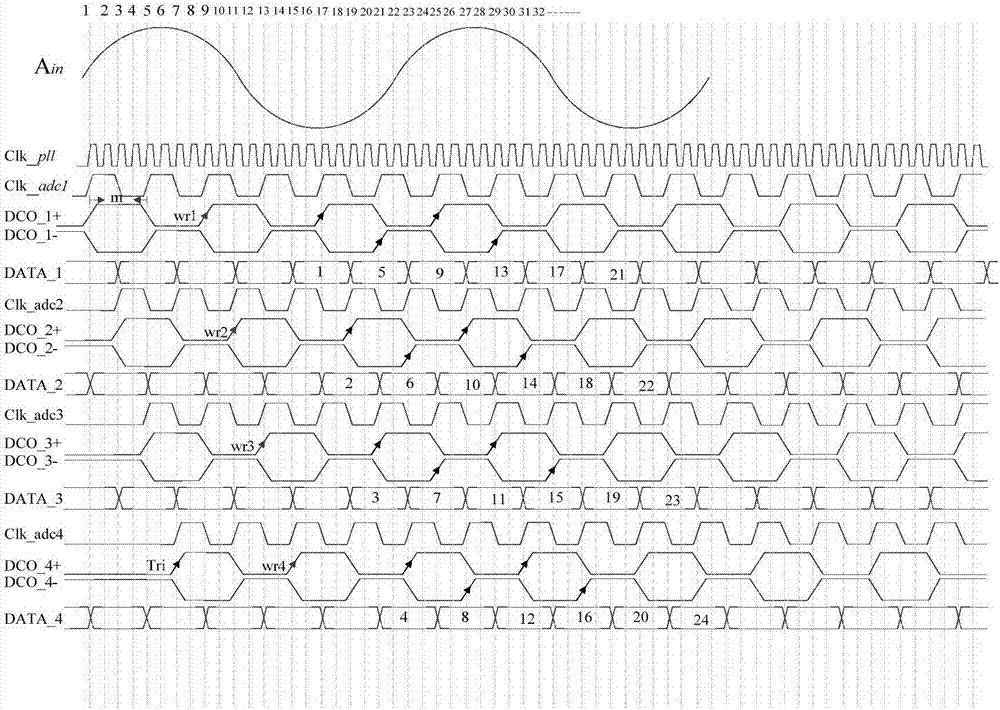

Data caching and reproduction system for time-interleaved analog to digital conversion system

InactiveCN107124185AImprove cache accuracyImprove signal-to-noise ratioAnalogue-digital convertersAnalogue/digital conversion calibration/testingSignal-to-noise ratio (imaging)Time interleaved

The invention provides a data caching and reproduction system for a time-interleaved analog to digital conversion system. According to the system, in order to improve the data caching accuracy, a high-precision time-interleaved ADC multi-phase clock is designed; moreover, internal resources of an FPGA are utilized fully; the integration complexity and hardware cost of the system are reduced; sample data is reasonably stored; digital rear end compensation is carried out on a bias error, a gain error and a time phase error existing in the TIADC system; and finally data is uploaded to an upper computer. According to a test result, a form of an input signal is restored relatively truly, and the performance such as an SNR (Signal to Noise Ratio) and ENOB (Effective Number of Bits) of the TIADC system is effectively improved through digital rear end compensation.

Owner:SUN YAT SEN UNIV +1

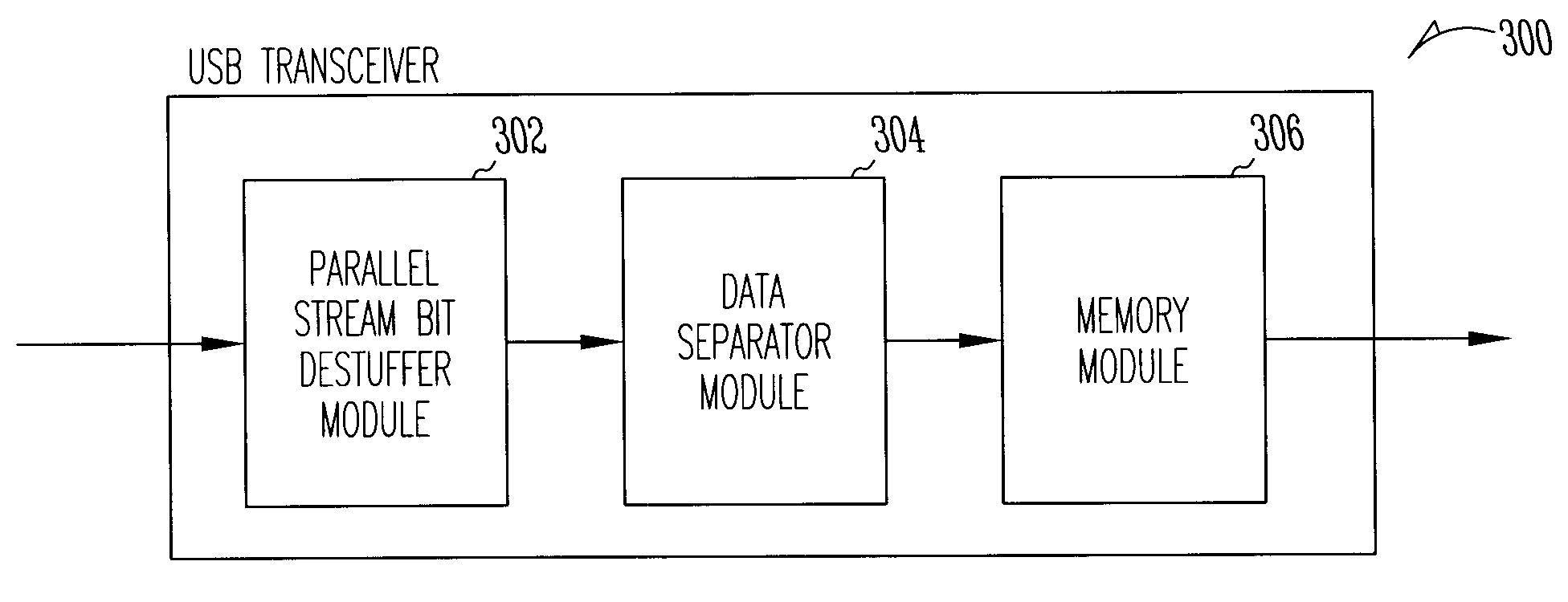

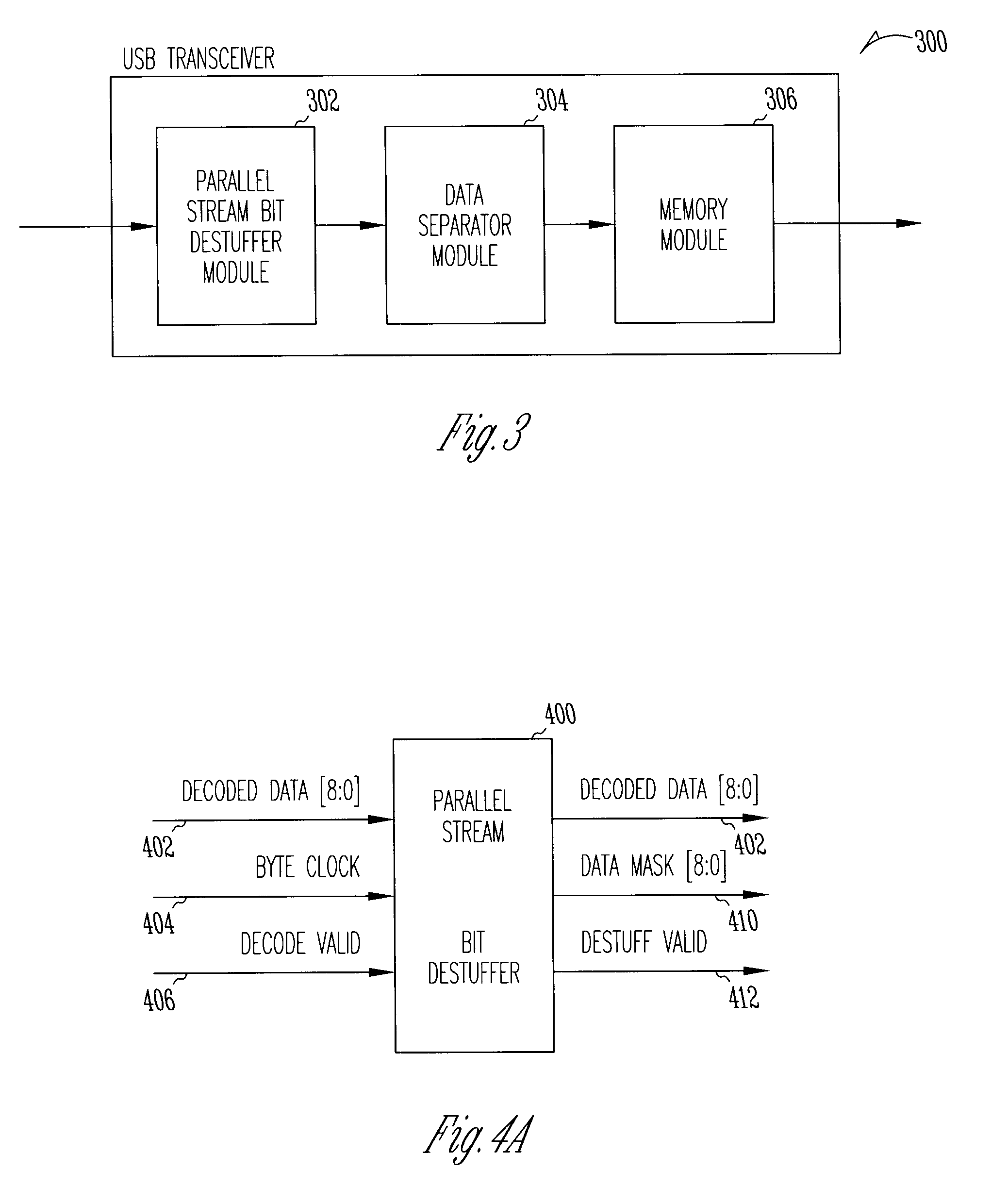

Concurrent asynchronous USB data stream destuffer with variable width bit-wise memory controller

InactiveUS6883047B2Picture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningData streamData transformation

A concurrent asynchronous USB 2.0 data stream destuffer and separator with variable-width bit-wise memory controller is described. A parallel stream bit destuffer module identifies in parallel one or more stuffed bits in a decoded data field of a received data stream using a six-bit sliding window. The stuffed bits are bits that were inserted into the received USB data stream by a transmitter to force data transitions in the received USB data stream. A data separator module separates the one or more stuffed bits from a plurality of valid data bits in the decoded data field. A memory module generates an incremental pointer value representative of the number of valid bits and writes the plurality of valid data bits from the decoded data field into a variable sized bit-wise memory structure.

Owner:INTEL CORP

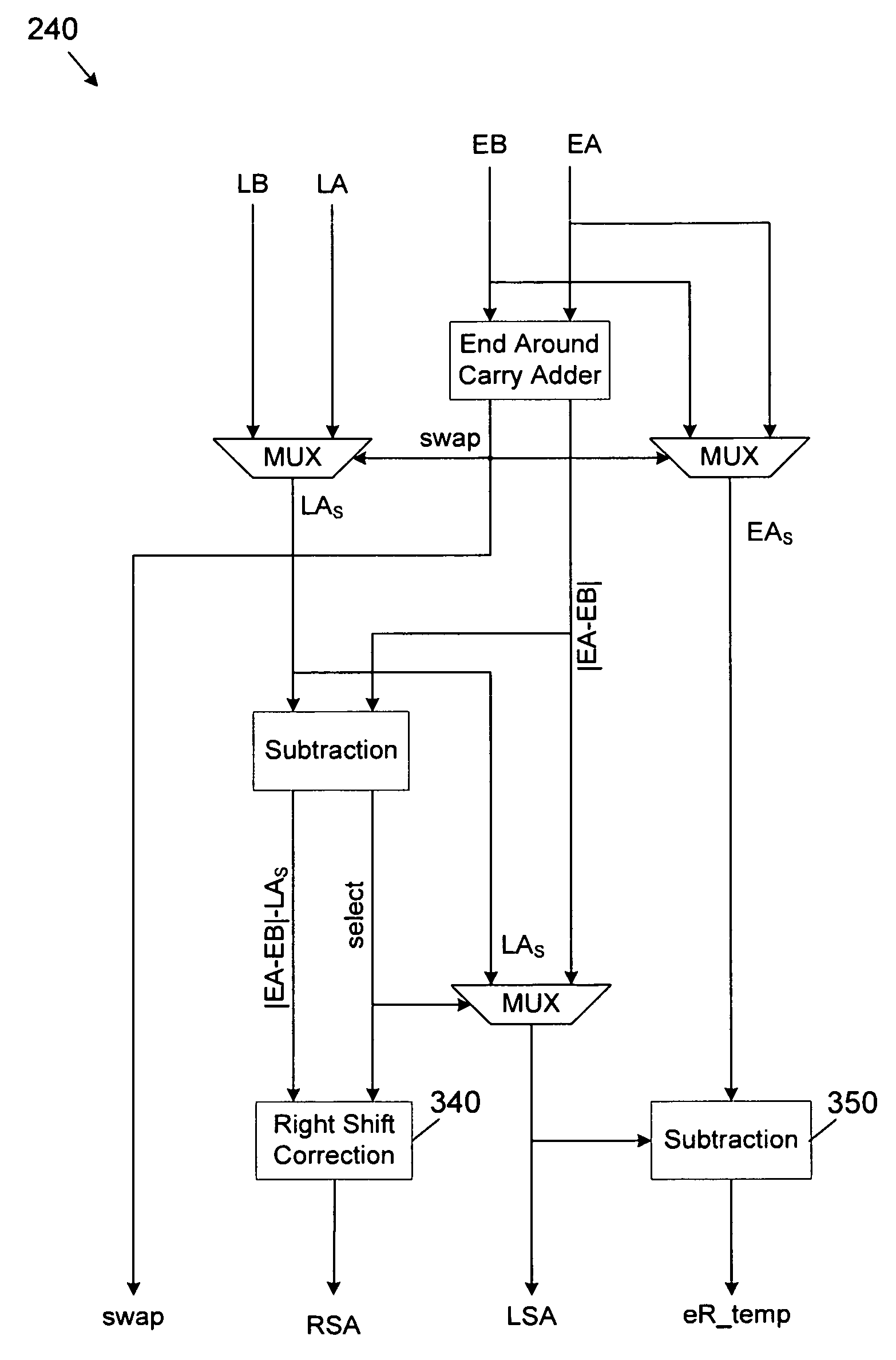

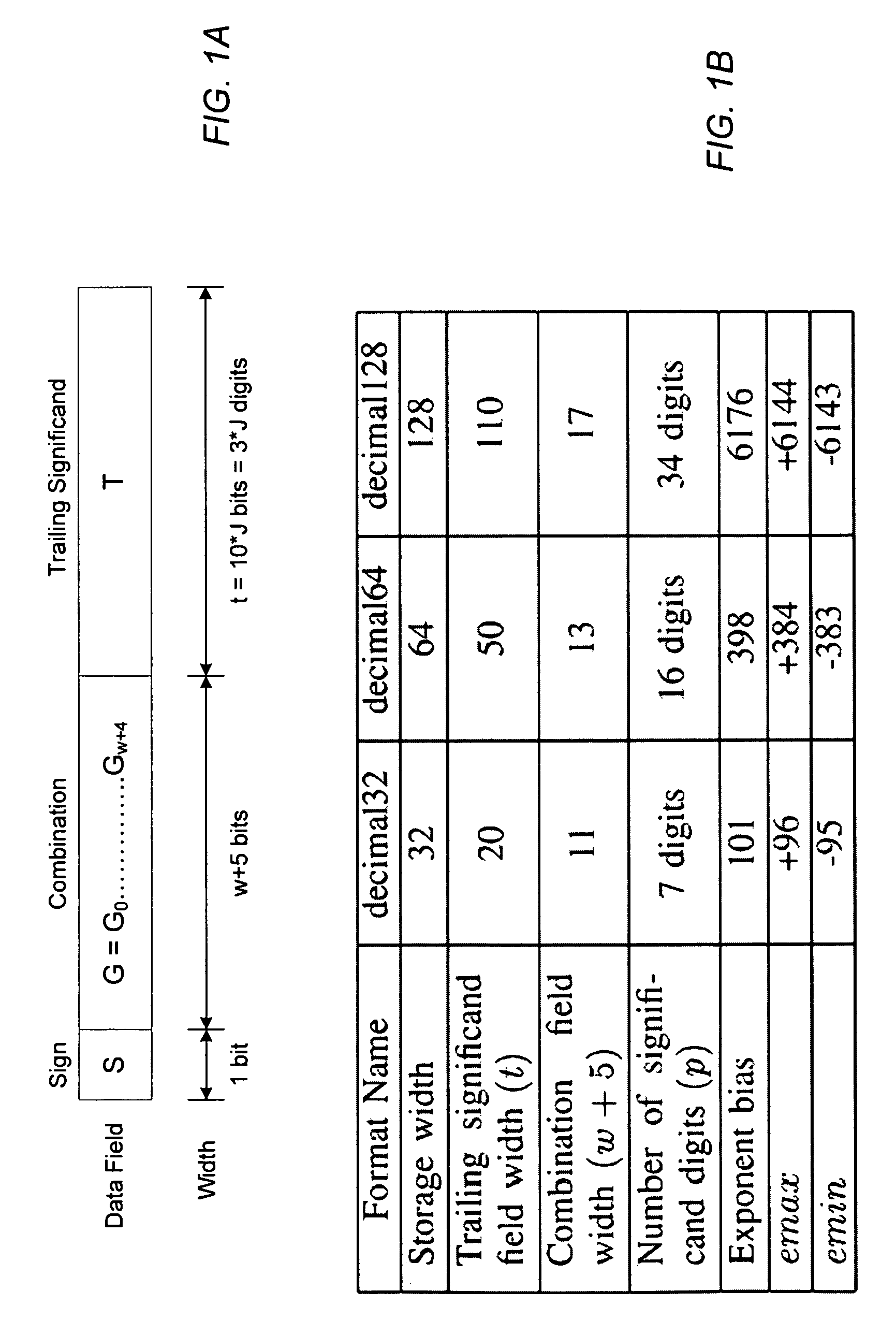

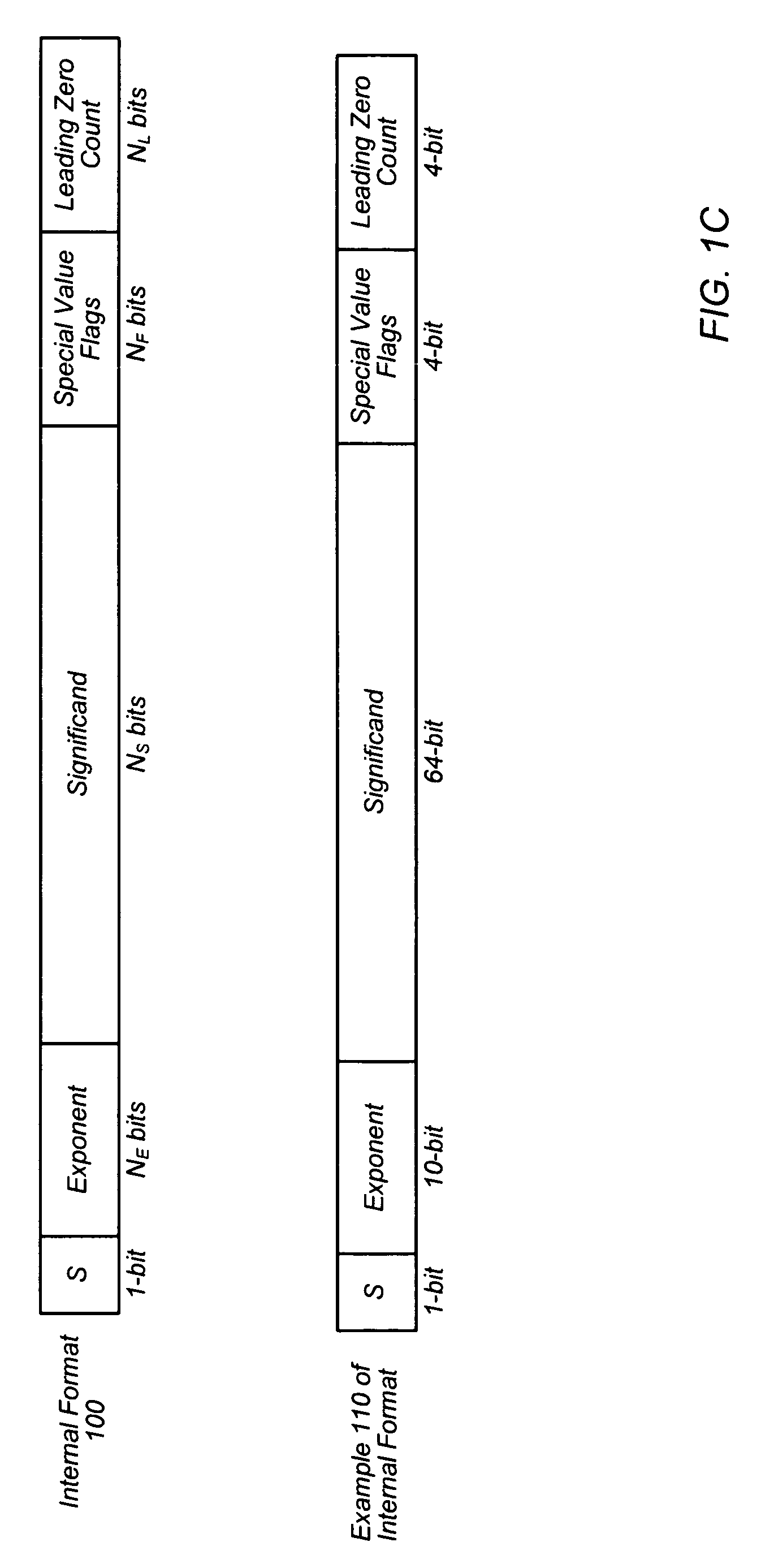

Decimal floating-point adder with leading zero anticipation

ActiveUS8489663B2Computations using contact-making devicesDigital computer detailsOperandLeading zero

A decimal floating-point (DFP) adder includes a decimal leading-zero anticipator (LZA). The DFP adder receives DFP operands. Each operand includes a significand, an exponent, a sign bit and a leading zero count for the significand. The DFP adder adds or subtracts the DFP operands to obtain a DFP result. The LZA determines the leading zero count associated with the significand of the DFP result. The LZA operates at least partially in parallel with circuitry (in the DFP adder) that computes the DFP result. The LZA does not wait for that circuitry to finish computation of the DFP result. Instead it “anticipates” the number of leading zeros that the result's significand will contain.

Owner:ADVANCED MICRO DEVICES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com