Successive approximation type analog-digital converter for monotonic switching mode

A successive approximation, analog-to-digital converter technology, applied in the direction of analog/digital conversion, code conversion, instruments, etc., can solve comparator offset, SARADC power consumption, large fluctuations in speed and accuracy, and reduce the effective resolution of the system, etc. problem, to achieve the effect of fast speed, stable performance and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Specific embodiments of the present invention will be described below in conjunction with the accompanying drawings, so that those skilled in the art can better understand the present invention. It should be noted that in the following description, when detailed descriptions of known functions and designs would dilute the main content of the present invention, these descriptions will be omitted here.

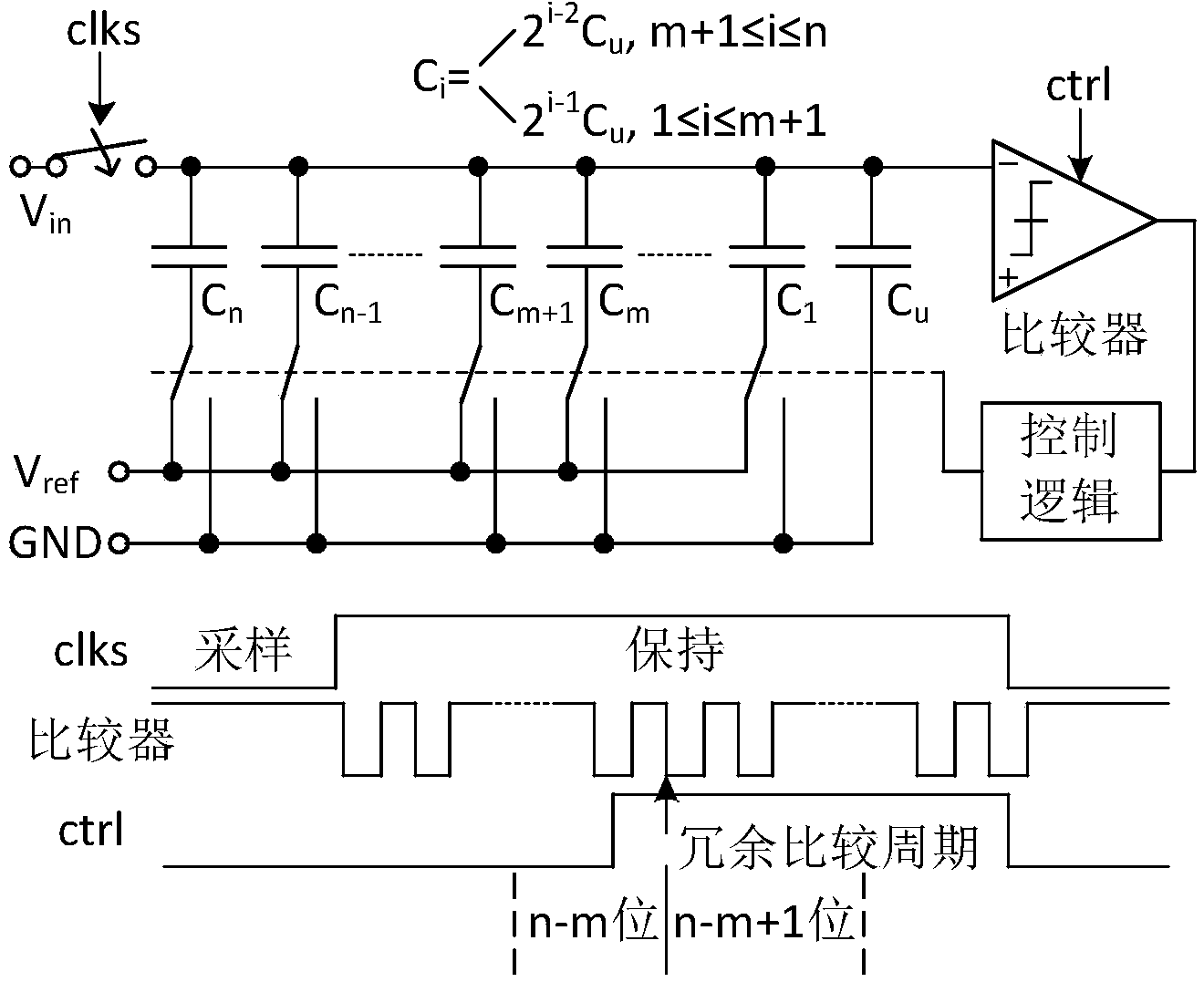

[0024] figure 1 It is the SAR ADC structure and timing diagram based on offset and noise error tolerance technology, including two parts: the upper part is the structure diagram of SAR ADC and the lower part is the working timing diagram of SAR ADC. The SAR ADC structure diagram shows the relationship between the charge redistribution DAC, comparator and control logic of n-bit SAR ADC. where the capacitance value of the DAC is determined by the formula above the array, C m and C m+1 Capacitance values are equal. Bits n-m are the redundant compare period. The timing...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com