Data caching and reproduction system for time-interleaved analog to digital conversion system

An analog-to-digital conversion and data caching technology, which is applied in the fields of analog-to-digital converter, analog-to-digital conversion, analog/digital conversion calibration/test, etc., can solve the problems of difficult design method, long development cycle and high hardware resource requirements. Achieve the effect of reducing integration complexity and hardware cost, and improving cache accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

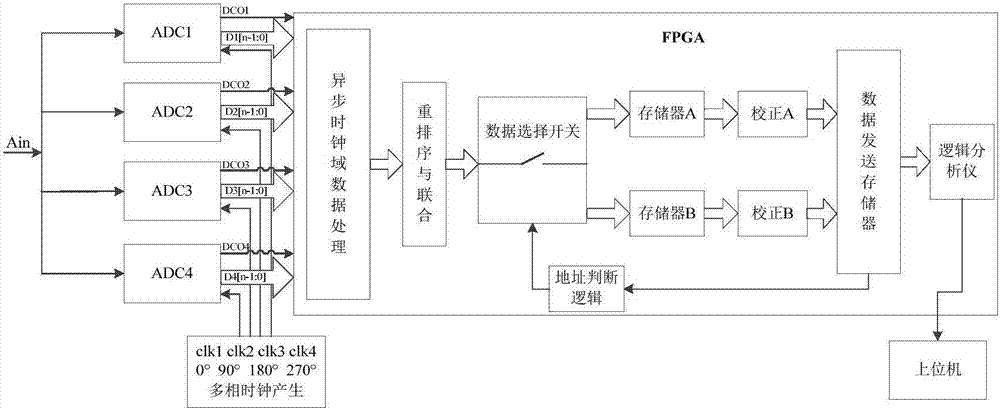

[0028] The present invention provides a data buffering and reproducing system of a time-interleaved analog-to-digital conversion system such as figure 1 As shown, it consists of a multi-channel ADC module, a multi-phase clock generation module, an asynchronous clock domain data processing module, a data reordering and correction module, and a data sending memory module.

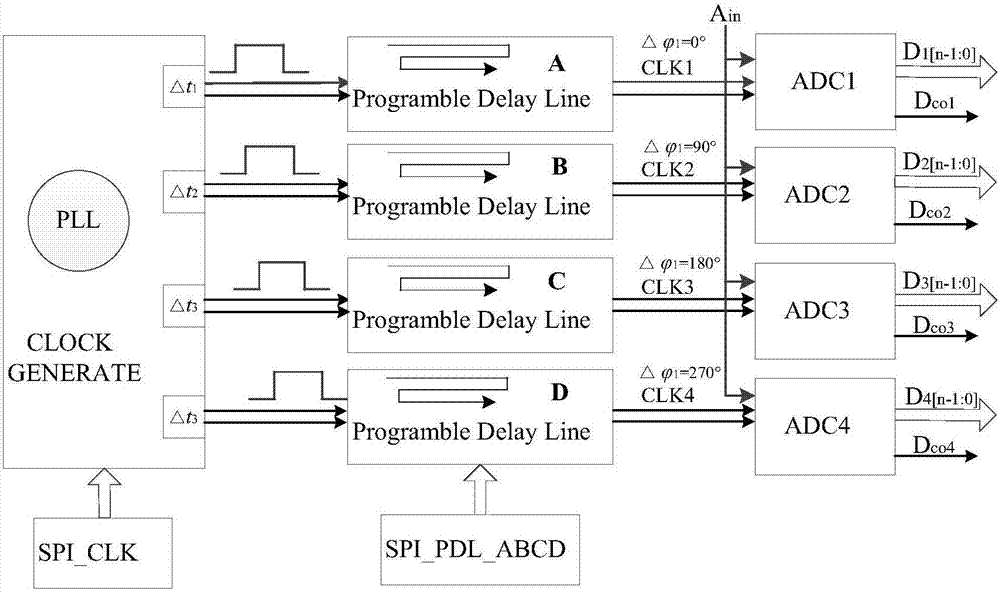

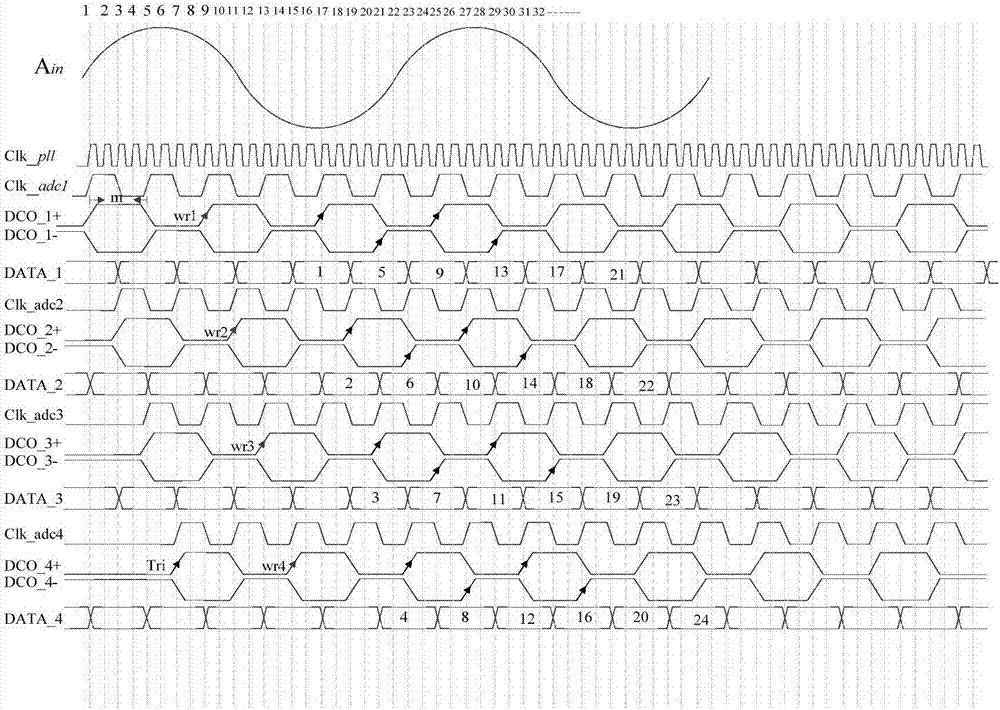

[0029] The principle diagram of high-precision multi-phase clock generation is as follows: figure 2 shown. The data reception of the TIADC system needs to be sequentially driven by the multi-phase clock. In order to obtain the accurate multi-phase drive clock of the data buffer unit, the PLL frequency multiplication technology is used to obtain a high-stability clock signal, and the internal register of the CLOCK GENERATE module is configured through SPI. Realize fine-tuning Δt of clock delay 1 , Δt 2 , Δt 3 , Δt 4 , since the internal time adjustment accuracy of the module is related to the minimum uni...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More