A mapreduce-based k-means clustering algorithm fpga acceleration system

A k-means clustering and acceleration system technology, applied in computing, computer components, multi-programming devices, etc., can solve the problems of high computational complexity, large algorithm time overhead, slow speed, etc., and achieve low power and low cost Inexpensive, real-time improvement effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

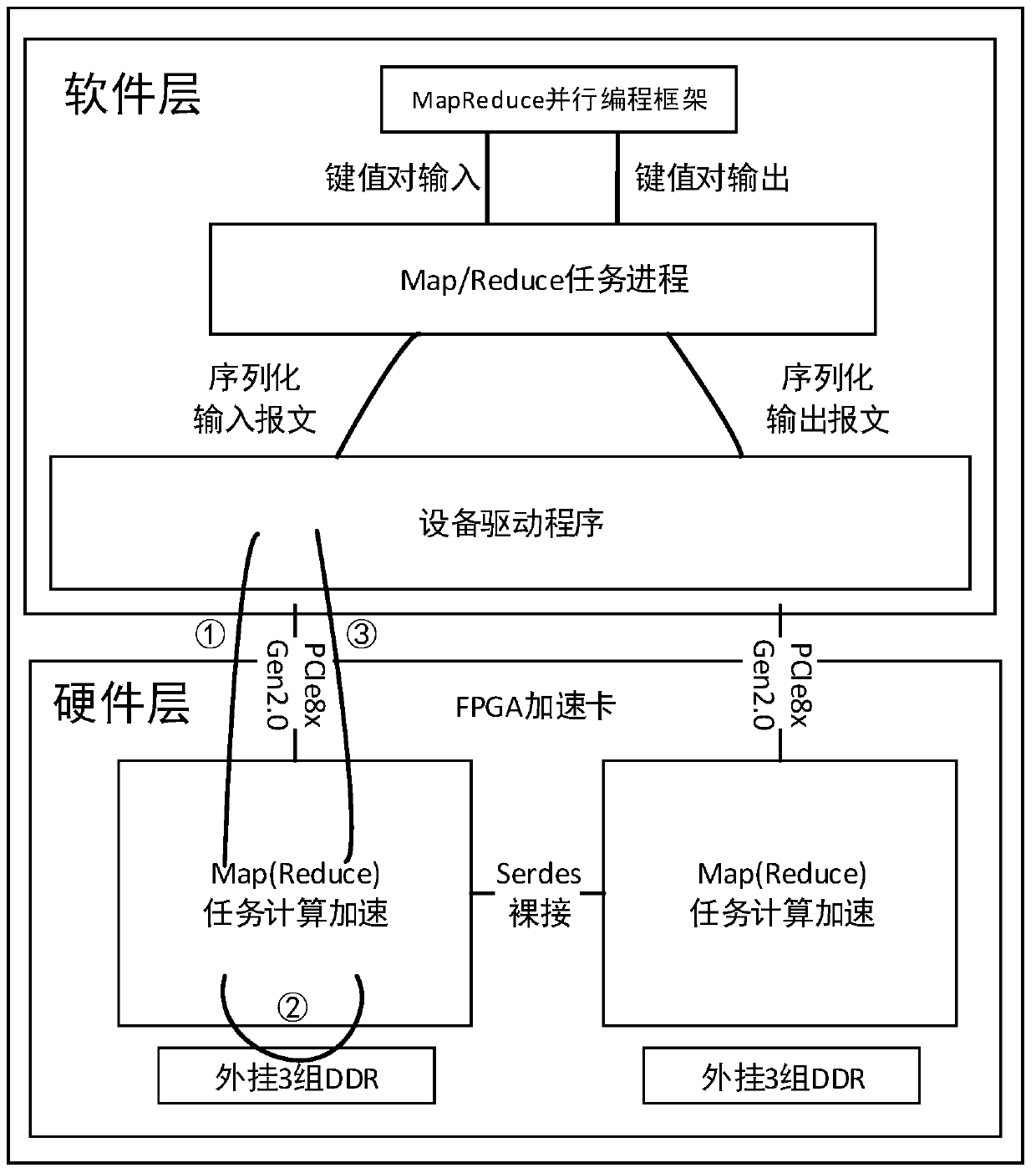

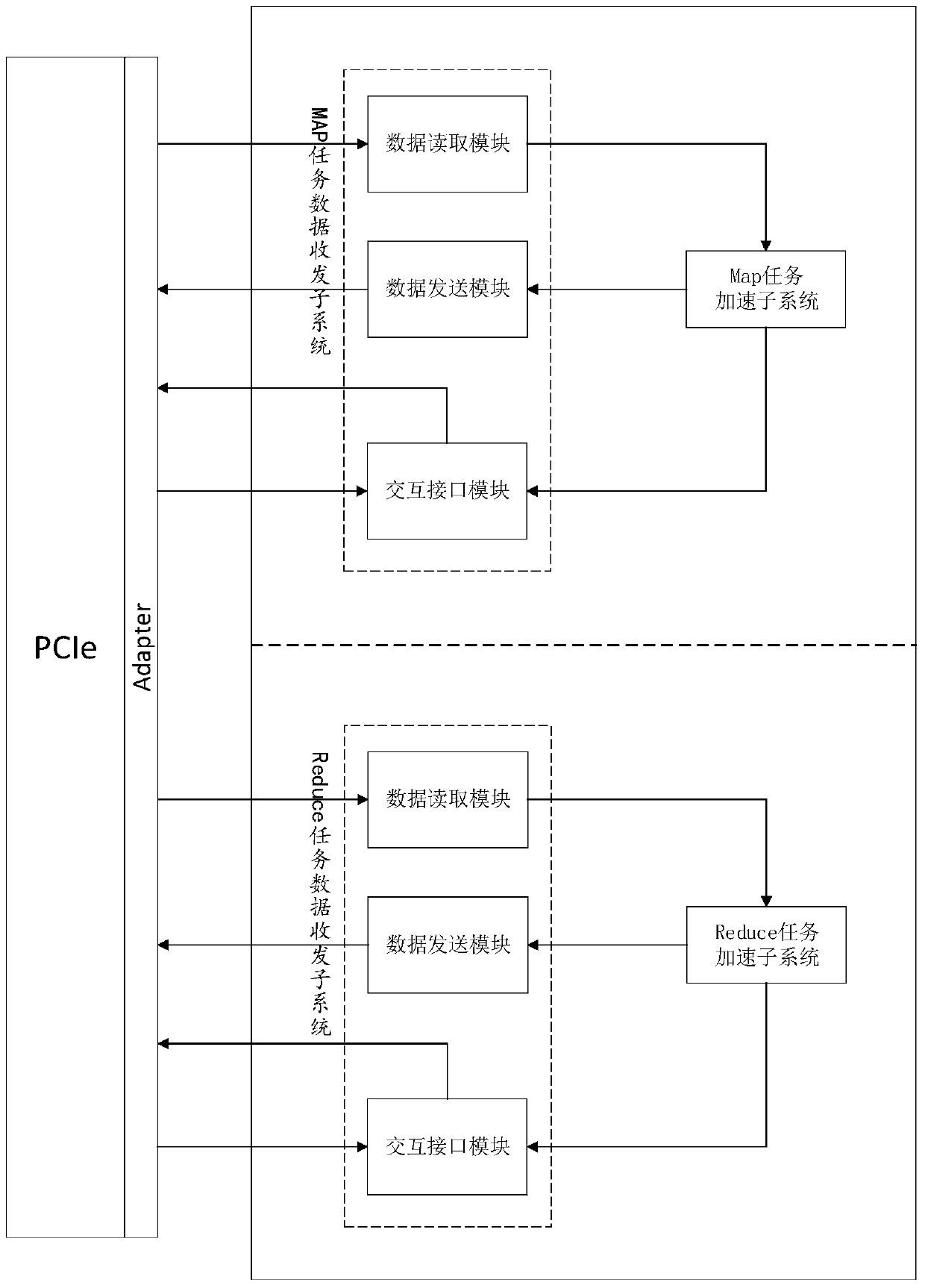

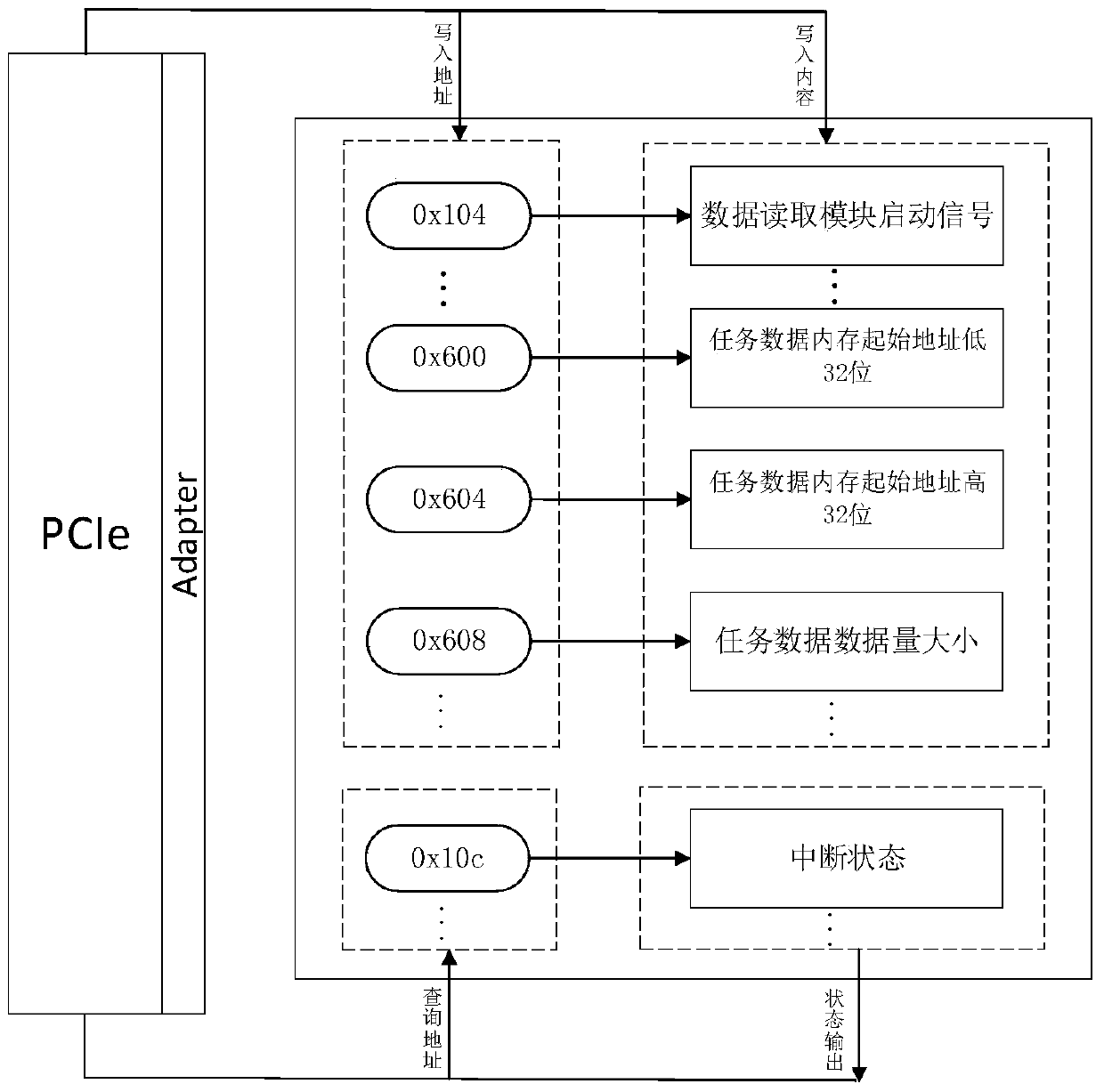

[0046] When the K-means clustering algorithm is calculated and processed under the native MapReduce computing framework, all calculation stages of the K-means clustering algorithm are performed on a general-purpose processor, which has high time complexity and limited processing capacity. The invention is applied to the extended MapReduce computing framework, and aims at accelerating the processing of the K-means clustering algorithm. Based on the original MapReduce computing framework, the expanded MapReduce computing framework uses FPGA-based hardware acceleration system as a coprocessor to achieve high-performance computing, and migrates the CPU-intensive computing process in the K-means cl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More