Circuit implementation method for avoiding blockage of assembly line

A technology for avoiding blockage and implementing methods, applied in the direction of electrical digital data processing, program control design, instruments, etc., can solve problems such as system design performance impact, chip efficiency reduction, etc., to reduce design optimization pressure, improve design efficiency, and solve efficiency Reduced effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The content of the present invention is described in more detail below:

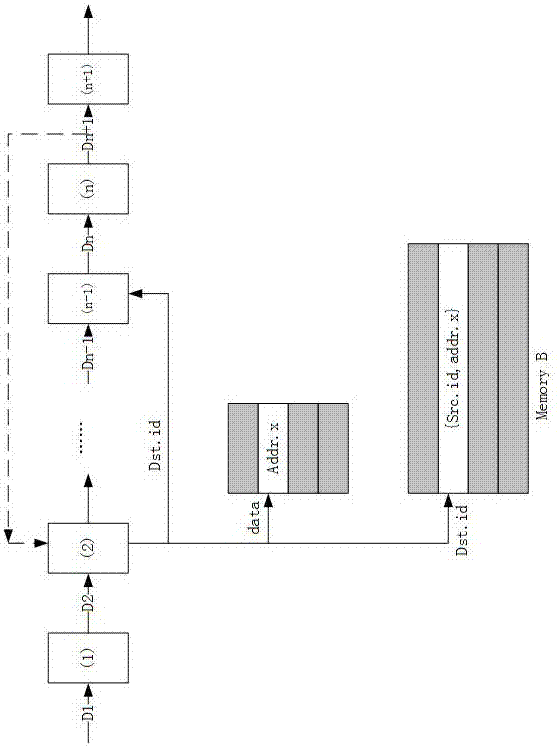

[0027] like figure 1 As shown, when the D2 data enters the (2) stage pipeline for processing, the result of the Dn-1 data entering the (n) stage processing is required as its input data to participate in the operation. However, at this time, the Dn-1 level data has only reached the (n-1) level pipeline for processing, and it needs to complete the n-level pipeline processing in the next clock cycle, and output the current D2 data in the (2) level pipeline. Therefore, at this time, the pipeline cannot correctly complete the processing that D2 data needs to complete in the (2) stage pipeline.

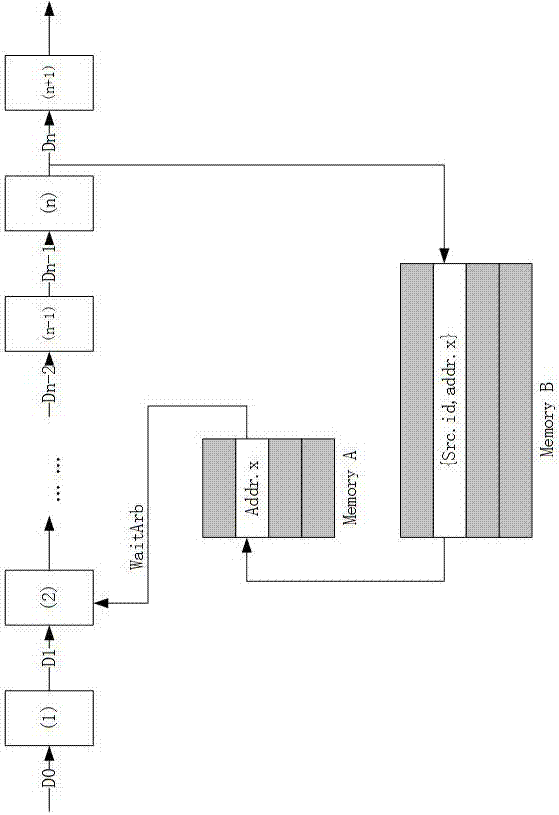

[0028] According to the traditional solution, to solve the problem from the circuit level, it is necessary to stagnate the D2 and D1 data in the (2) and (1) level pipeline processing, and wait for the Dn-1 data to reach the (n) level pipeline, complete Processing, when the data is output to the (2) stage pip...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More