FPGA based redundant double-network-interface configurable Ethernet IP core

An Ethernet, dual network port technology, applied in the field of Ethernet IP core, can solve the problem of inability to realize data transmission, and achieve the effect of low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

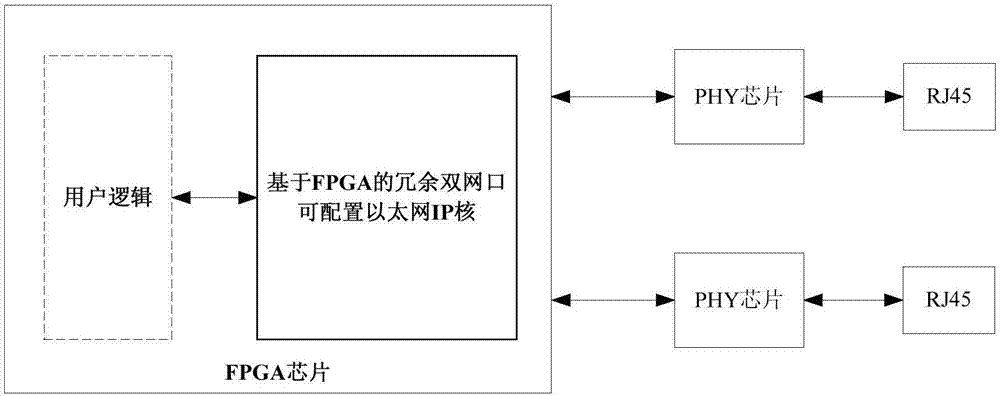

[0030] Such as figure 1 As shown, the FPGA-based redundant dual network port configurable Ethernet IP core in this embodiment is implemented on the StratixII series FPGA architecture system. All circuit boards that meet the following requirements can realize the verification of the IP core.

[0031] 1) There are two PHY chips and two RJ45 network ports on the circuit board;

[0032] 2) There is an FPGA chip that can work and configure normally on the circuit board;

[0033] 3) Two PHY chips are connected to one FPGA chip at the same time;

[0034] 4) The FPGA chip has a custom IO interface.

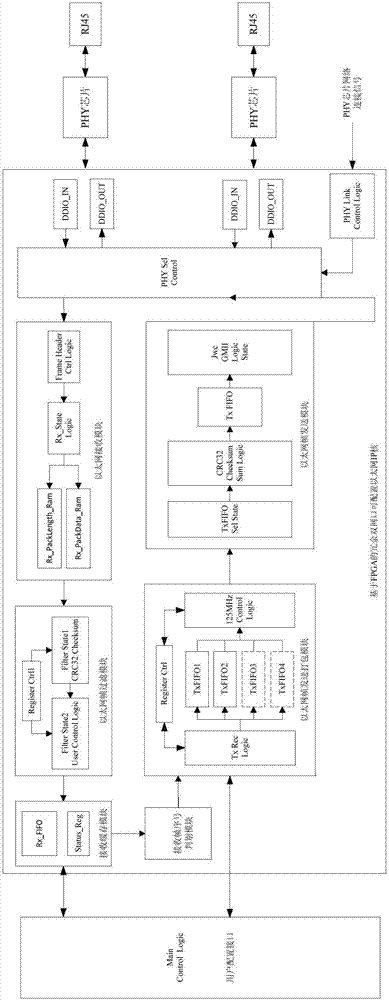

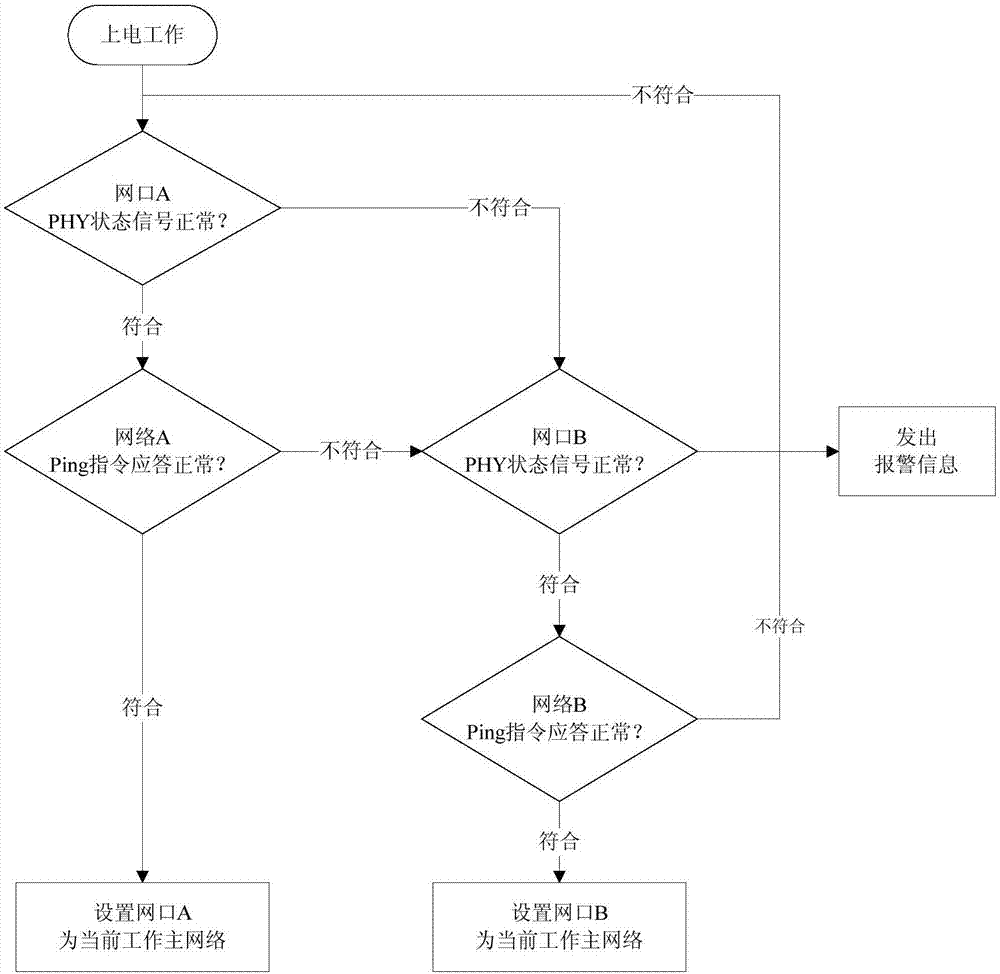

[0035] FPGA-based redundant dual-network Ethernet IP core, in which the FPGA uses the RGMII interface to communicate with the physical layer PHY chip, and all protocols above the physical layer are implemented inside the FPGA; the redundant dual-network port Ethernet IP core is not The combination of two single network port IP cores is a redesigned Ethernet IP core with redundant dual...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com