A gate-controlled thyristor with high current rise rate

A high-current, thyristor technology, applied in the direction of circuits, electrical components, semiconductor devices, etc., can solve the problems of device surge current failure, inability to adjust the concentration distribution, etc., and achieve the effect of high current rise rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

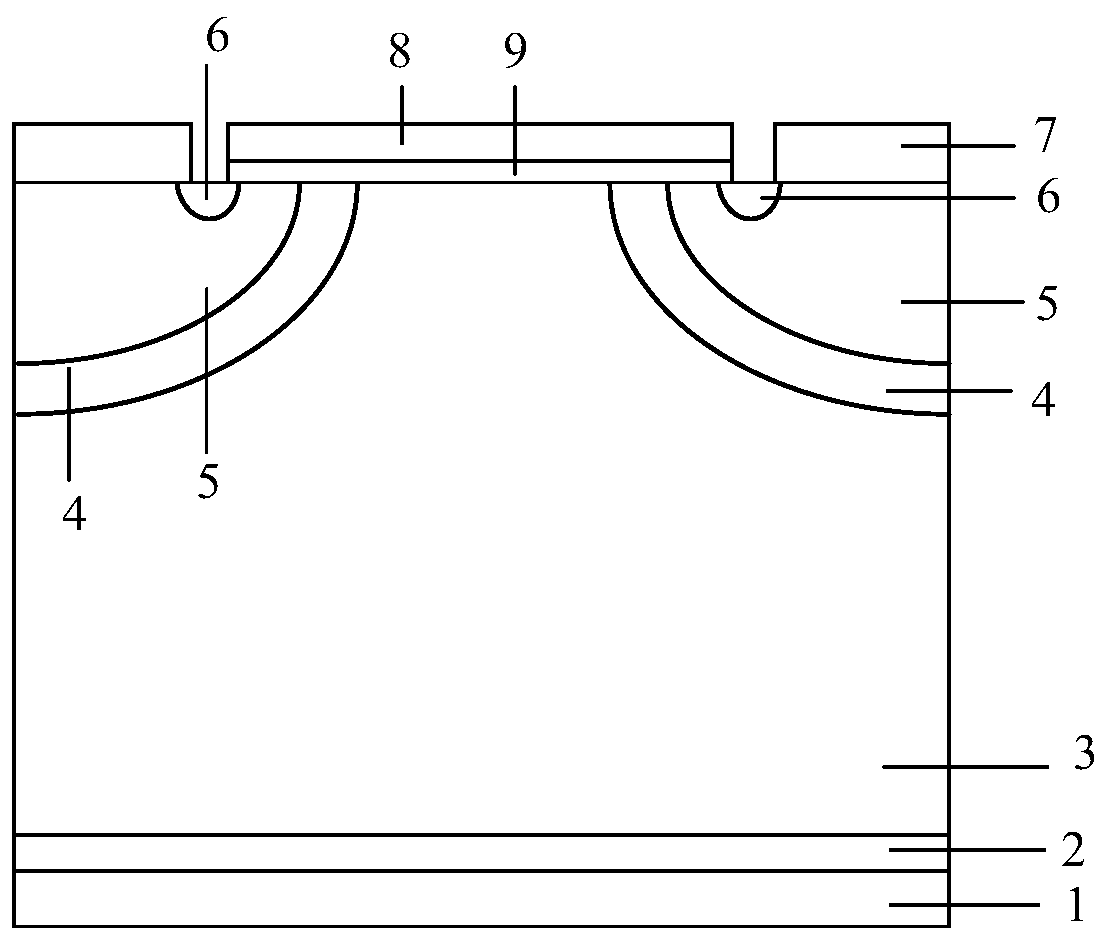

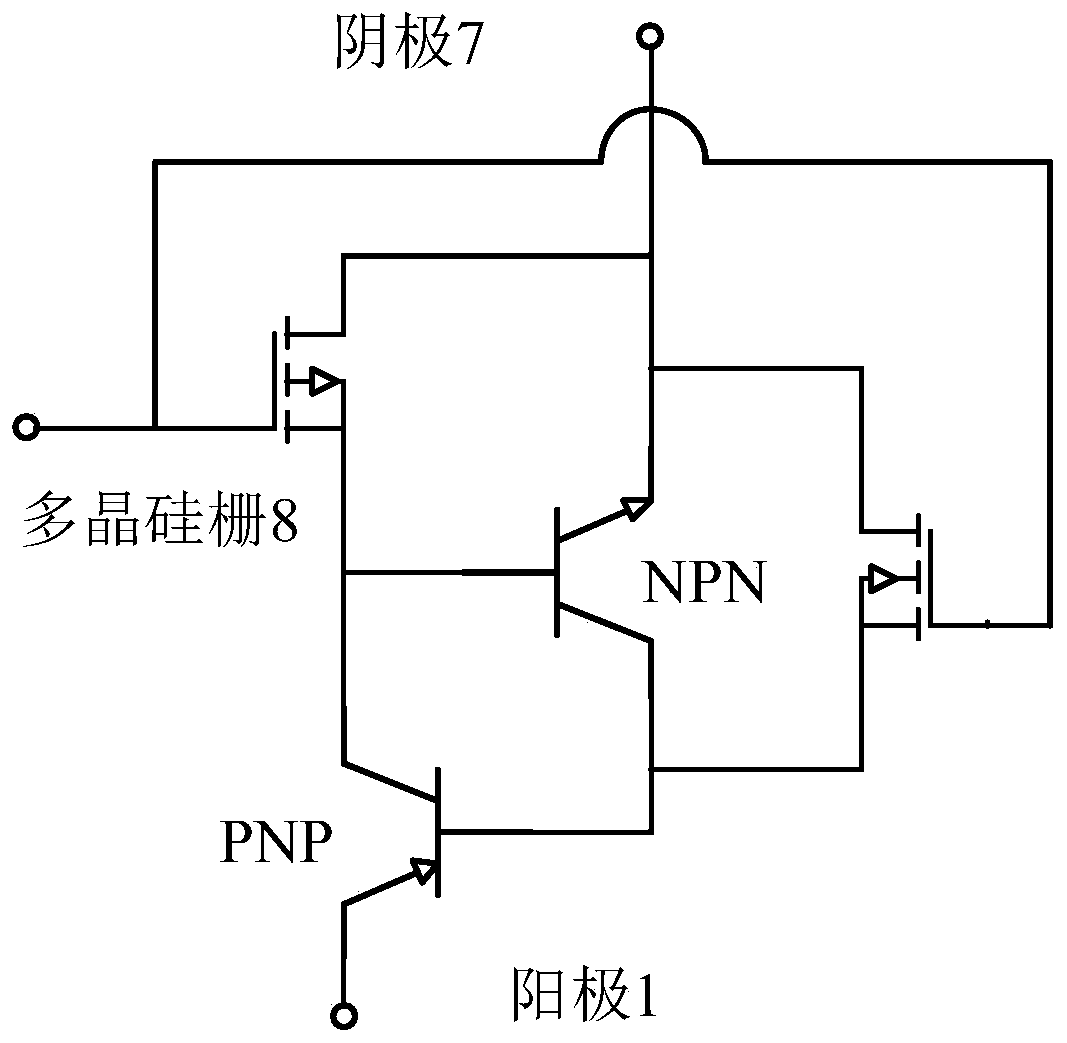

[0016] Such as figure 1 As shown, this embodiment provides a gate-controlled thyristor with a high current rise rate, comprising a first conductivity type semiconductor doped substrate 2 and a metal anode disposed on the back of the first conductivity type semiconductor doped substrate 2 1. The second conductivity type semiconductor doped epitaxial layer 3 is arranged on the front surface of the first conductivity type semiconductor doped substrate 2, and the top surface of the second conductivity type semiconductor doped epitaxial layer 3 is provided with a metal cathode 7 and An insulated gate, wherein the insulated gate is located in the middle, and the metal cathode 7 is located on both sides of the insulated gate and isolated therefrom; the insulated gate includes a gate dielectric layer 9 and a polysilicon gate 8 arranged on the upper surface of the gate dielectric layer 9; Two conductive type semiconductor doped epitaxial layers 3 are respectively provided with a first c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More