Low-drop-out voltage stabilizer

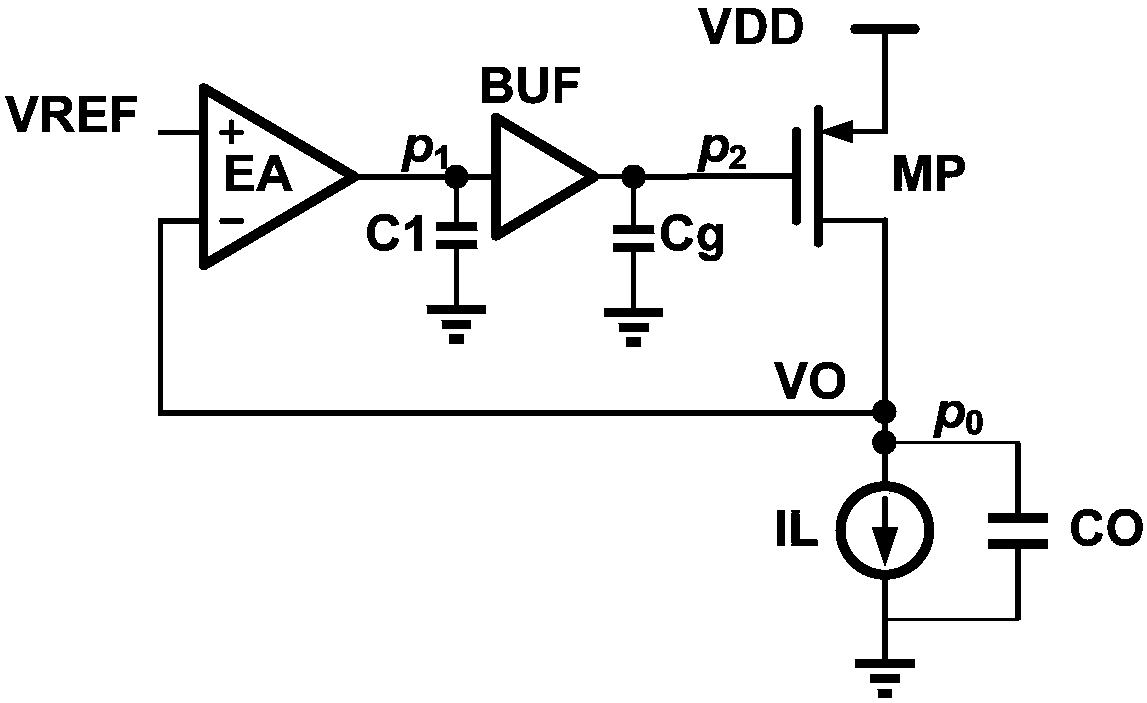

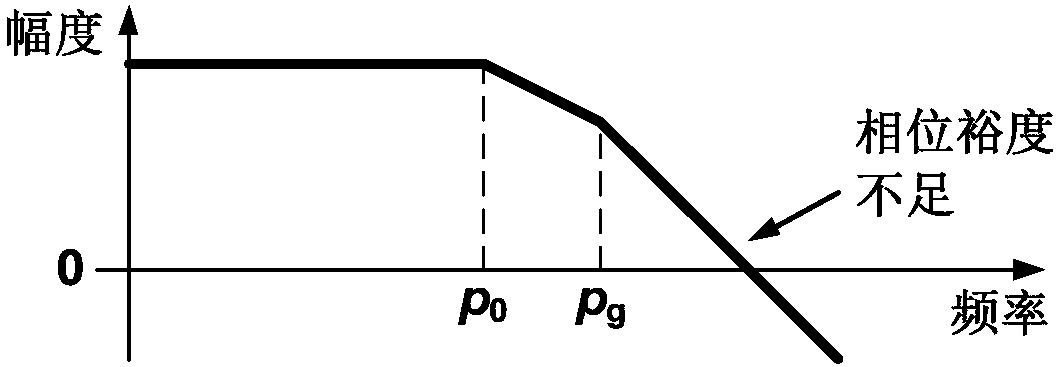

A low-dropout voltage regulator and error amplifier technology, which is applied in the direction of instruments, electric variable adjustment, control/regulation systems, etc., can solve problems such as system instability and phase drop, and achieve the effect of high and low frequency gain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

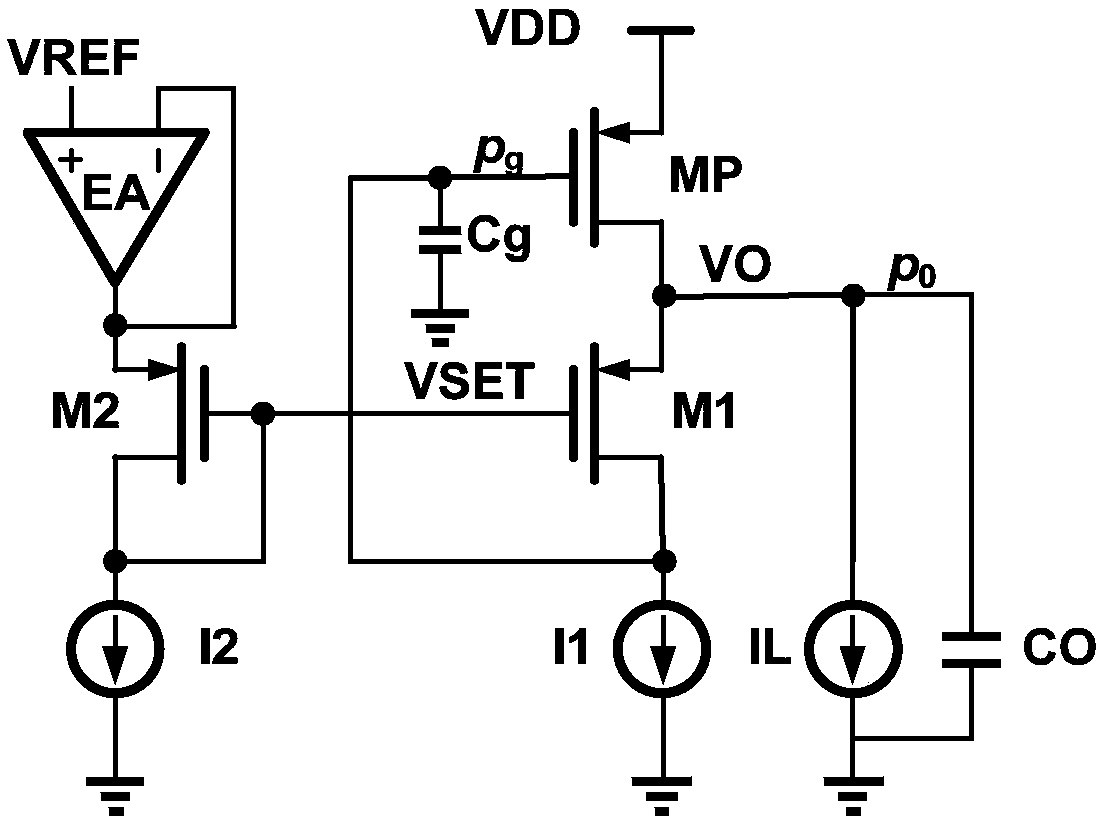

[0046] see Figure 7 , which is a structural diagram of the low dropout voltage regulator according to Embodiment 1 of the present invention. The present invention provides a high-speed and stable low-dropout voltage regulator, including an error amplifier EA, a first field effect transistor M1, a second field effect transistor M2, a power device MP, a first current source I1, a second current source I2, A load current source IL, a first capacitor CO, a second capacitor Cg, a third capacitor Cm and a super source follower SSF.

[0047] The positive input terminal of the error amplifier EA receives the reference voltage VDD, and the negative input terminal is connected to the output terminal.

[0048] The drain of the second field effect transistor M2 is connected to the output terminal of the error amplifier EA, the source is grounded through the second current source I2, and the gate is grounded through the second current source I2.

[0049] The drain of the power device MP...

Embodiment 2

[0065] Compared with Embodiment 1, the main configuration of the damping coefficient control module of Embodiment 2 is different. Specifically, see Figure 11 , which is a structural diagram of the low dropout voltage regulator of the second embodiment. The damping coefficient control module DFC includes a fifth field effect transistor M5, a fourth capacitor C D and a fifth current source I5. The drain of the fifth field effect transistor M5 is connected to the power supply voltage VDD, the gate of the fifth field effect transistor M5 is connected to the gate of the fourth field effect transistor M4, and the source of the fifth field effect transistor M5 passes through the fifth field effect transistor M5. The current source I5 is grounded; the fourth capacitor C D The two ends of are respectively connected to the gate and the source of the fifth field effect transistor M5.

[0066] In this embodiment 2, the DFC module consists of M5, I5 and C D constitute. Among them, M...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More