Vernier type TDC circuit based on FPGA carry chain

A technology of carry chains and circuits, which is applied in the direction of electrical unknown time interval measurement, devices for measuring time intervals, clocks, etc., can solve the problems of uneven distribution of delays in delay units, uncontrollable and exacerbated non-uniformity, and reduce non-uniformity. Effects of linearity errors DNL and INL, reducing implementation complexity and resource overhead, and improving measurement accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

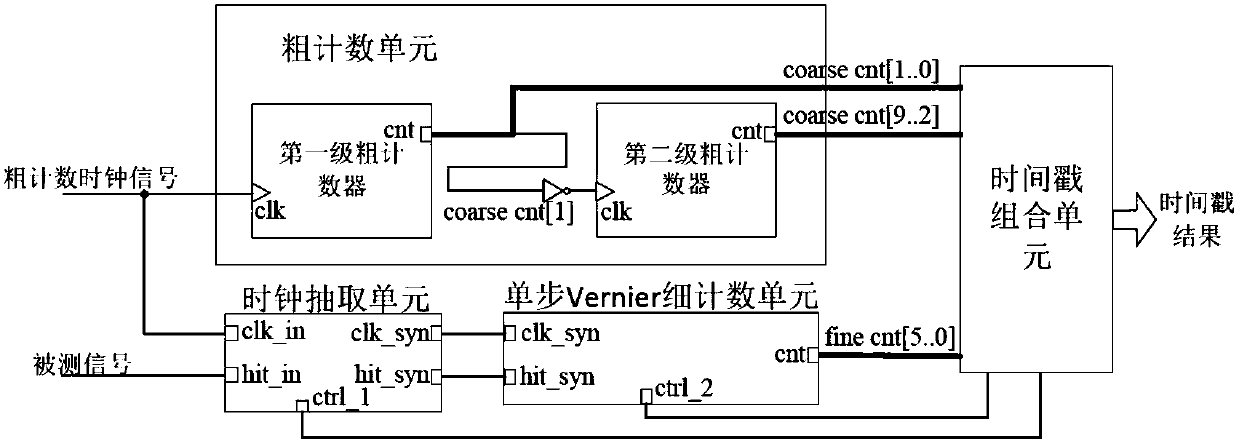

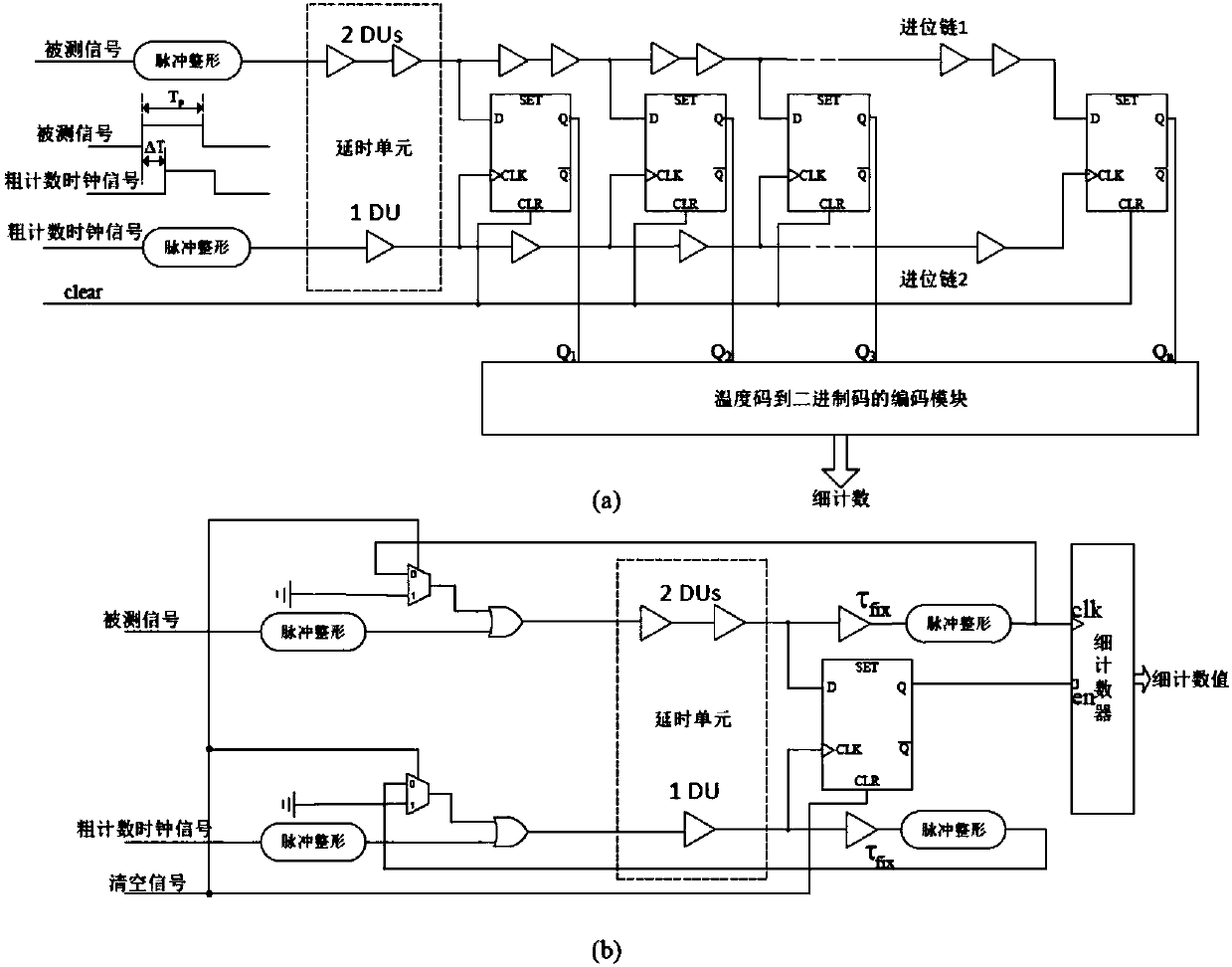

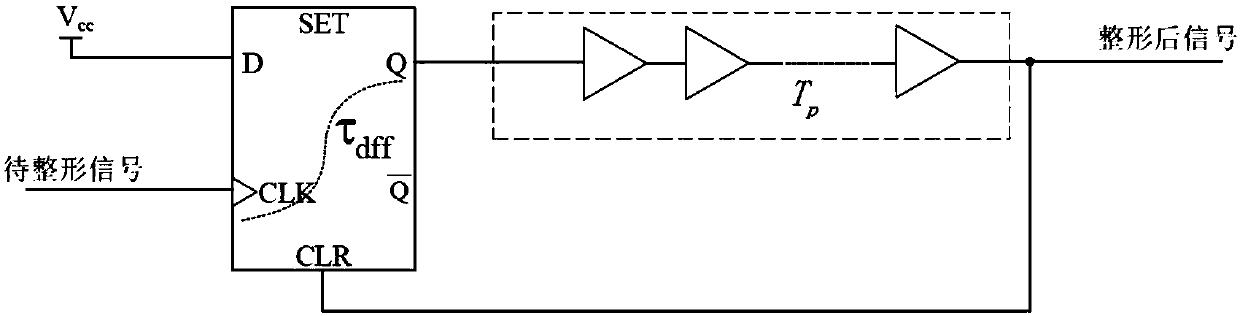

[0034] combine figure 1 , the present invention is based on the single-step Vernier type TDC circuit of FPGA delay chain, comprises coarse counting unit, single-step Vernier fine counting unit, clock extracting unit and time stamp combination unit, wherein coarse counting unit adopts two cascaded counters to improve coarse counting clock frequency. The values of the two coarse counters are fed together into the timestamp combination unit as a result of the coarse time count. The single-step Vernier fine counting unit contains two delay lines composed of cascaded delay units of the carry chain. The output end of each delay line is returned to the input end of the delay line to form an oscillation loop. The two loops contain only 2 equivalent delay units (corresponding to slow delay lines) and 1 equivalent delay unit (corresponding to fast delay lines). The output end of the slow delay line is connected to the clock port of the fine counter to trigger the number of times the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More