Method for conducting instruction dispatching based on network load features in data stream architecture

A network load and instruction scheduling technology, applied in concurrent instruction execution, electrical digital data processing, machine execution devices, etc., can solve the problems of computing node stall, idle, execution speed bottleneck, etc., to improve utilization and network bandwidth utilization efficiency, improving component utilization and network resource utilization and throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

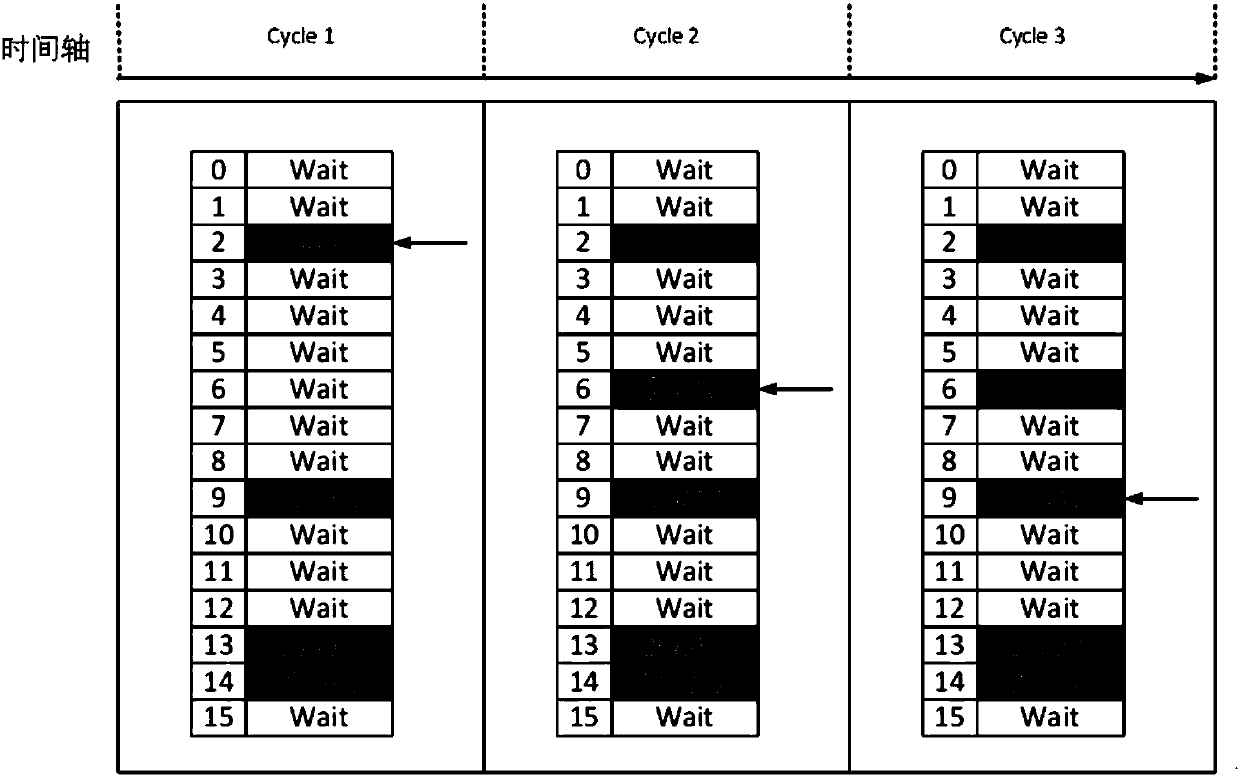

[0028] The present invention provides a method for command scheduling based on network load characteristics in a data flow architecture, which includes the following steps:

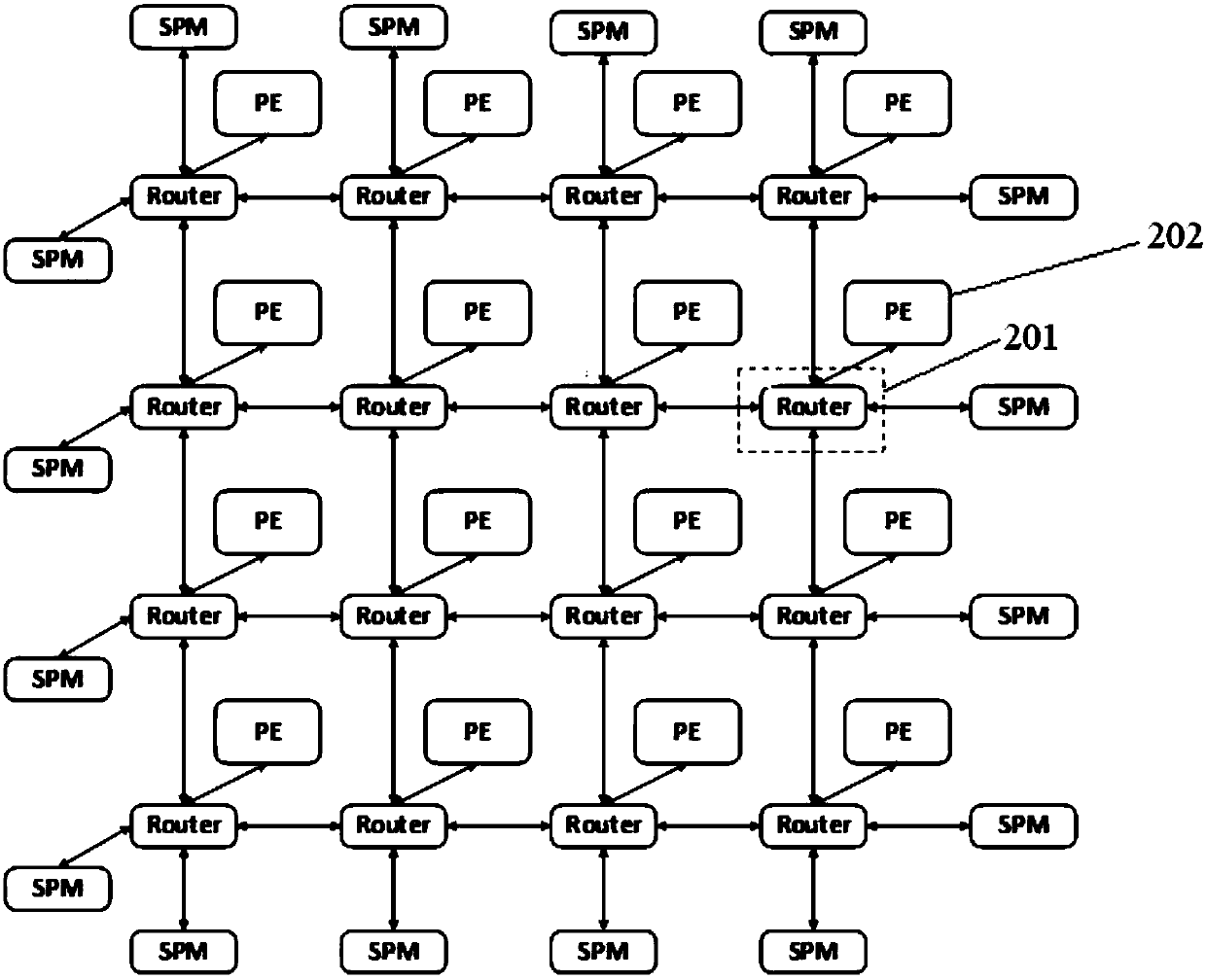

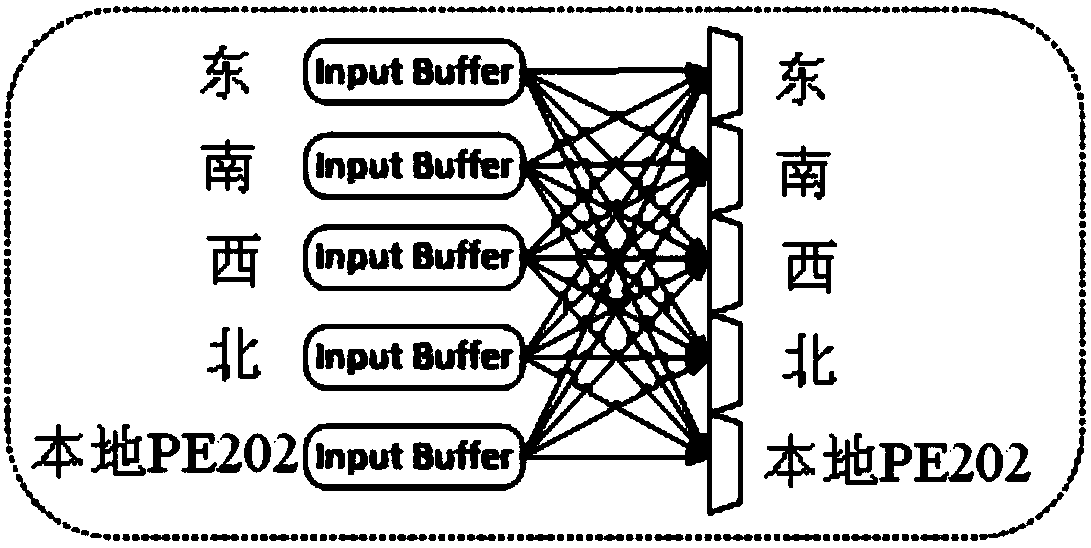

[0029] A congestion detection unit is set inside each on-chip route, an output buffer unit is set at each exit of each on-chip route, and an instruction selection unit is set inside each computing node;

[0030] Figure 4 Schematic diagram for the output buffer components in on-chip rout...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More