Measuring Method of Effect of Surface State Traps on Device Output Characteristics

A technology of output characteristics and measurement methods, applied in the direction of single semiconductor device testing, electrical measurement, measurement devices, etc., can solve problems such as the reduction of output power density, and achieve the effect of simple testing methods

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

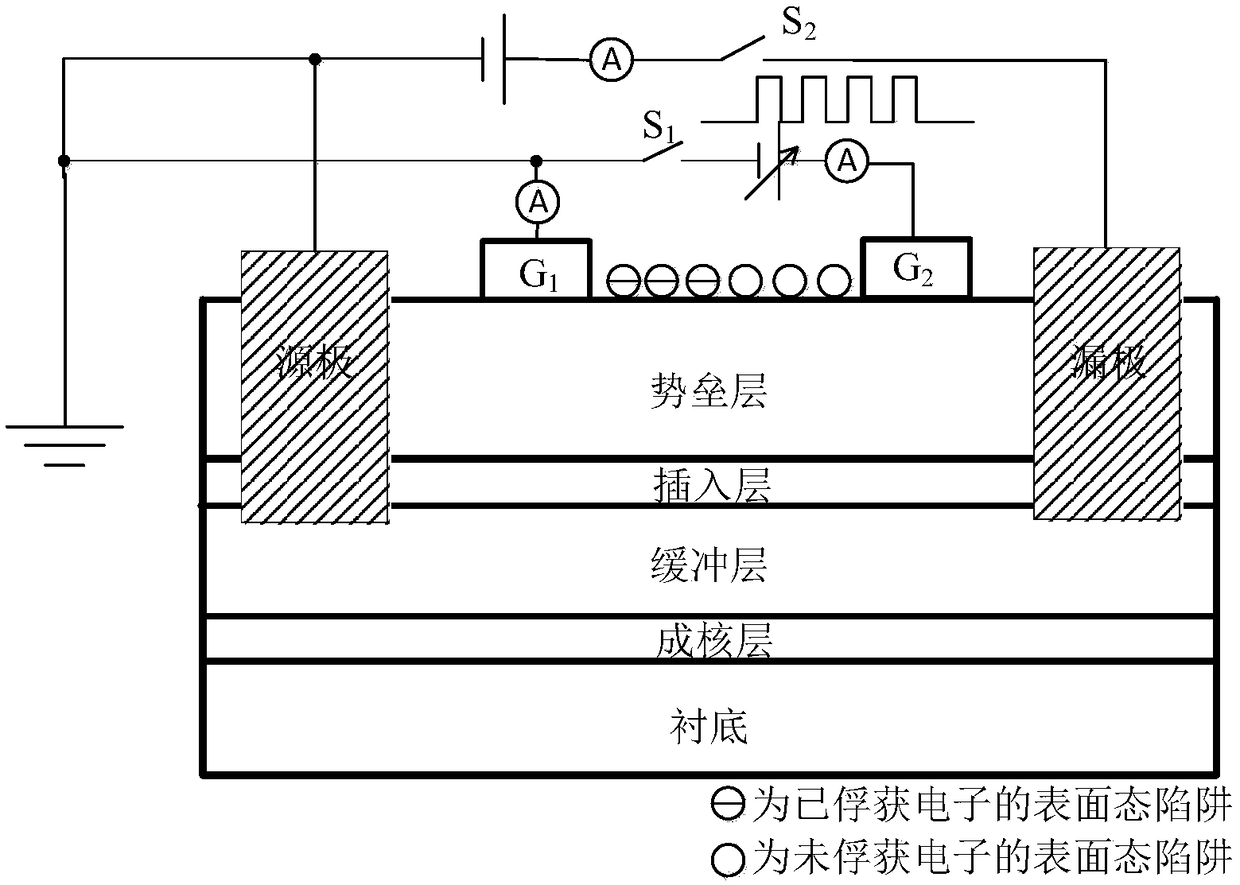

[0035] The specific implementation of the present invention will be further described in detail below in conjunction with the accompanying drawings and examples. The device under test in this example is a HEMT device as an example, and this embodiment is used to illustrate the present invention, but not to limit the scope of the present invention.

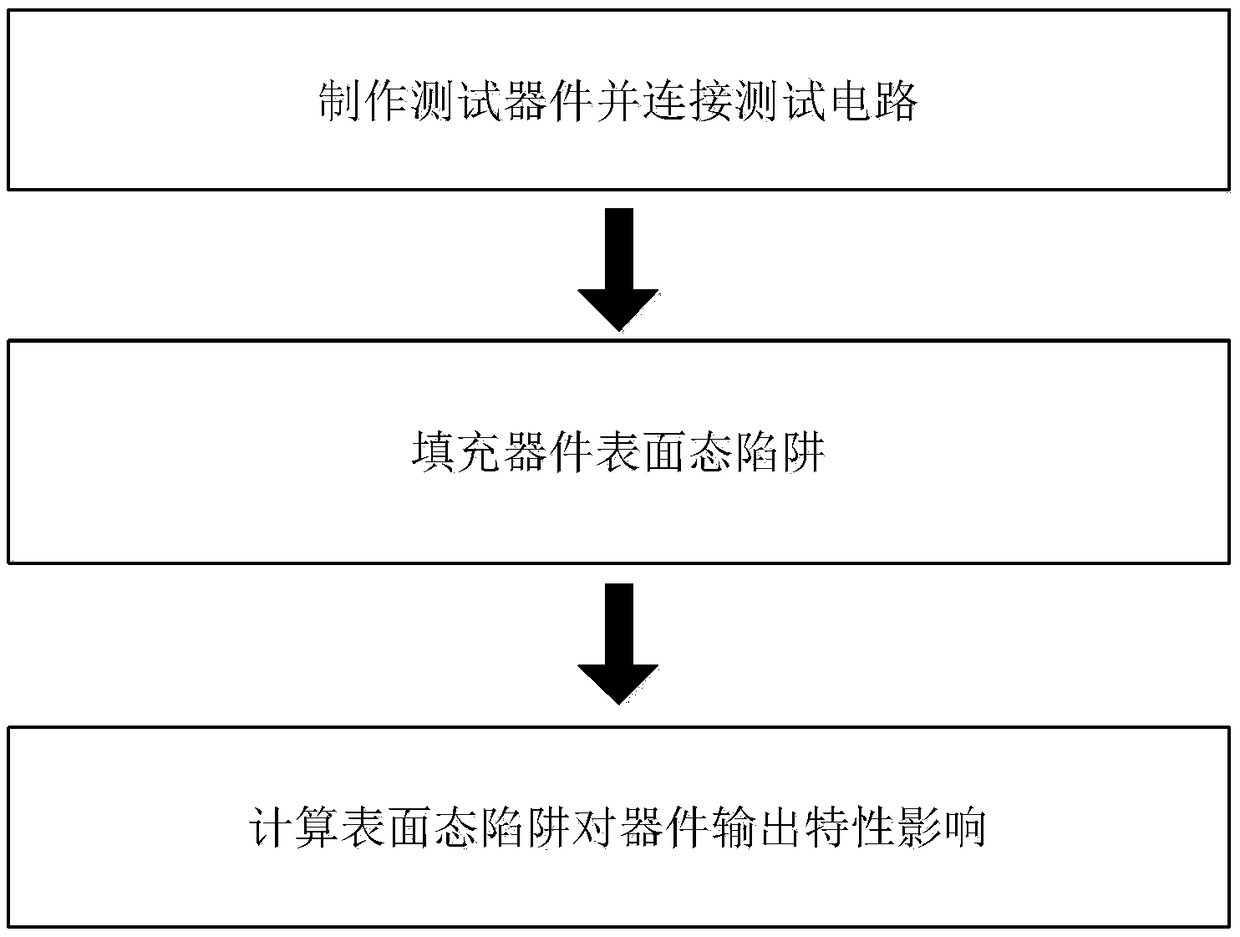

[0036] refer to figure 1 , the specific implementation of this example is as follows:

[0037] Step 1, make the test device and connect the test circuit.

[0038] 1a) Make a new gate between the source and drain of the tested HEMT device to form a double gate structure, and the two gates are respectively marked as G 1 and G 2 , the material and process of the new gate should be consistent with the original gate of the device; it is also possible to directly use the same process and material to fabricate two gates during the manufacturing process of the device under test to form a double gate structure device;

[0039] 1b) Conne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More