Semiconductor device structure and fabrication method thereof

A device structure and semiconductor technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of low yield of critical size chips, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

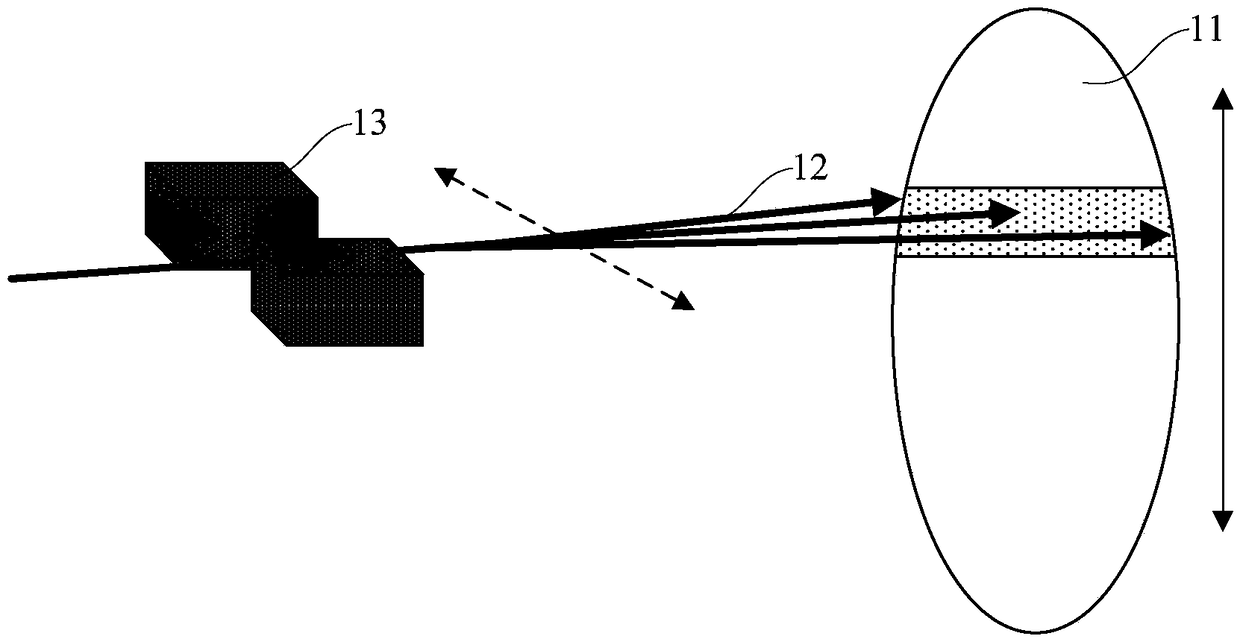

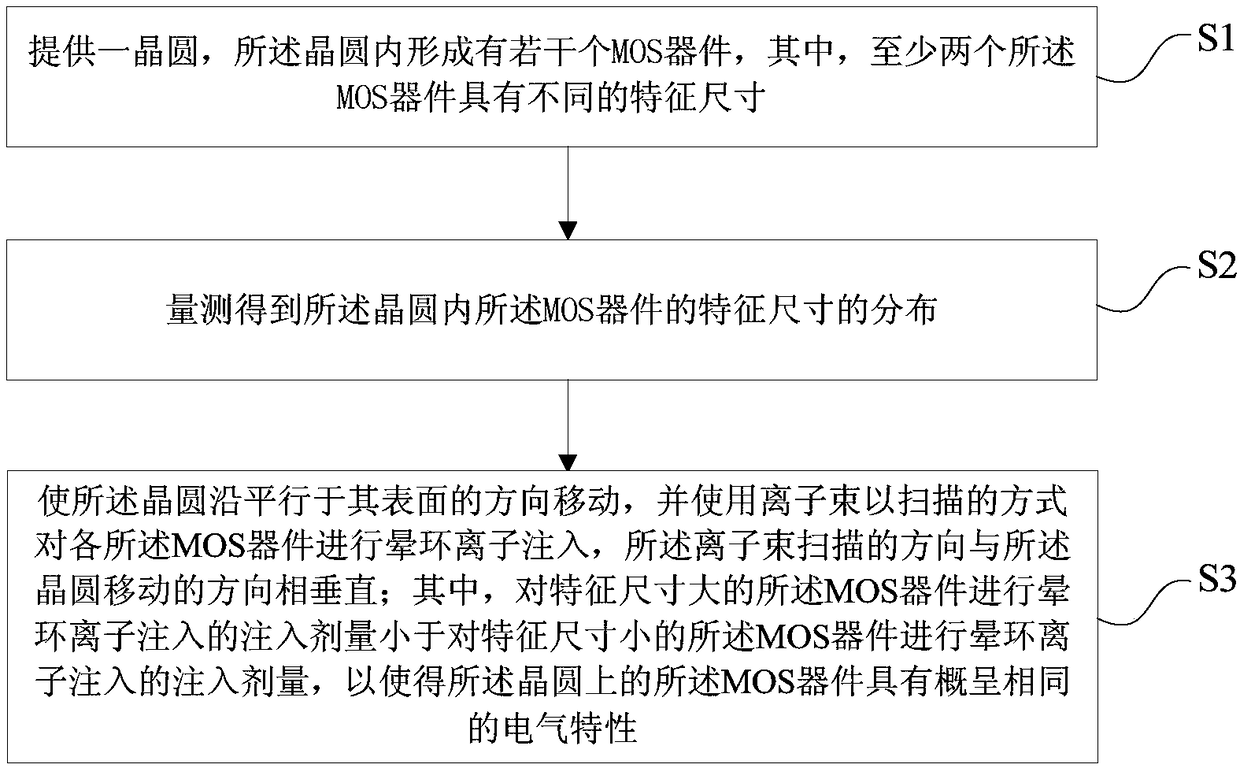

[0062] see figure 1 , the invention provides a kind of preparation method of semiconductor device structure, the preparation method of described semiconductor device structure comprises the following steps:

[0063] 1) providing a wafer in which several MOS devices are formed, wherein at least two of the MOS devices have different feature sizes;

[0064] 2) measuring and obtaining the distribution of the characteristic sizes of the MOS devices in the wafer;

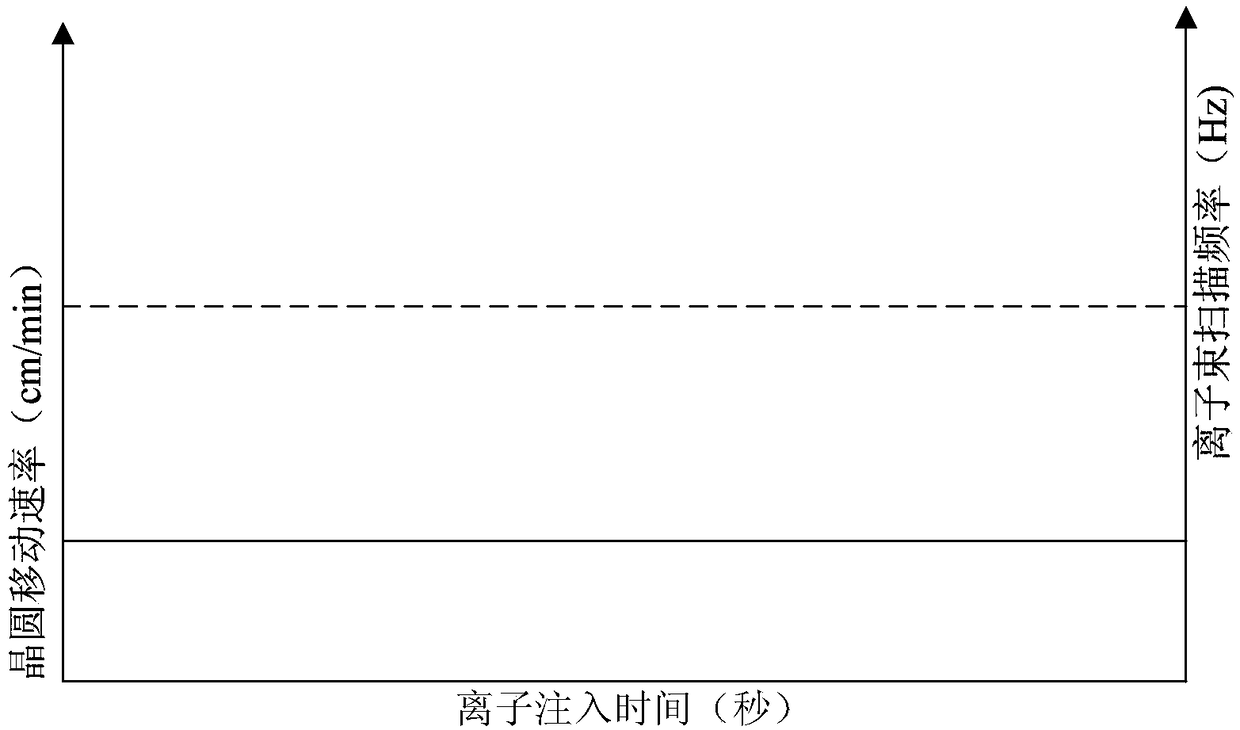

[0065] 3) moving the wafer in a direction parallel to its surface, and performing halo ion implantation on each of the MOS devices in a scanning manner using an ion beam, the scanning direction of the ion beam is the same as the moving direction of the wafer The directions are perpendicular; wherein, the implantation dose of halo ion implantation for the MOS device with a large feature size is smaller than the implantation dose for halo ion implantation for the MOS device with a small feature size, so that the The MOS d...

Embodiment 2

[0091] Please continue to refer to Embodiment 1 Figure 4 to Figure 15 , the present invention also provides a semiconductor device structure, the semiconductor device structure is prepared by the preparation method described in Embodiment 1, the semiconductor device structure includes: a number of MOS devices arranged at intervals, wherein at least two Each of the MOS devices has different feature sizes; an annular halo implantation region 25 is formed in the channel of each of the MOS devices, and the ion implantation concentration in the halo implantation region 25 is inversely proportional to that of the MOS device. Feature size.

[0092] As an example, the ion implantation concentration in the halo implantation region 25 in the MOS device with a relatively large feature size is lower than the ion implantation concentration in the halo implantation region 25 in the MOS device with a small relative feature size, , to ensure that the MOS devices on the wafer 21 have substan...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More