A kind of manufacturing method of MOS type device

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as material lattice damage and lattice damage, and achieve the effect of reducing lattice damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

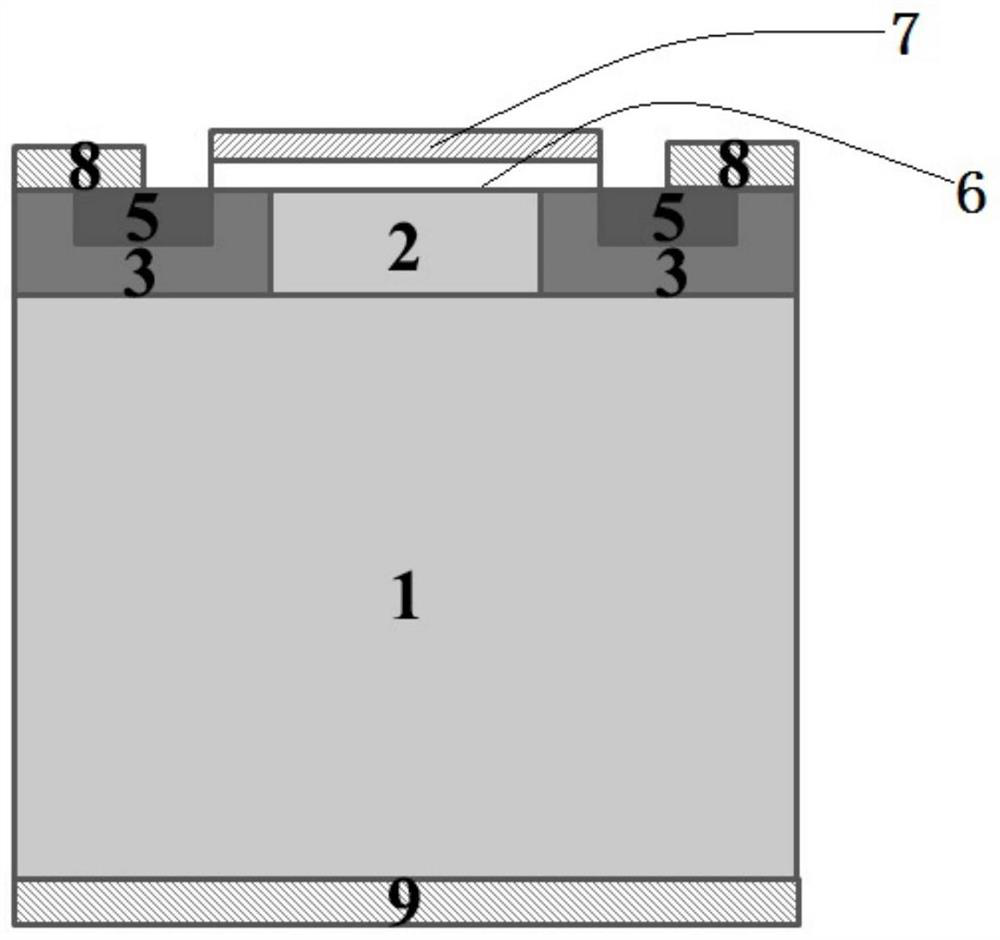

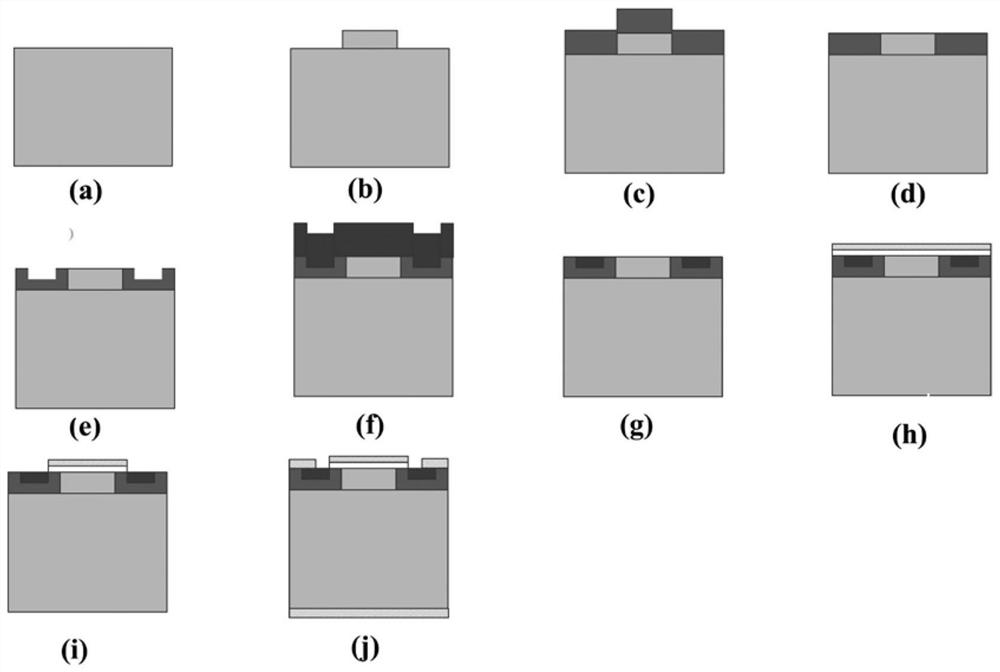

[0019] Embodiment 1: as image 3 Shown is the process of manufacturing MOSFET devices.

[0020] (1) Epitaxially grow the epitaxial layer 1 so as to meet the blocking requirements of the device, such as image 3 as shown in (a);

[0021] (2) Mesa 2 is etched on the epitaxial layer, such as image 3 as shown in (b);

[0022] (3) Epitaxially growing the initial well region 3 on the mesa, the height of the initial well region should be greater than or equal to the height of the mesa; as image 3 as shown in (c);

[0023] (4) Use the CMP process to obtain a well area with a flat and smooth surface, and the height of the well area obtained after the CMP process is the same as the height of the mesa, such as image 3 as shown in (d);

[0024] (5) Obtain the groove area 4 by using processes such as etching, such as image 3 as shown in (e);

[0025] (6) The thickness of the initial source region 5 for epitaxial growth is higher than the depth of the groove region 4, and the he...

example 2

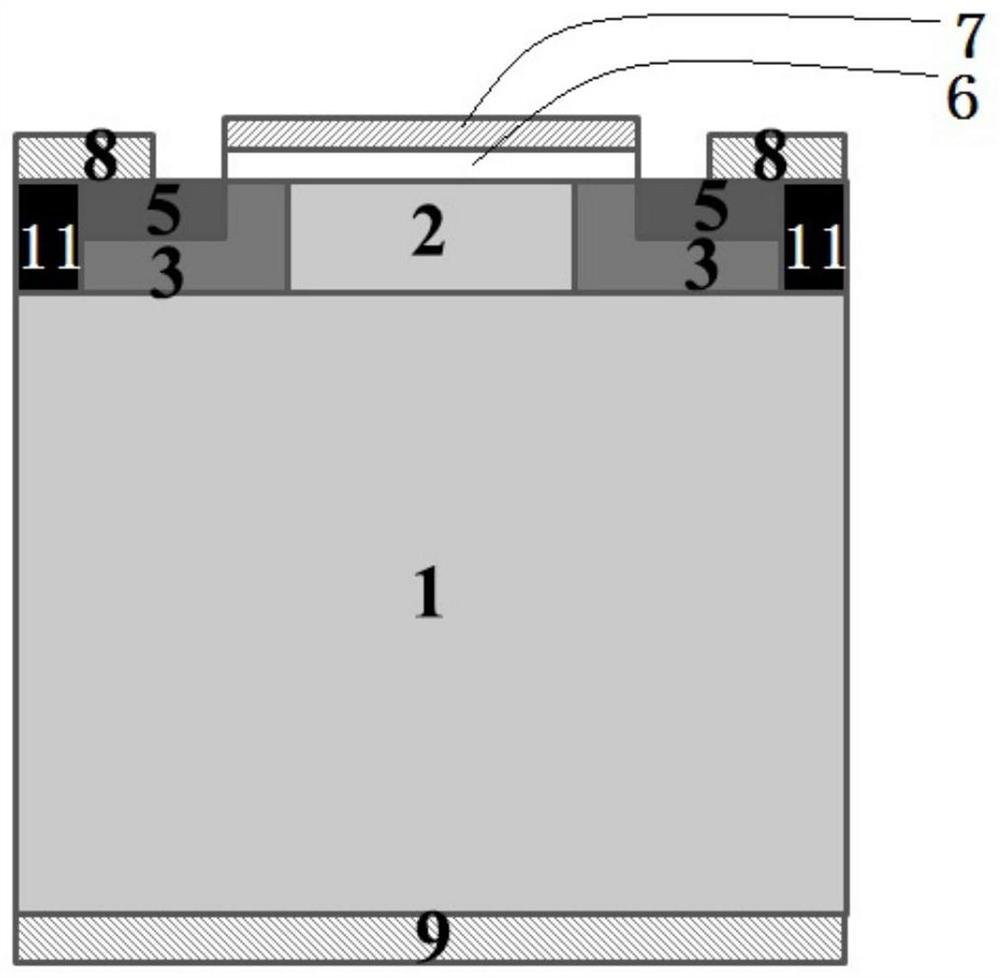

[0031] Example 2: if Figure 4 Shown is the process of manufacturing IGBT devices.

[0032] (1) Epitaxially grow the epitaxial layer 1 so as to meet the blocking requirements of the device, such as Figure 4 as shown in (a);

[0033] (2) The mesa 2 etched on the epitaxial layer, such as Figure 4 as shown in (b);

[0034] (3) The initial well region 3 is epitaxially grown on the mesa, and the height of the initial well region is greater than or equal to the height of the mesa, such as Figure 4 as shown in (c);

[0035] (4) Use the CMP process to obtain a flat and smooth well region, and the height of the obtained well region is the same as the height of the mesa, such as Figure 4 as shown in (d);

[0036] (5) Obtain the groove area 4 by using processes such as etching, such as Figure 4 as shown in (e);

[0037] (6) The thickness of the initial source region 5 for epitaxial growth is higher than the depth of the groove region, and the height of the initial source reg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More