Preparation method of 3d NAND wiring hole including silicon-rich silicon nitride isolation dielectric layer

A technology of silicon nitride layer and silicon-rich silicon nitride, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of affecting the electrical performance of devices, large etching energy, and nitrogen residue, so as to improve stability and Reliability, effects of avoiding uneven distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Exemplary embodiments of the present disclosure will be described in more detail below with reference to the accompanying drawings. Although exemplary embodiments of the present disclosure are shown in the drawings, it should be understood that the present disclosure may be embodied in various forms and should not be limited by the embodiments set forth herein. Rather, these embodiments are provided for more thorough understanding of the present disclosure and to fully convey the scope of the present disclosure to those skilled in the art.

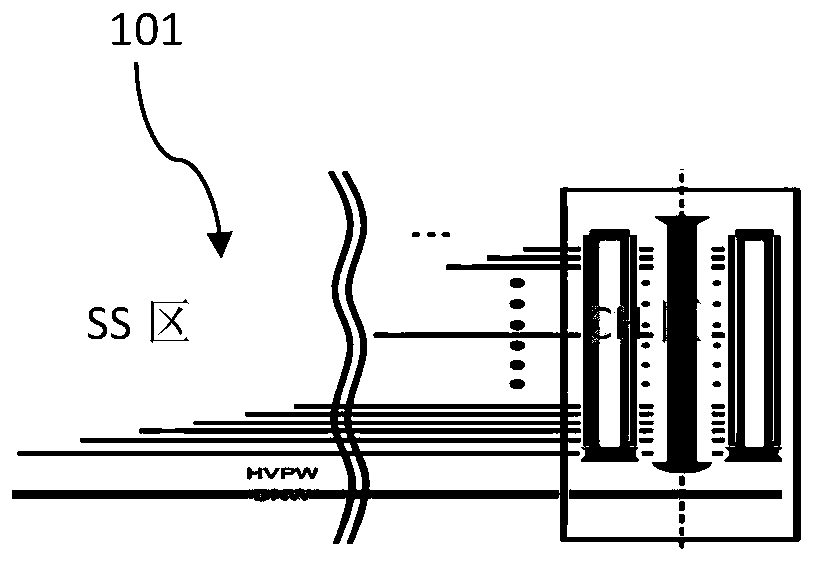

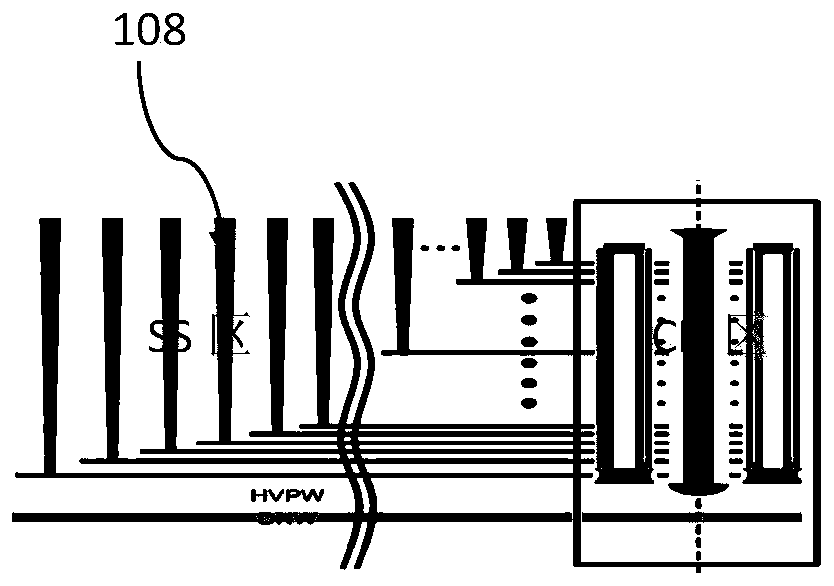

[0029] The technological process of the metal tungsten plug in the SS region of the present invention is the same as the aforementioned Figure 3(a)-3(d) The shown prior art process flow is similar, the difference is that the aforementioned silicon nitride layer is replaced by a silicon-rich silicon nitride layer, and the specific process flow is as follows Figure 7(a)-7(e) It includes the following steps: first, as shown in Figur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More