Semiconductor structures and methods of forming them

A semiconductor and work function layer technology, which is applied in semiconductor/solid-state device manufacturing, transistors, electrical components, etc., can solve the problems that the electrical properties of semiconductor structures need to be improved, so as to avoid undercut area defects, shorten the etching time, and improve the quality of side walls. good shape effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

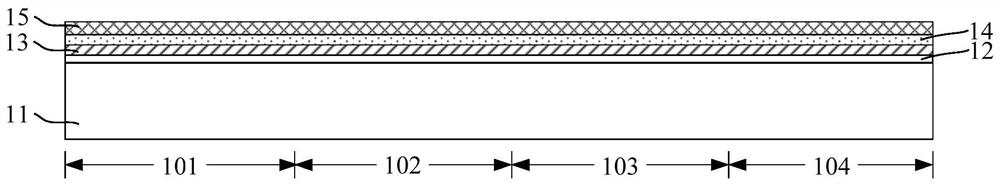

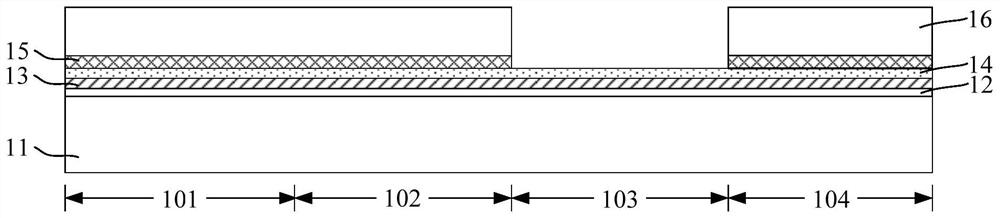

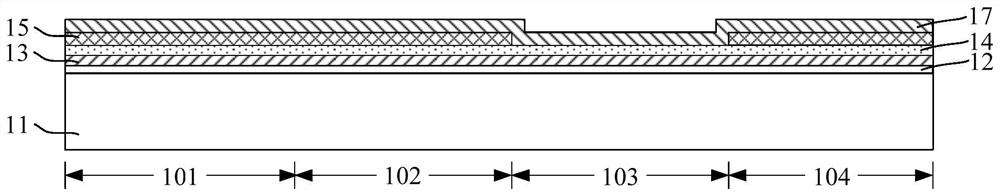

[0031]It can be seen from the background art that the electrical performance of the semiconductor structure formed in the prior art needs to be improved. Especially when the semiconductor structure includes P-type devices with different threshold voltages (Threshold Voltage) and N-type devices with different threshold voltages, the problem of poor electrical performance of the semiconductor structure is particularly significant.

[0032] In order to meet the requirements of NMOS tube and PMOS tube to improve the threshold voltage, different metal materials are usually used as the material of the work function (WF, Work Function) layer in the gate structure of the NMOS tube and the PMOS tube, and the work function layer in the NMOS tube The material may be referred to as an N-type work function material, and the work function layer material in the PMOS transistor may be referred to as a P-type work function material. When the NMOS transistor and the PMOS transistor share the sa...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| electron work function | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More