Methods and device of channel register initialization, DMA (Direct Memory Access) equipment and terminal

An initialization method and register technology, applied in the security field, can solve the problems of DMA devices being easily hijacked and affecting system security, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0066] In this embodiment, the channel register initialization method can be jointly executed by the CPU and the DMA device, combined below figure 2 The flow of the channel register initialization method is introduced:

[0067] S202: The CPU configures initialization information for channel registers in the direct memory access DMA device according to the data transfer task.

[0068] In this embodiment, the initialization information corresponding to the data moving task is delivered to the DMA device by the CPU. Therefore, whether it is a data transfer task from the CPU itself or a data transfer task for peripherals, the initialization information of the channel registers is configured by the CPU. In this embodiment, the initialization information is information used to indicate at least one of a source address and a destination address in each data migration task. For example, in some examples of this embodiment, the initialization information includes both the source add...

Embodiment 2

[0098] This embodiment will continue to introduce the flow of the channel register initialization method on the DMA device side on the basis of the first embodiment. Here, the data transfer instruction issued by the CPU is the real-time data transfer instruction, and the instruction interaction interface is the slave of the DMA device. machine interface as an example, please refer to Figure 7 :

[0099] S701: the slave interface receives a data transfer command from the bus;

[0100] S702: the slave machine interface judges whether the instruction buffer is full;

[0101] If the instruction buffer is full, the slave interface cannot buffer the received data transfer instruction into the instruction buffer, so if the judgment result is yes, execute S703; otherwise, execute S704.

[0102] S703: The slave machine interface feeds back information indicating that the DMA device is temporarily unable to respond to the CPU;

[0103] For example, in this embodiment, the slave inte...

Embodiment 3

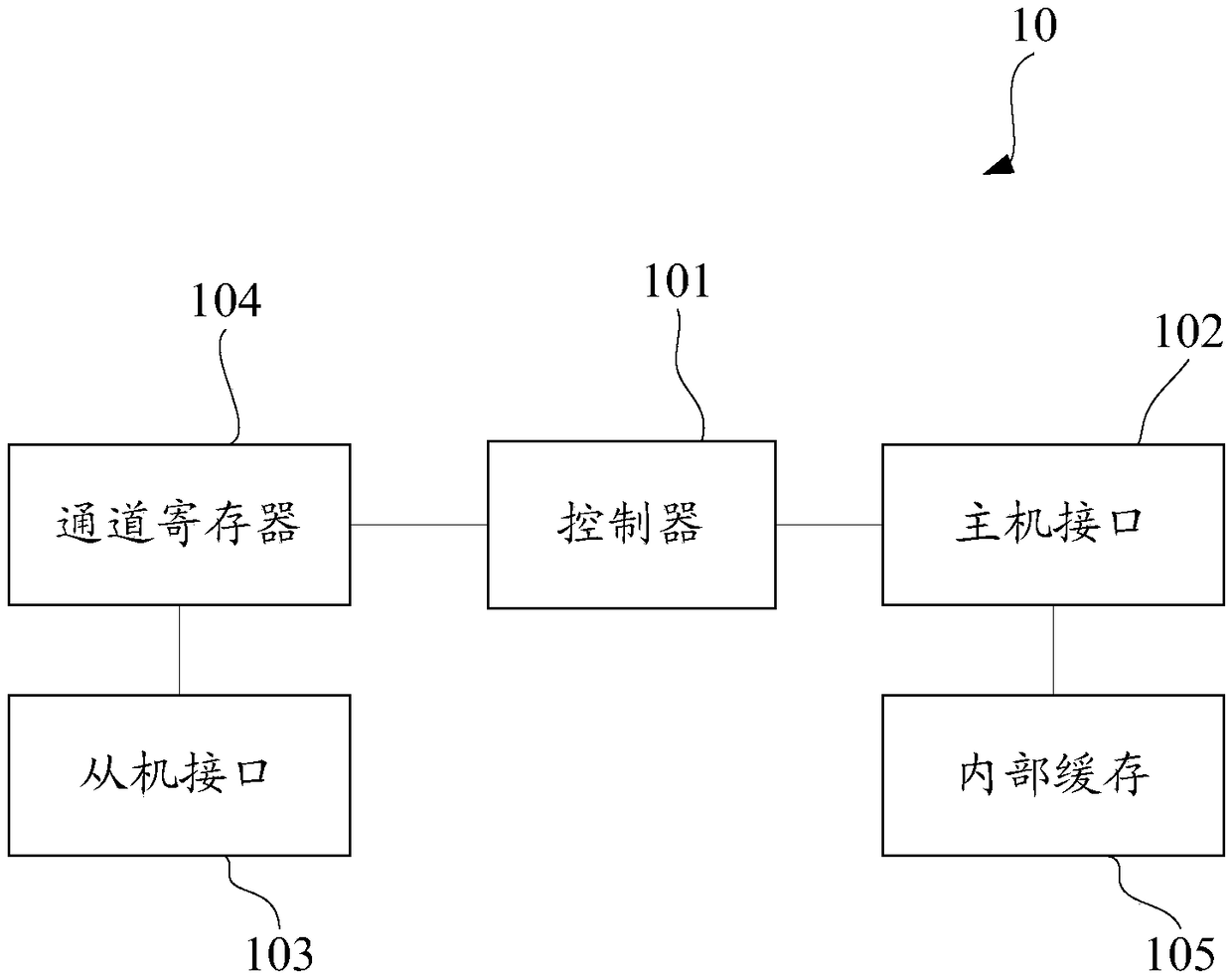

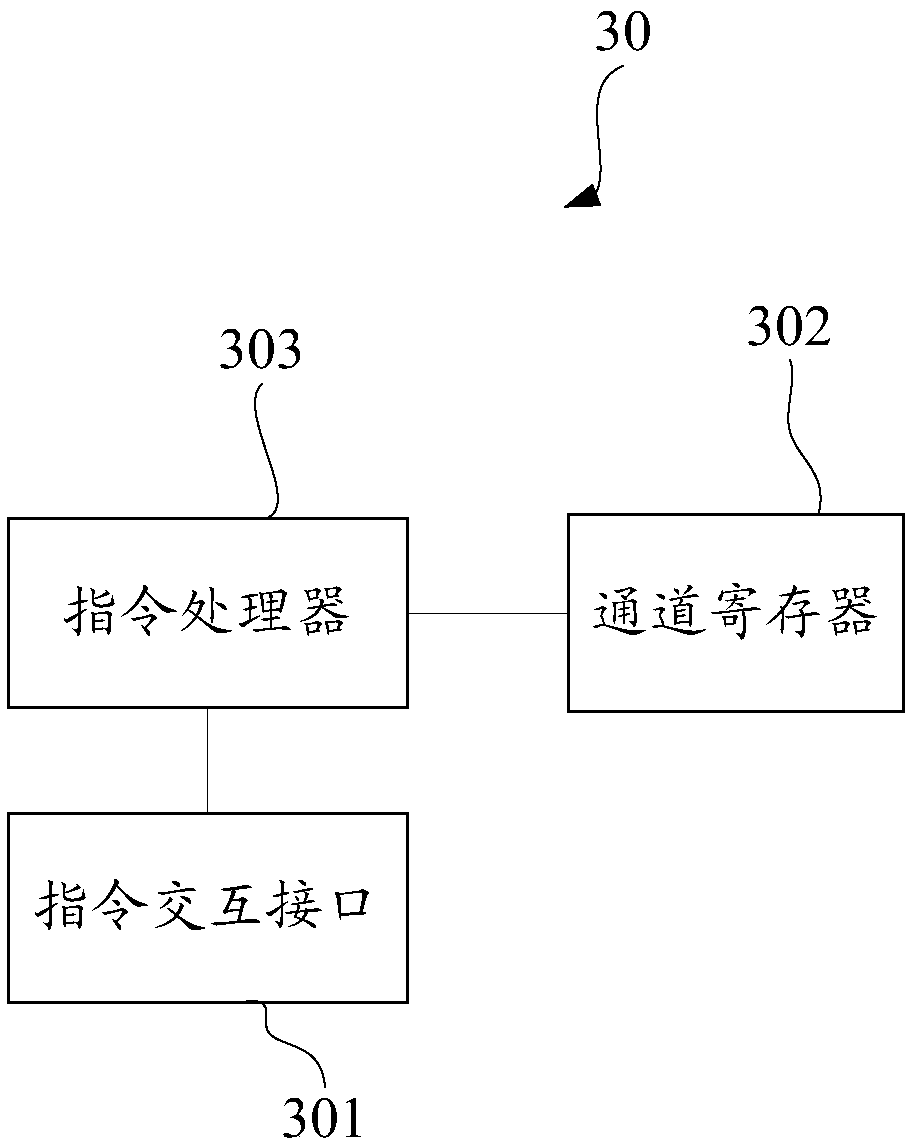

[0117] In order to solve the problem in the prior art that when the channel register in the DMA device is initialized, the initialization information is directly transmitted, causing the DMA device to be easily hijacked by a malicious attacker, thereby moving the data specified by the malicious attacker and threatening the security of the system, this embodiment provides a DMA device that combines the following Figure 8 with Figure 9 The structure of the DMA device and the initialization process of the channel register in the DMA device are introduced:

[0118] The DMA device 80 includes a slave interface 801 , an instruction buffer 802 , an instruction processor 803 , a channel register 804 , a peripheral information register 805 , a controller 806 , a host interface 807 , and an internal cache 808 . The slave interface 801 is communicatively connected with the instruction register 802 . The instruction buffer 802 can be used to store the data movement instruction receive...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More