Accelerating circuit of 3*3 convolution algorithm

A technology for accelerating circuits and convolution operations, applied in image memory management, processor architecture/configuration, etc., can solve the problems of consuming software instructions, inefficiency, and occupying software resources, so as to save bandwidth, reduce time consumption, and process image complete effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings:

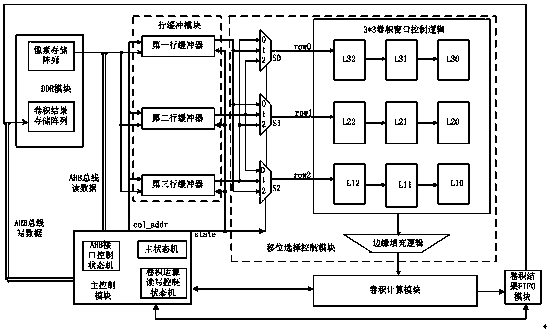

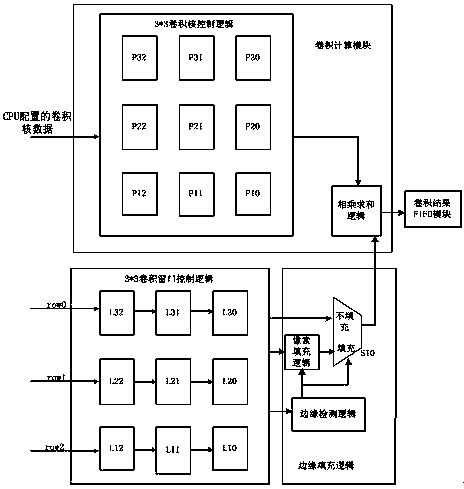

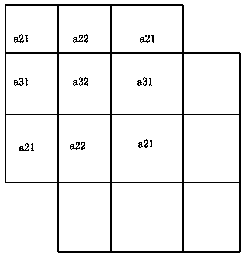

[0022] The concept of the invention is: in the process of traversing the input source image, the window of the 3*3 convolution kernel stores the pixels from the input source image stored in the DDR or SRAM through three single-port 1KB line buffer SRAM buffers, and uses the state machine to store the pixels of the input source image. and the column address count value to realize the sliding of the center pixel of this window in the input source image to complete the matrix convolution operation, then write the result of the convolution operation into the 16-layer 8-bit FIFO, and finally use the AHB bus to transfer the data in the FIFO Write back the DDR and send an interrupt to the CPU, enabling hardware-accelerated convolution calculations.

[0023] Based on the above inventive concept, an embodiment of the present invention provides an acc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com