Server chip debugging circuit, debugging method and server

A technology for debugging circuits and debugging methods, which is applied in the direction of faulty hardware testing methods, instruments, and electrical digital data processing, etc., which can solve the problems of increased manufacturing costs, cumbersome operations, and high costs of servers, and achieve improved space utilization, reduced costs, and Effect of saving board space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

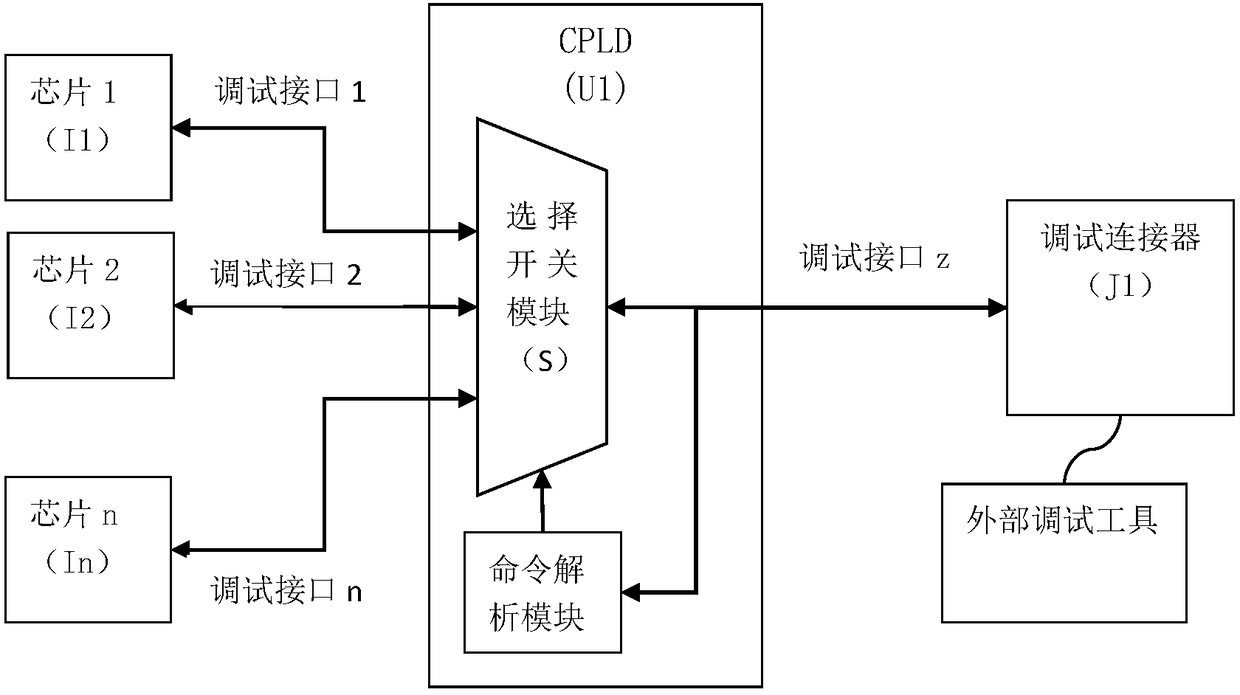

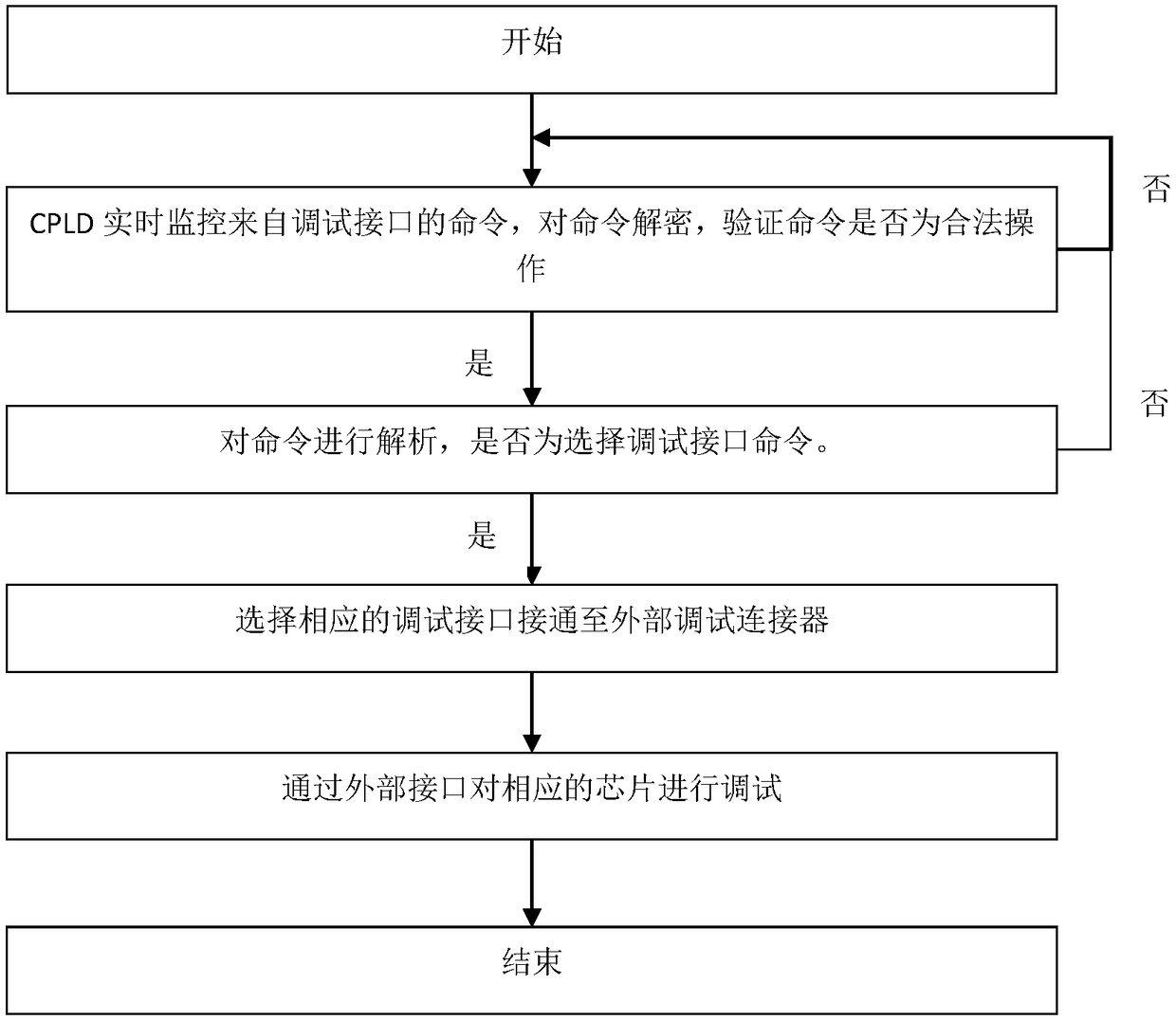

[0022] Such as figure 1 As shown, a server chip debugging circuit includes: a debugging control unit U1, n chips to be debugged (I1, I2, . . . , In) and a debugging connector J1. In this embodiment, the debugging control unit is specifically a CPLD chip.

[0023] The debugging control unit includes a selection switch module S and a command analysis module. One end of the selection switch module is respectively connected to the debugging interfaces (debugging interface 1, debugging interface 2, . . . , debugging interface n) of the plurality of debugged chips through the first interface. In this embodiment, the debugging interface 1, the debugging interface 2, . . . , the debugging interface n, and the debugging interface z are specifically I2C protocol interfaces.

[0024] The other end of the selection switch module is connected to the debugging connector through the debugging interface z. The command parsing module is used for accepting the commands of the debugging inter...

Embodiment 2

[0029] The difference between this embodiment and Embodiment 1 is that in this embodiment, the debugging interface 1, the debugging interface 2, . . . , the debugging interface n are I2C protocol interfaces. The debugging interface z is a UART protocol interface. The debugging control unit includes a protocol conversion module, which realizes the conversion between the I2C protocol interface and the UART protocol interface of the debugging interface z. Through the protocol conversion module, the optional range of protocols on both sides of the debugging control unit is increased.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More