Power device and encapsulation method thereof

A technology of power devices and packaging methods, which is applied in the direction of electric solid-state devices, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of low thermal diffusion efficiency of chips, increase of manufacturing costs, and product failure, so as to reduce manufacturing costs, Improved integration and better packaging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

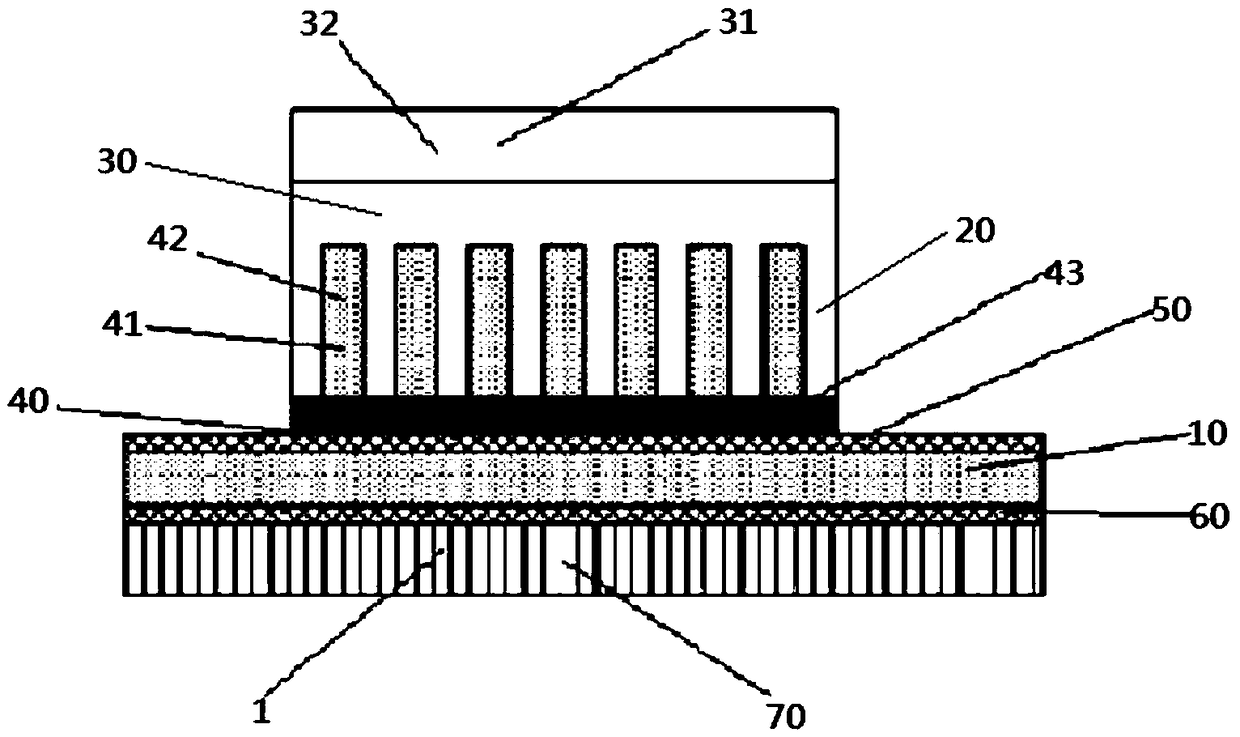

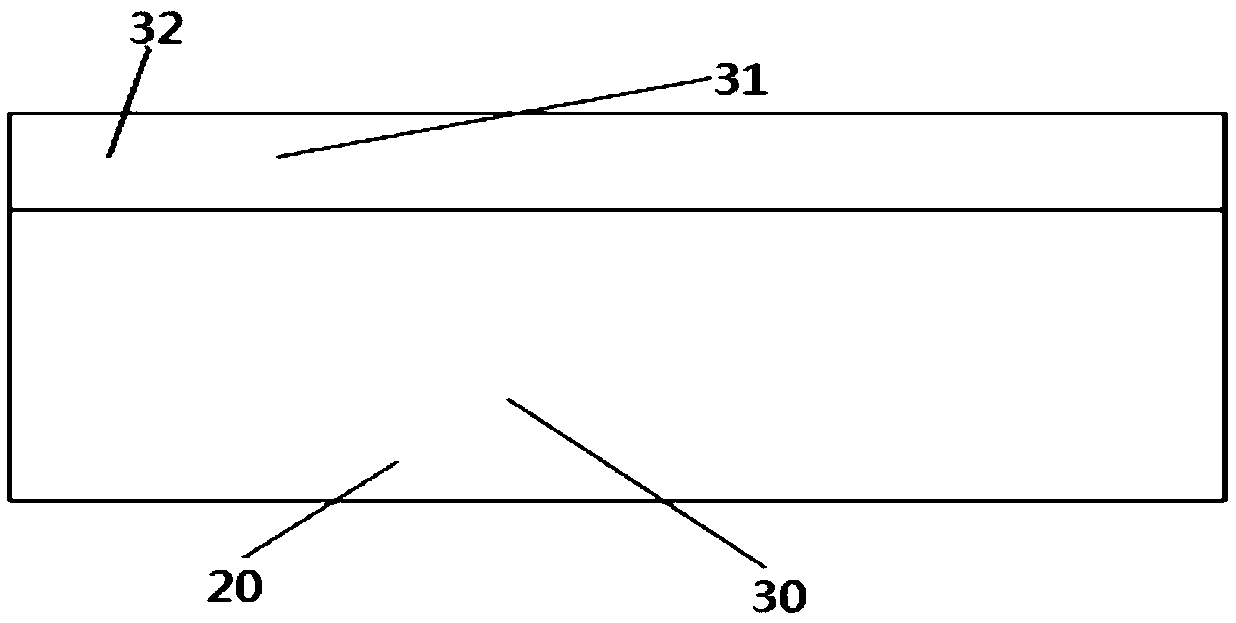

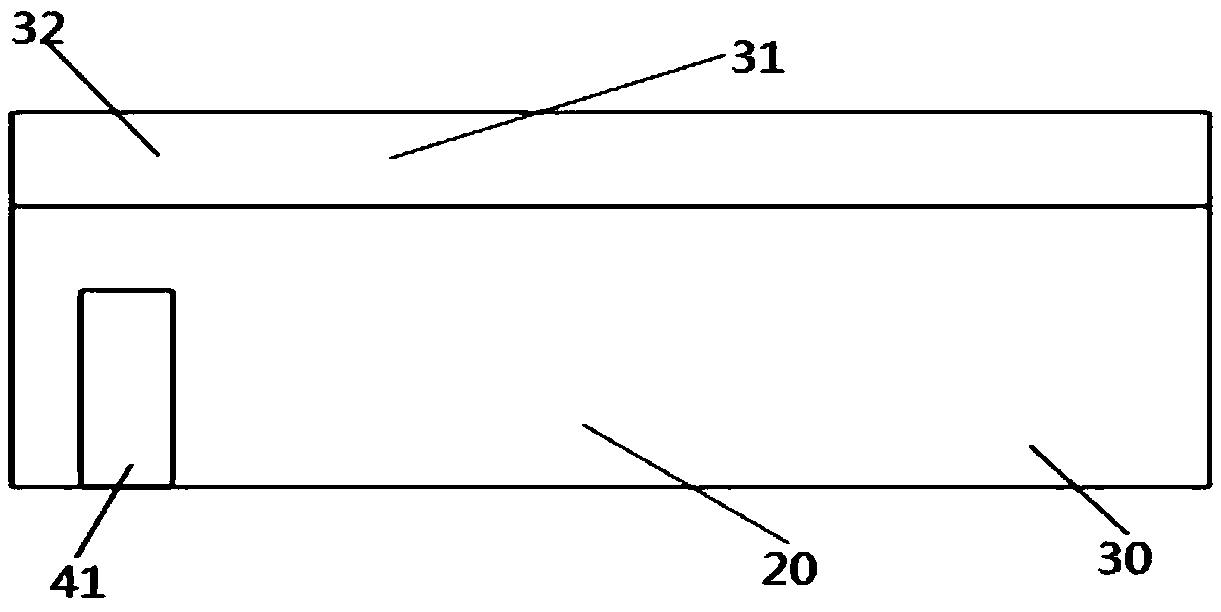

[0020] In order to understand the specific technical solutions, features and advantages of the present invention more clearly, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0021] In the description of the present invention, it should be noted that the terms "upper", "lower", "left", "right", "transverse", "longitudinal", "horizontal", "inner", "outer" etc. indicate The orientation or positional relationship is based on the orientation or positional relationship shown in the drawings, or the orientation or positional relationship that is usually placed when the product of the invention is used, and is only for the convenience of describing the present invention and simplifying the description, rather than indicating or implying the It should not be construed as limiting the invention that a device or element must have a particular orientation, be constructed, and operate in a particular ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More