Realization Method of Wideband Digital Predistorter

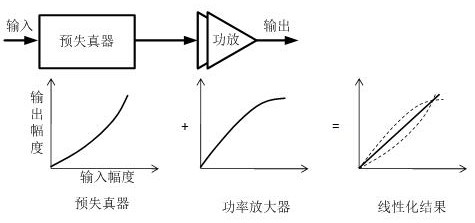

A technology of digital pre-distortion and implementation method, which is applied in the field of wireless communication, can solve the problems of model input and output timing design difficulties, FPGA cannot realize digital pre-distorter, high-speed multiplier and adder cannot be realized, etc., so as to reduce the system processing rate , low complexity, wide linearization bandwidth effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

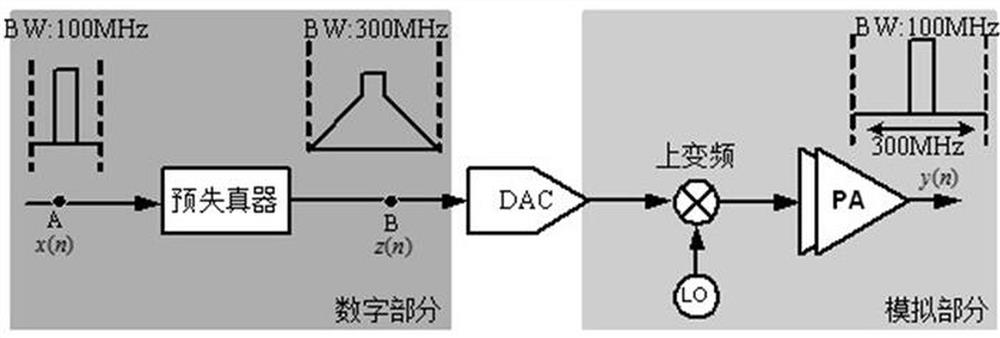

[0046] As a preferred embodiment of the present invention, with reference to the attached Figure 1-5 , this example discloses:

[0047] A method for realizing a wideband digital predistorter, comprising the steps of:

[0048] Step A, obtaining the feedback signal y(n) of the power amplifier, expressed as:

[0049]

[0050] Where y(n) is the output of the power amplifier model, x(n) is the input of the power amplifier model, b km is the coefficient of the power amplifier model, K and M are the nonlinear order and memory depth of the model respectively;

[0051]Step B, observe whether there is spectrum expansion in y(n), and judge whether it is linear, if the spectrum of y(n) does not expand, then the linear effect converges, and directly enter step G; if the spectrum of y(n) expands, Then nonlinear distortion occurs, the linear effect does not converge, and enters step C;

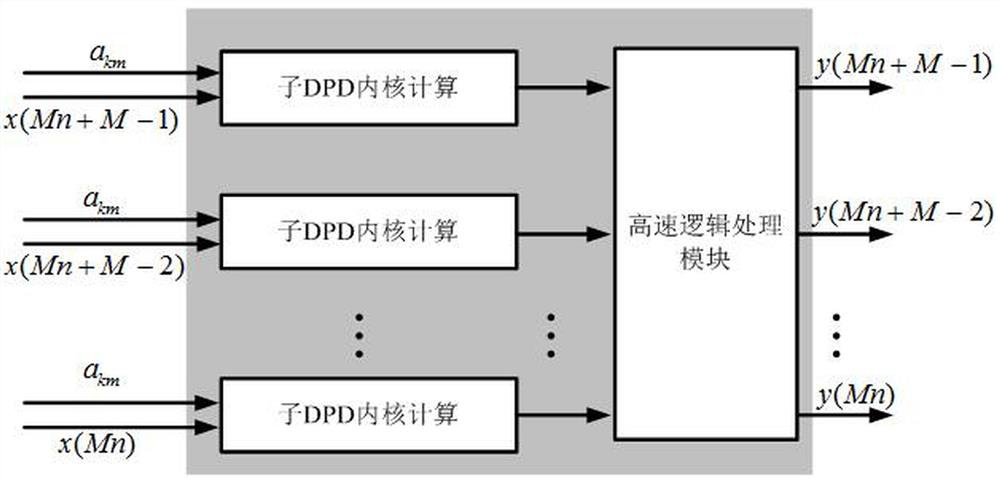

[0052] Step C, decomposing the memory polynomial model of the power amplifier model in step A int...

Embodiment 2

[0070] As another preferred embodiment of the present invention, with reference to the attached Figure 1-5 , this example discloses:

[0071] A method for realizing a wideband digital predistorter, comprising the following steps:

[0072] Step A, obtain the feedback signal y(n) of the power amplifier by the ADC acquisition card, express as:

[0073]

[0074] where y(n) is the output of the power amplifier model, x(n) is the input of the power amplifier model, b km is the coefficient of the power amplifier model, K and M are the nonlinear order and memory depth of the model respectively;

[0075] Step B. Observe whether y(n) has spectrum expansion through the spectrum analyzer to judge whether it is linear. If the spectrum of y(n) does not expand, it means that the linear effect is converged, and then directly enter step G; if y(n) ) has expanded, indicating that nonlinear distortion has occurred, and the linear effect has not converged, and enters step C;

[0076] Step...

Embodiment 3

[0094] Such as Figure 6 as shown, Figure 6 It is the linearization result diagram of the actual measurement of the power amplifier in the implementation case of the proposal of this application. This implementation case predistorts 64QAM with a symbol rate of 100Msps and a bandwidth of 125MHz. The traditional predistorter requires a working frequency of 750MHz, which cannot be implemented in FPGA. However, this implementation case decomposes the predistorter model into 8 channels. DPD core parallel computing, the required baseband clock can be reduced to 750 / 8 = 93.75MHz, which greatly reduces the operating frequency of FPGA. From Figure 6 It can be seen that the broadband digital predistorter in this implementation case has good linearization capability.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More