c 2 mos trigger

A technology of flip-flops and inverters, applied in electric pulse generator circuits, bipolar transistors to generate pulses, etc., can solve the problems of inability to achieve high-speed operation data integrity, limited operating frequency, etc., and achieve a small number, leakage and power consumption. Low, cost-saving effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

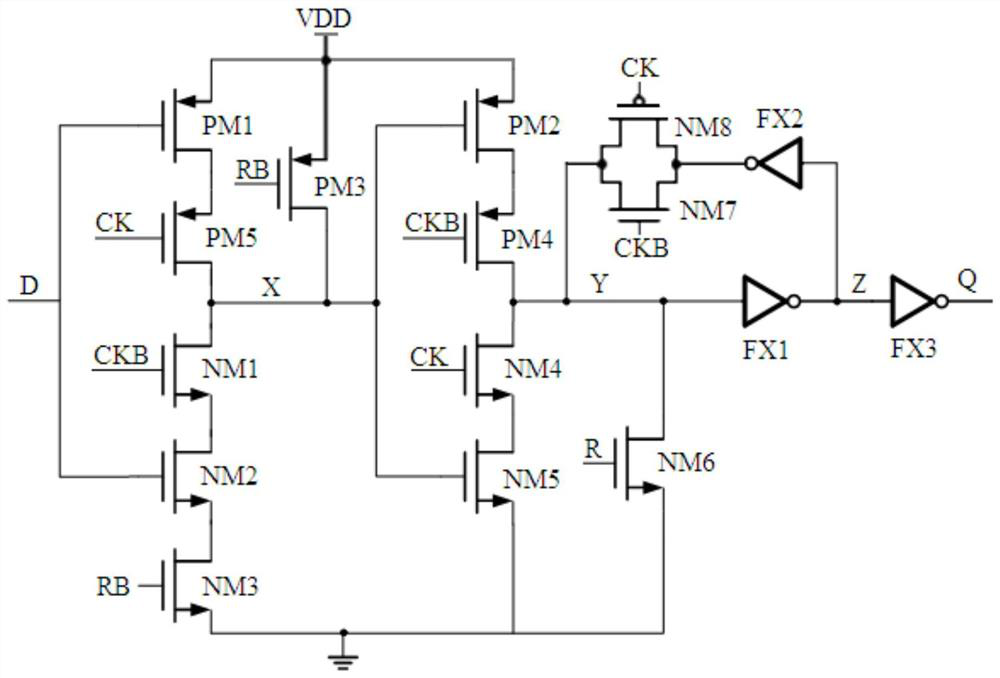

[0019] see figure 2 As shown, in the following embodiment, the C2MOS flip-flop includes: five PMOS transistors PM1-PM5, eight NMOS transistors NM1-NM8 and three inverters FX1-FX3.

[0020] The sources of the PMOS transistors PM1 to PM3 are connected to the power supply voltage terminal VDD, the drain of the PMOS transistor PM1 is connected to the source of the PMOS transistor PM5, the drains of the PMOS transistors PM5 and PM3 are connected to the drain of the NMOS transistor NM1, and the PMOS transistor The gate of PM2 is connected to the gate of NMOS transistor NM5, and the connected node is denoted as X.

[0021] The NMOS transistor NM2 and the NMOS transistor NM3 are connected in series between the source of the NMOS transistor NM1 and the ground.

[0022] The gate of the PMOS transistor PM1 and the gate of the NMOS transistor NM2 are used as the input terminal D of the flip-flop, and the gate of the PMOS transistor PM3 and the gate of the NMOS transistor NM3 input an in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More