A reliability evaluation method for nano-integrated circuits under the influence of multiple transient faults

An integrated circuit and reliability technology, which is applied in the field of reliability evaluation of nano-integrated circuits under the influence of multiple transient faults. Insufficient degree and other problems, to achieve the effect of good scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

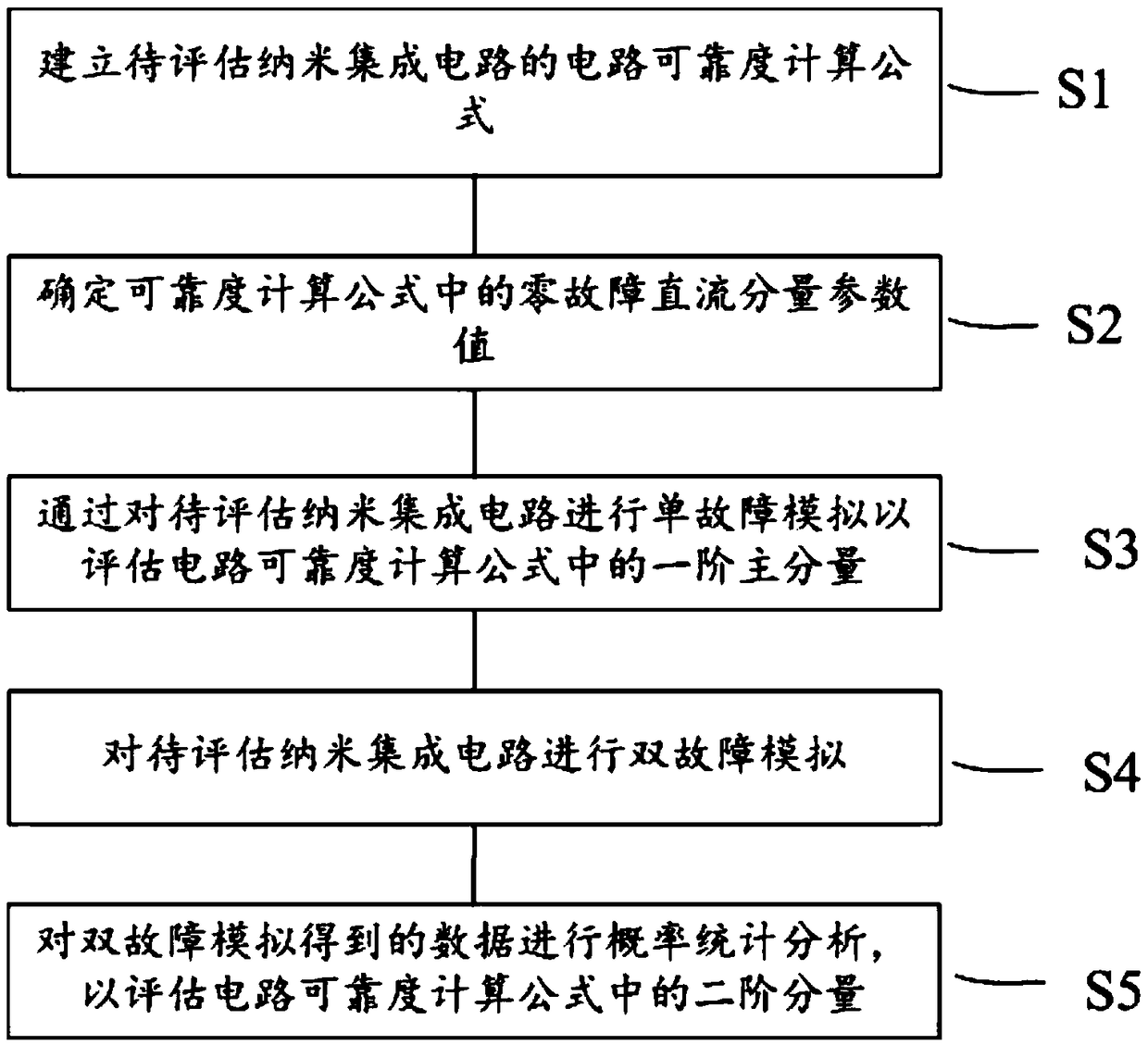

[0029] In order to make the content of the present invention more clear and understandable, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

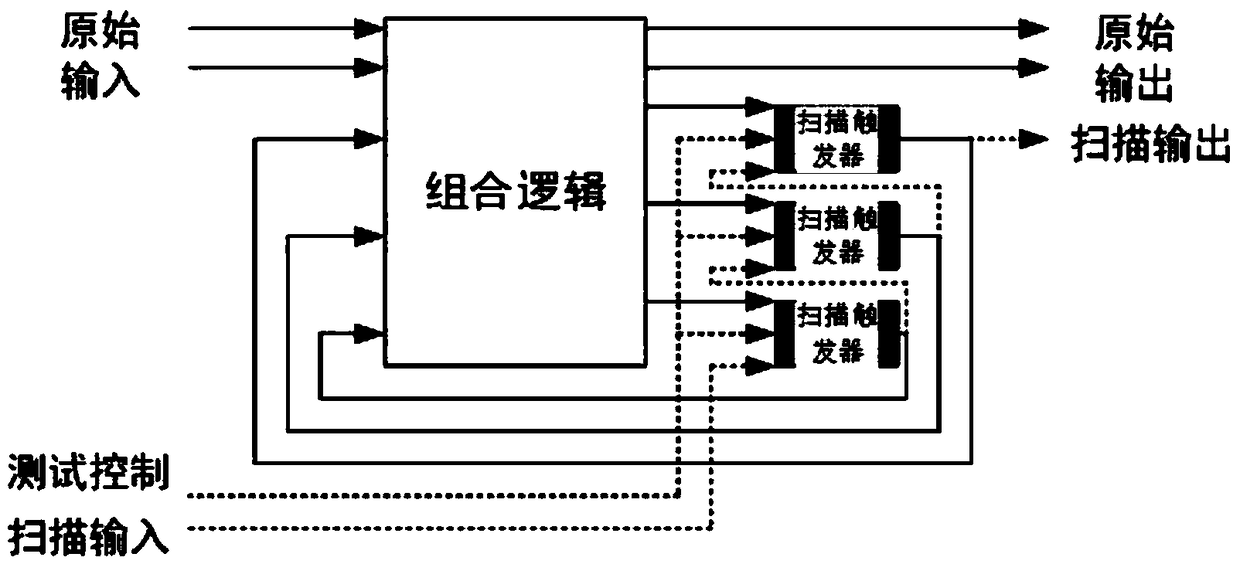

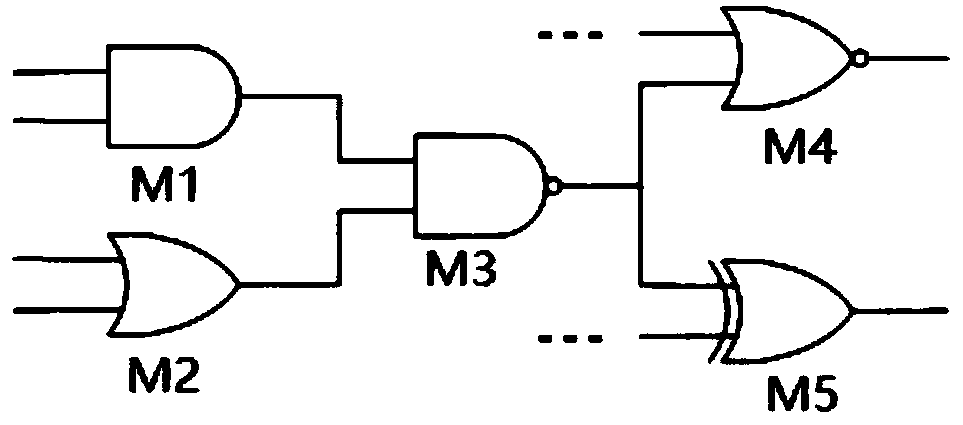

[0030]In the reliability research of logic circuits, the widely used probability gate model means that each logic gate in the circuit has the same correct output probability when it is affected by the space radiation environment. Considering the actual manufacturing process of the gate circuit, it can also be considered that the correctness of the output of the logic unit due to particle impact is independent of each other. Based on this model, the correct output of a single logic unit of the circuit under the influence of the external environment is regarded as a random event, and the probability of the number of faulty logic units in the circuit being a certain value obeys the binomial distribution. This method mainly studies combinational circui...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More