Wafer structure

A wafer and layer structure technology, applied in electrical components, circuits, semiconductor devices, etc., can solve problems such as complicated cutting procedures, inability to shrink process patterns, and residual process patterns.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] Some terms are used in the description and claims to refer to specific components. However, those with ordinary knowledge in the technical field of the present invention should understand that manufacturers may use different terms to refer to the same component. Moreover, this specification And the claims do not use the difference in name as the way to distinguish components, but the difference in the overall technology of the components as the criterion for distinguishing. "Includes" mentioned throughout the specification and claims is an open term, so it should be interpreted as "including but not limited to".

[0043] In order to make the structural features of the present invention and the achieved effects have a further understanding and recognition, preferred embodiments and detailed descriptions are specially used, which are described as follows:

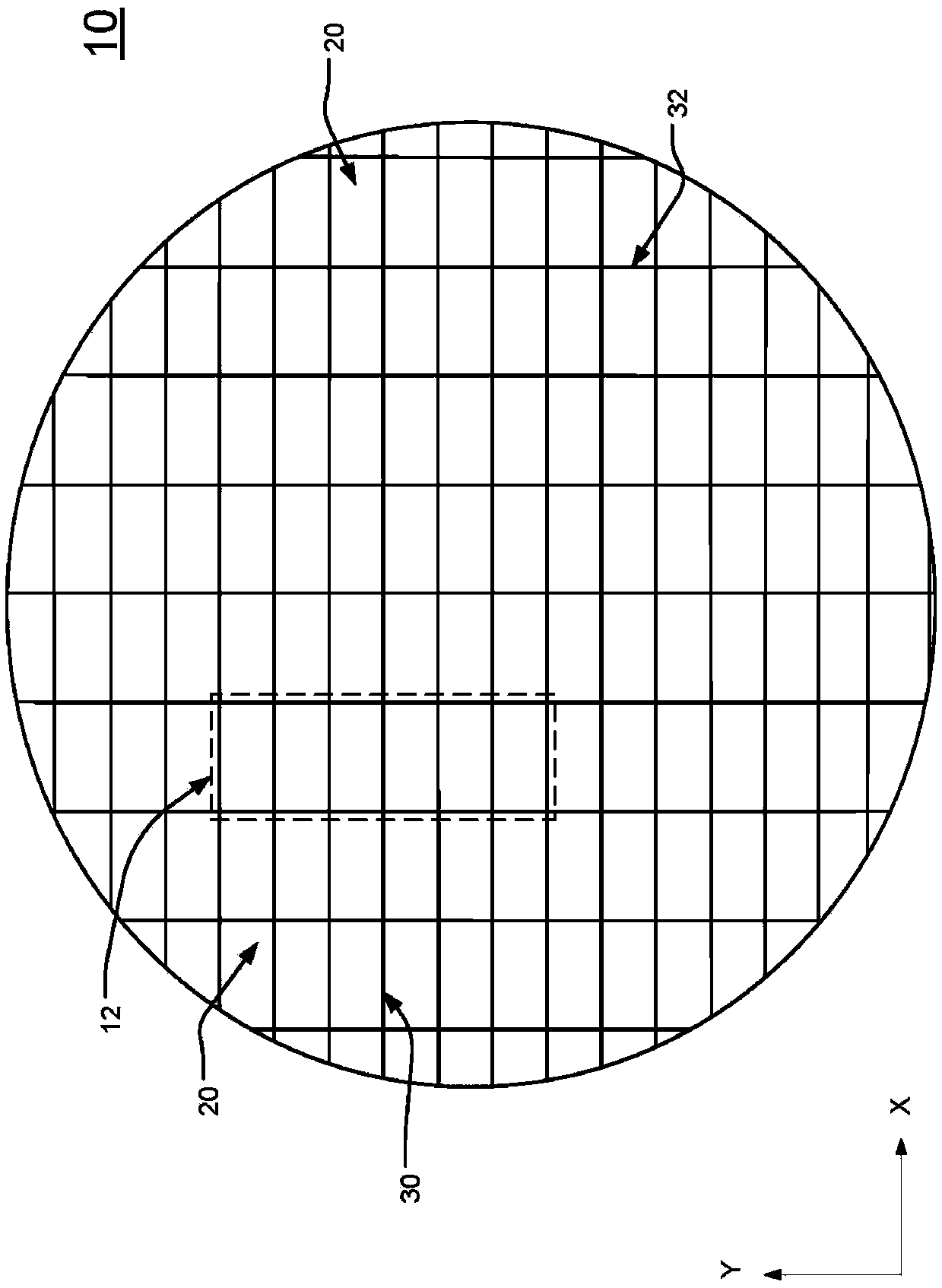

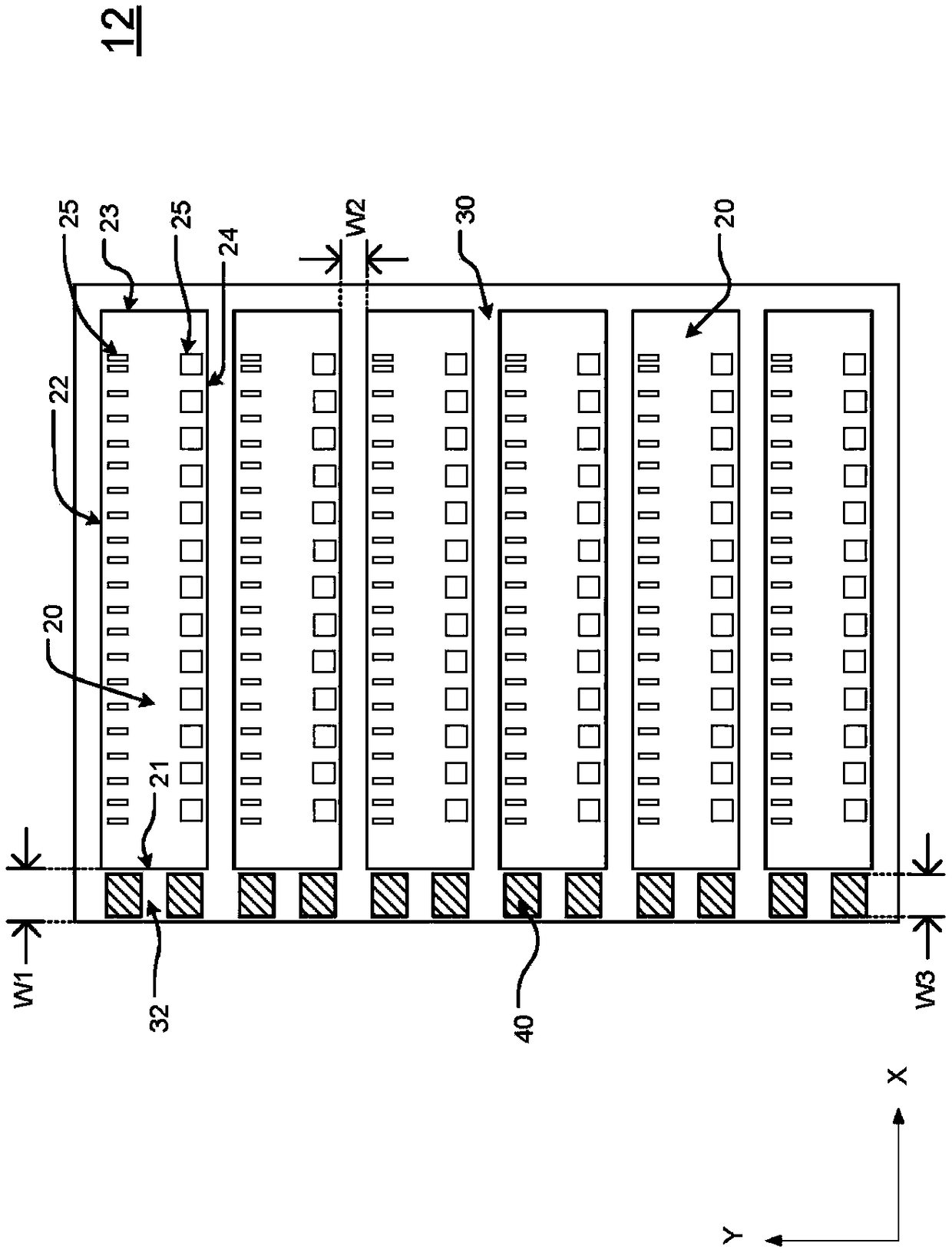

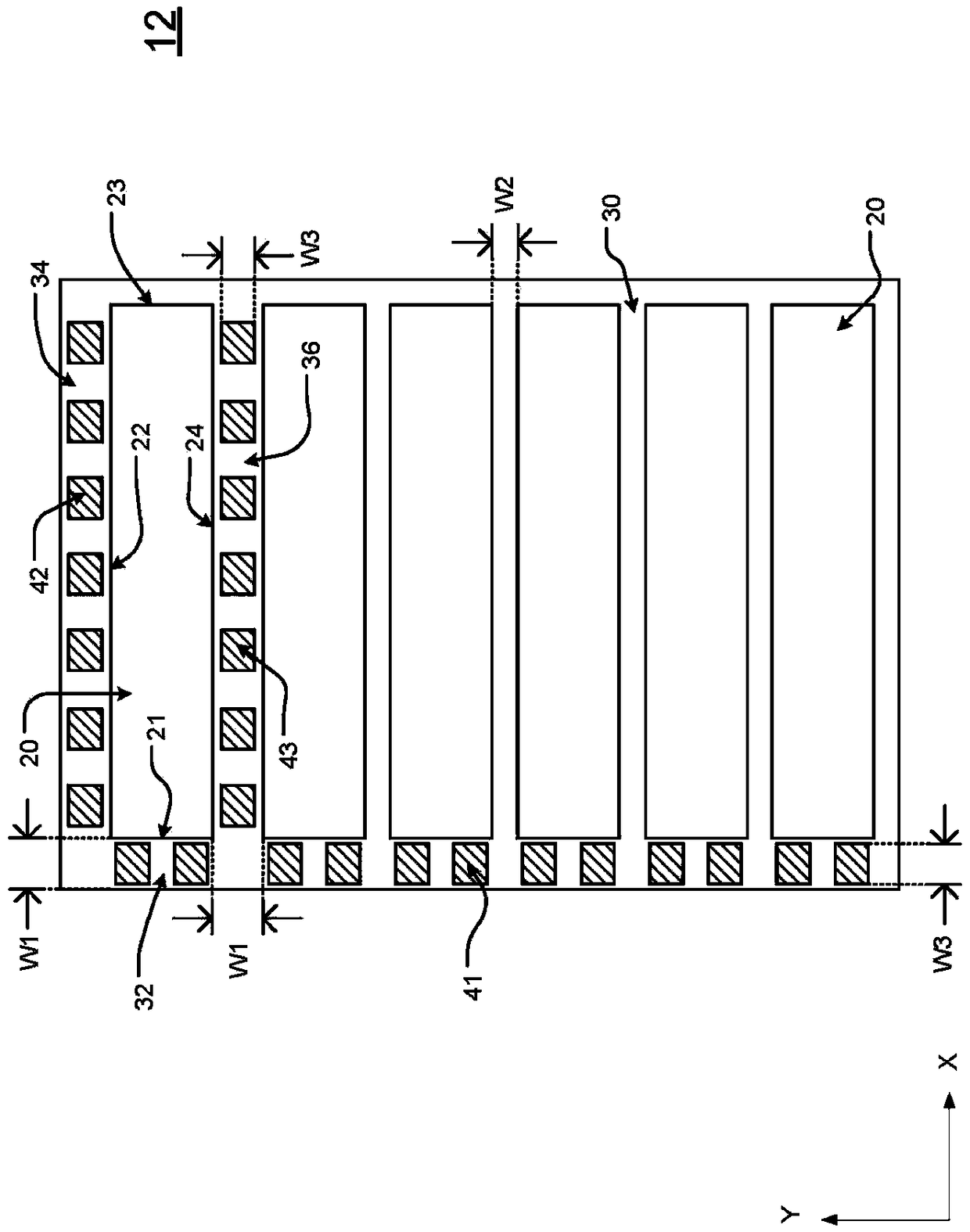

[0044] see figure 1 , which is a schematic diagram of an embodiment of the wafer structure of the present invention...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More