Time performance test method of embedded real-time operating system based on FPGA

A real-time operating system and time performance technology, applied in software testing/debugging, error detection/correction, instruments, etc., can solve the problems of system scheduling CPU time occupation, affecting test accuracy, poor flexibility, etc., to improve test accuracy and improve Flexibility, reduced syscall and signal latency effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

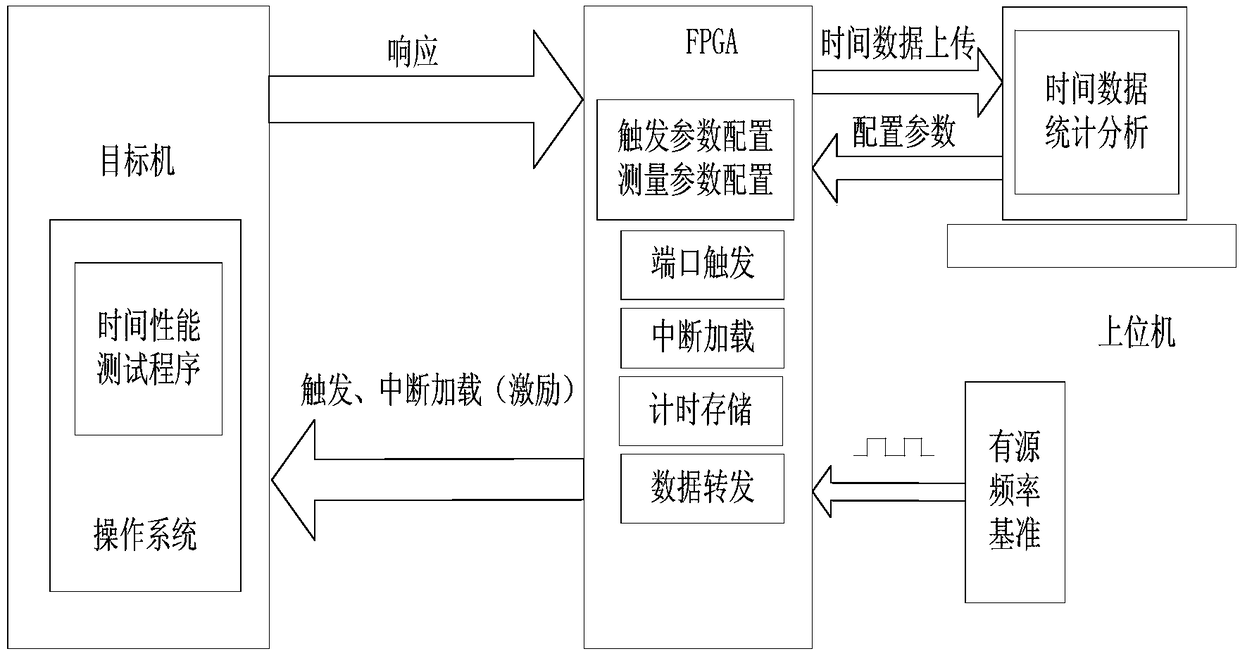

[0078] This embodiment specifically describes the method for testing the time performance index of the embedded real-time operating system using FPGA proposed by the present invention. The detection method is applied to the interrupt response time performance test of an embedded real-time operating system.

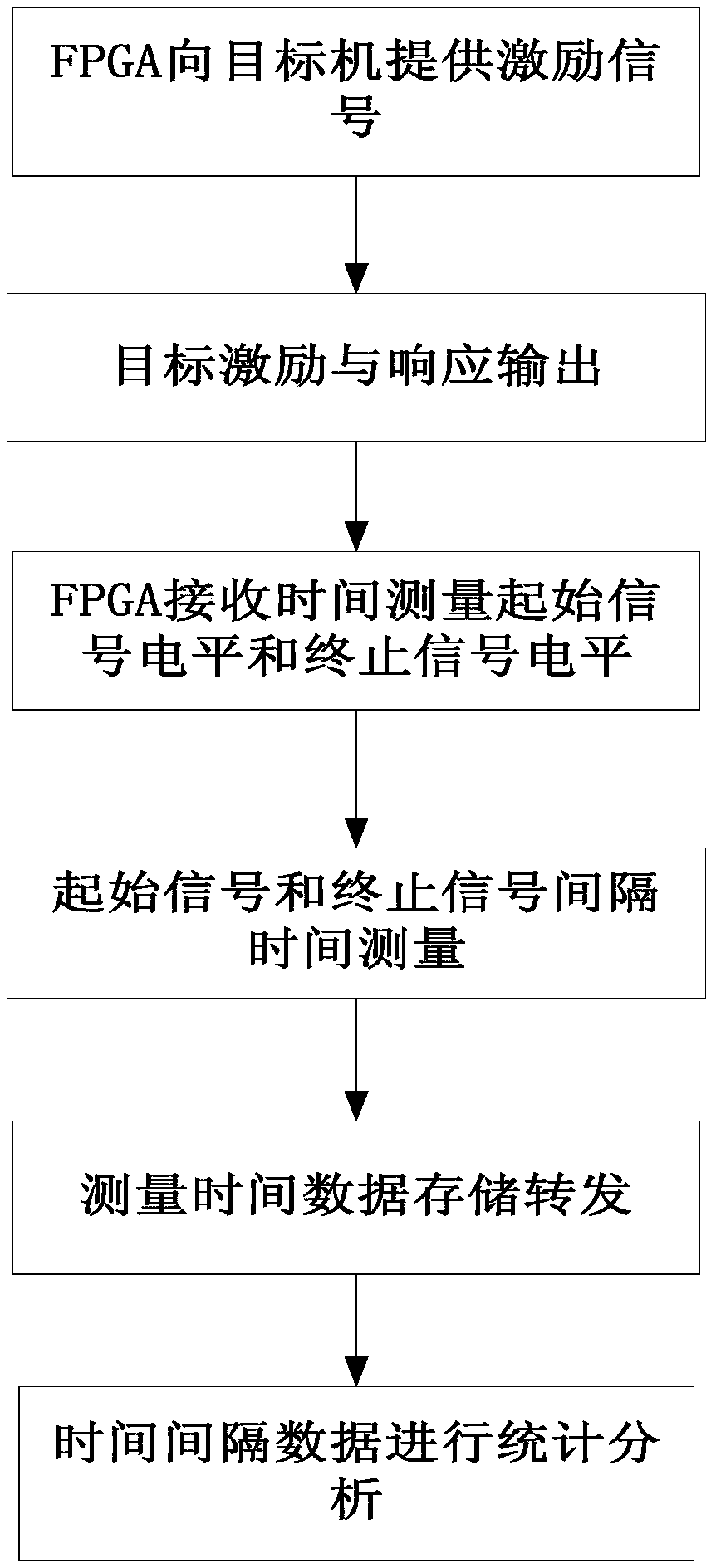

[0079] like figure 1 Shown, described time testing method comprises the steps:

[0080] Step 1: The FPGA provides an excitation signal to the target machine, and the input excitation signal here is the external interrupt source of the target machine. Step 1 consists of the following steps:

[0081] Step 101, setting frequency f, signal duration t, and trigger times n of the interrupt trigger signal at the host computer to determine the interrupt input source parameters of the target machine;

[0082] Step 102, sending the excitation input source configuration parameters to the FPGA

[0083] Step 103, the FPGA outputs an interrupt signal to the target machine according ...

Embodiment 2

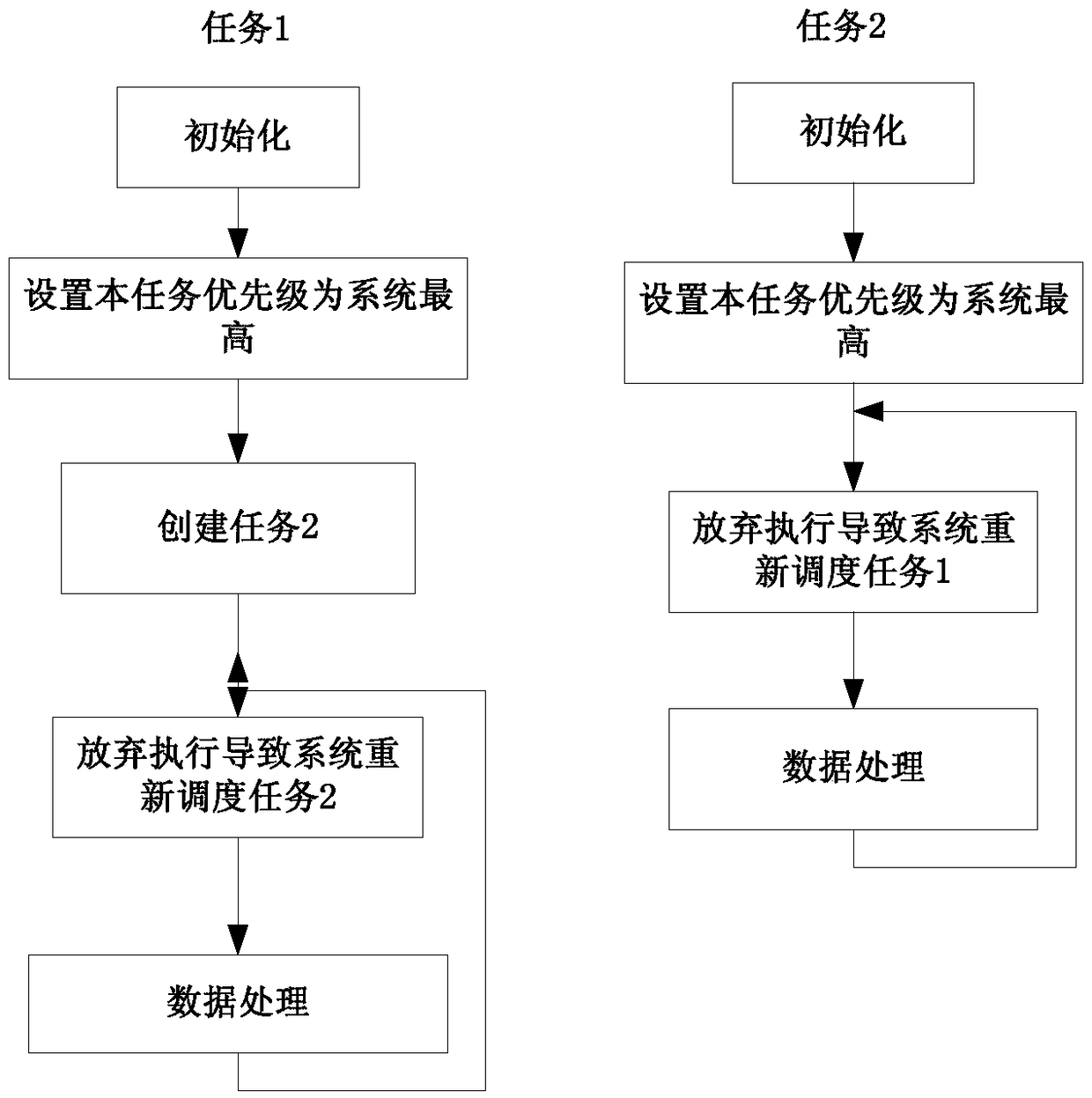

[0095] This example specifically describes the method for testing the time performance index of the embedded real-time operating system using FPGA proposed by the present invention. The detection method is applied to the task switching time performance test of an embedded real-time operating system.

[0096] Described time performance test method comprises the steps:

[0097] Step 1: Configure task switching time test measurement parameters and set the number of measurements;

[0098] Step 2: Run the time performance test program on the target machine, and output the start signal level and the end signal level of the measurement time;

[0099] Both the start level signal and the end level signal to be output during task switching time performance measurement are timely output by the test program. like image 3 Shown:

[0100] (1) Create two tasks 1 and 2 with the same priority. In order to avoid the influence of other tasks in the system, give these two tasks the highest p...

Embodiment 3

[0112] This embodiment provides a method for testing the time performance index of an embedded real-time operating system using FPGA, and the detection method is applied to the time performance test of the embedded real-time operating system.

[0113] Described time performance test method comprises the steps:

[0114] Step 1: FPGA provides excitation signal to the target machine;

[0115] Step 2: The target machine responds to the stimulus and outputs a response signal, and outputs the start signal level and end signal level of the measurement time;

[0116] Step 3: the FPGA receives the output of the target machine to measure the start signal level and the end signal level;

[0117] Step 4: FPGA uses its own time base to count, and measures the time interval between the start signal level and the end signal level;

[0118] Step 5: FPGA stores and forwards the measured multiple sets of time interval data to the host computer;

[0119] Step 6: The host computer performs sta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More