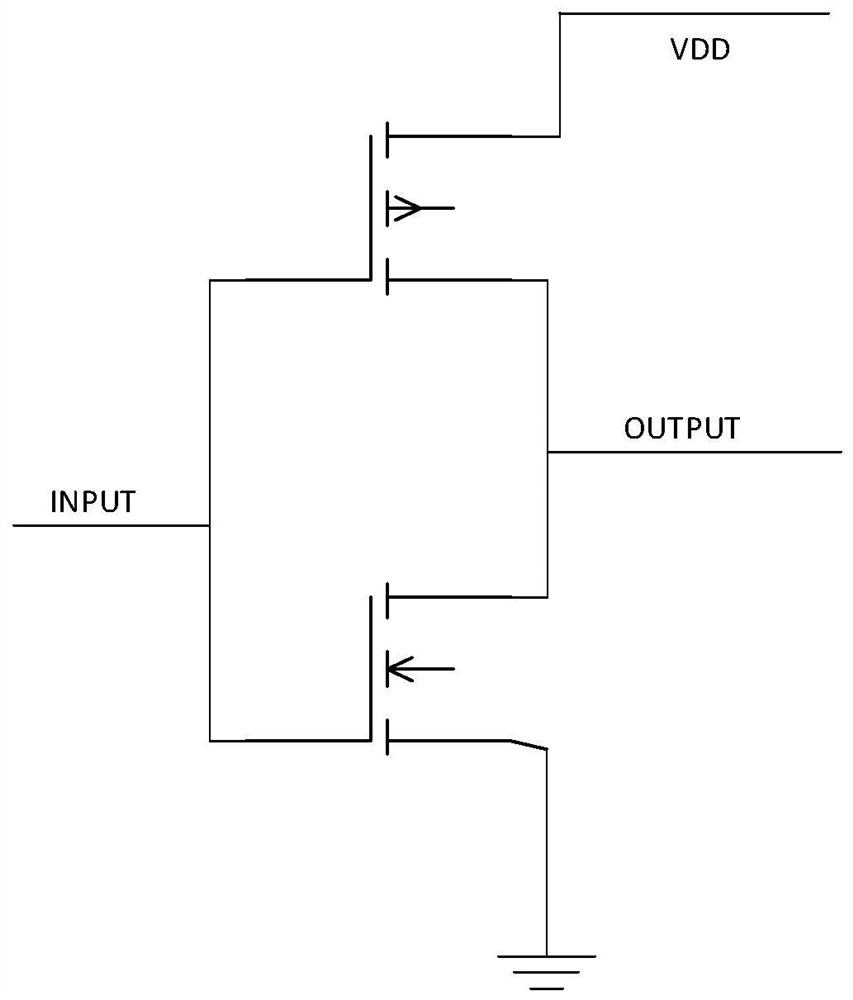

A graphene-based tunneling transistor, inverter and preparation method thereof

A technology of tunneling transistors and graphene, applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of difficulty in meeting the requirements of response speed of digital logic circuits, low saturation motion speed, etc., to achieve protection quality, improve Overall gain, the effect of prolonging the working life

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

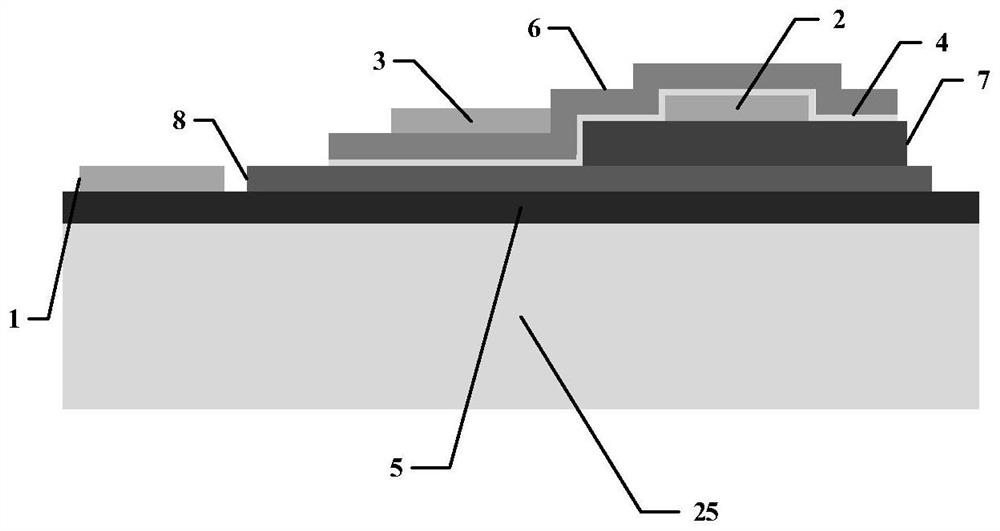

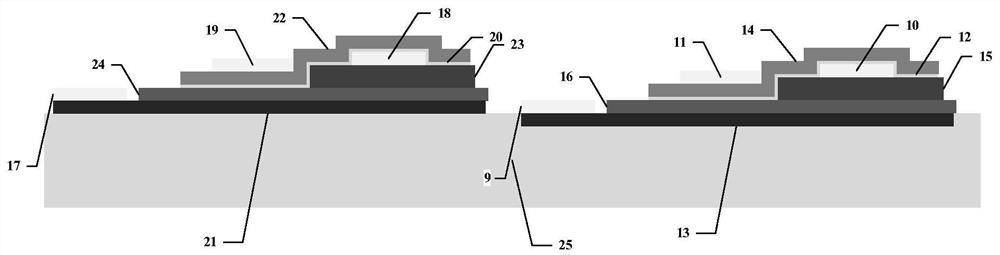

[0030] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

[0031] Those skilled in the art will understand that unless otherwise stated, the singular forms "a", "an", "said" and "the" used herein may also include plural forms. It should be further understood that the word "comprising" used in the description of the present invention refers to the presence of said features, integers, steps, operations, elements and / or components, but does not exclude the presence or addition of one or more other features, Integers, steps, operations, elements, components, and / or groups thereof. It will be unders...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| electron work function | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More