Patents

Literature

30results about How to "No additional process steps required" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

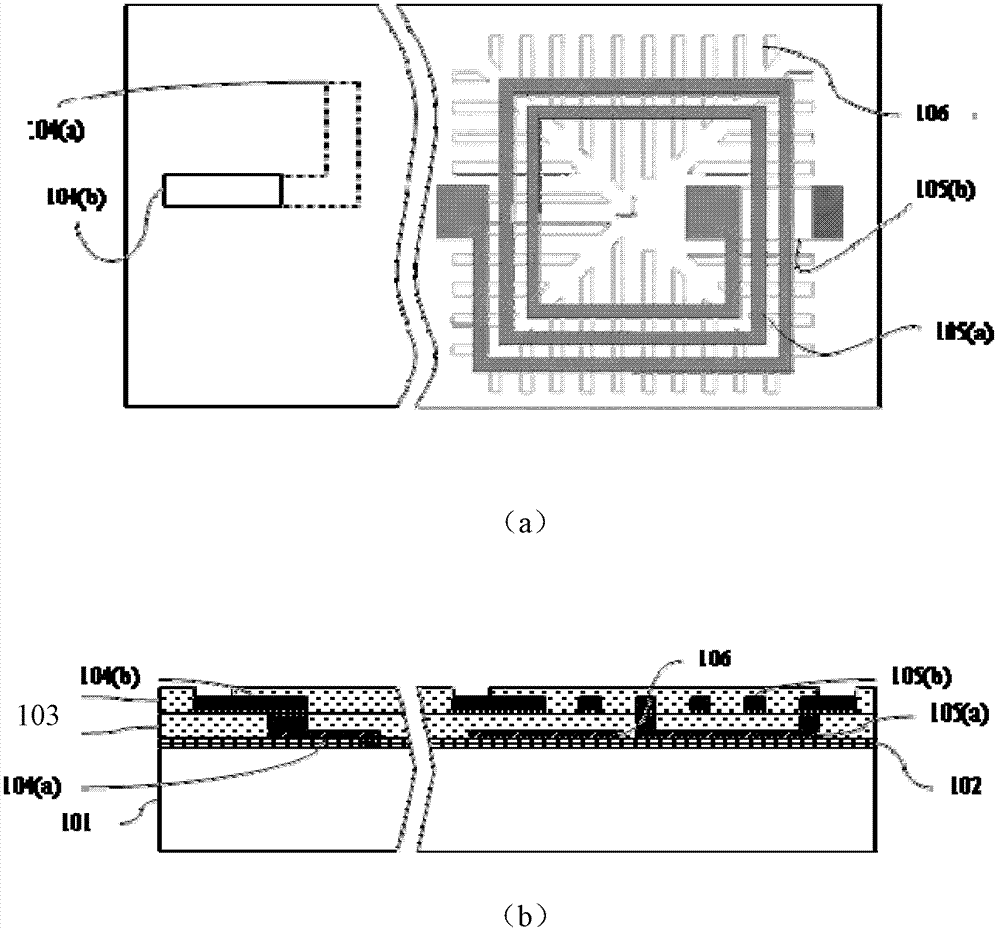

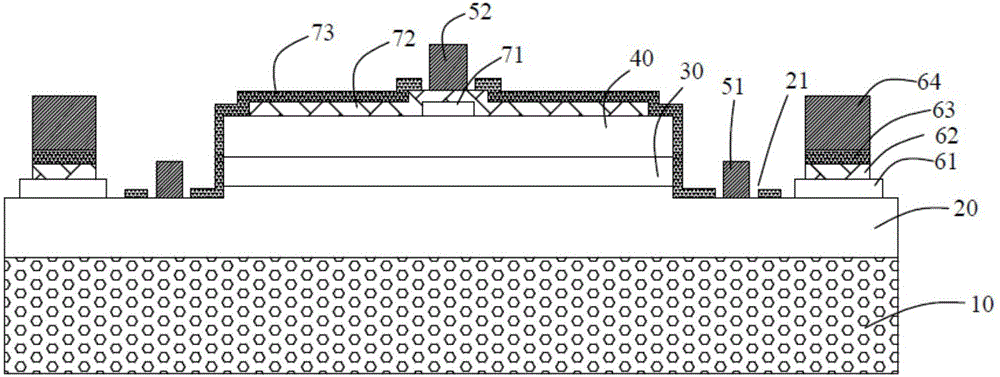

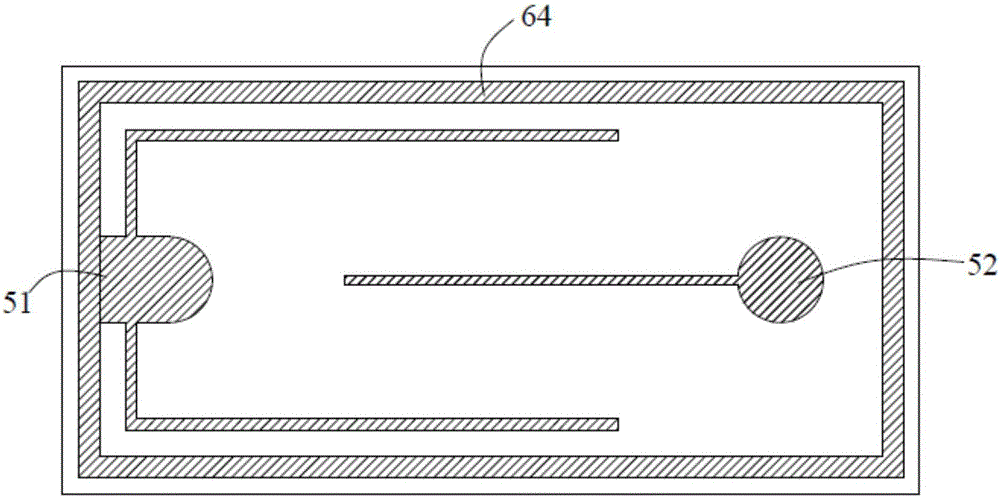

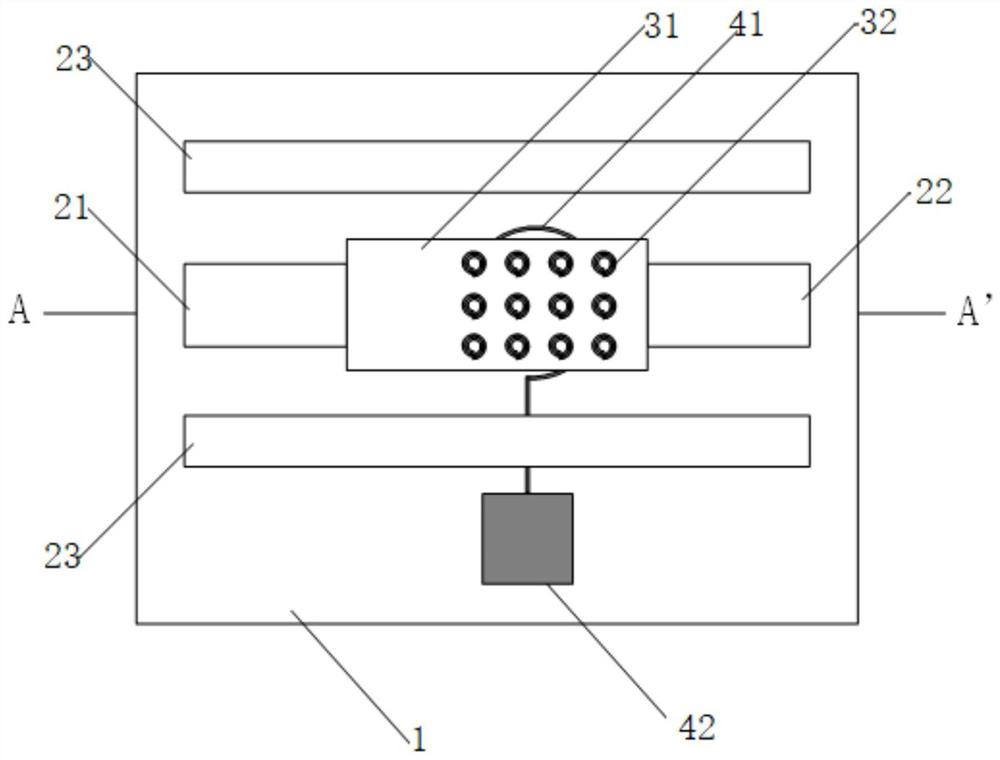

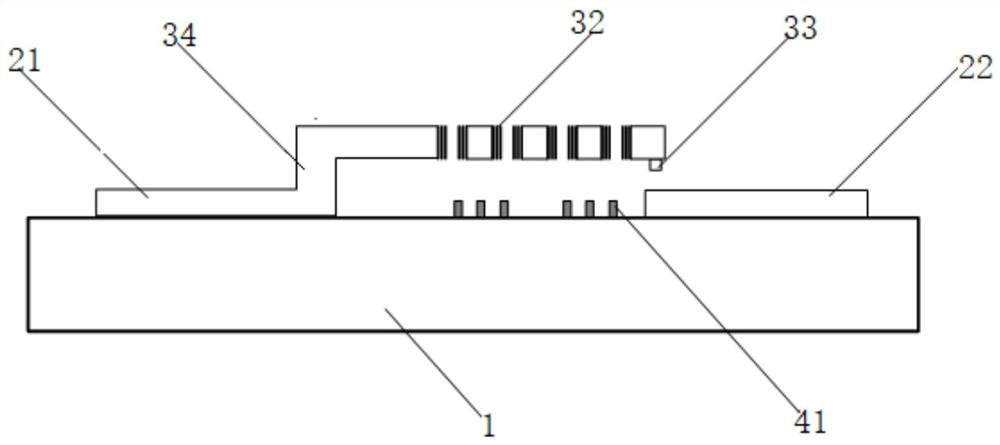

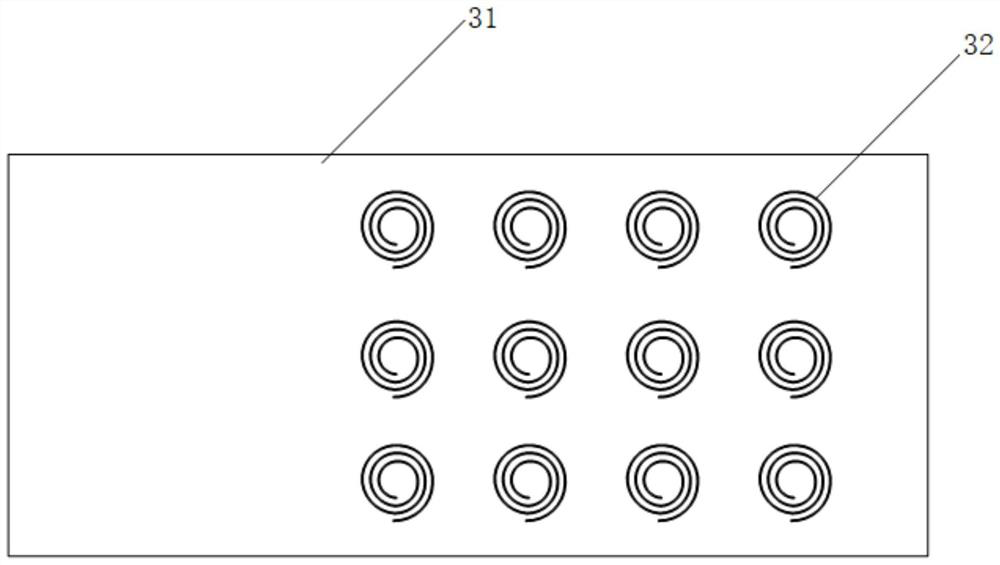

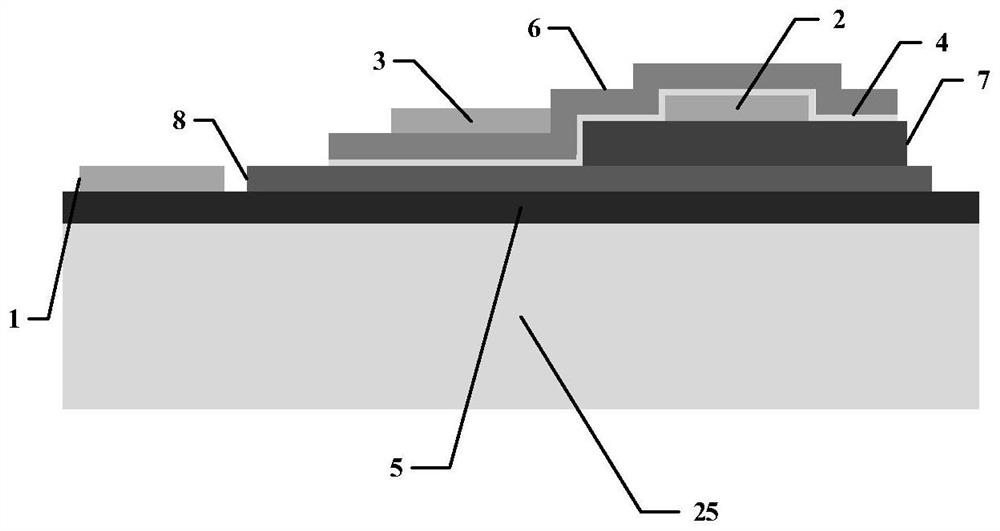

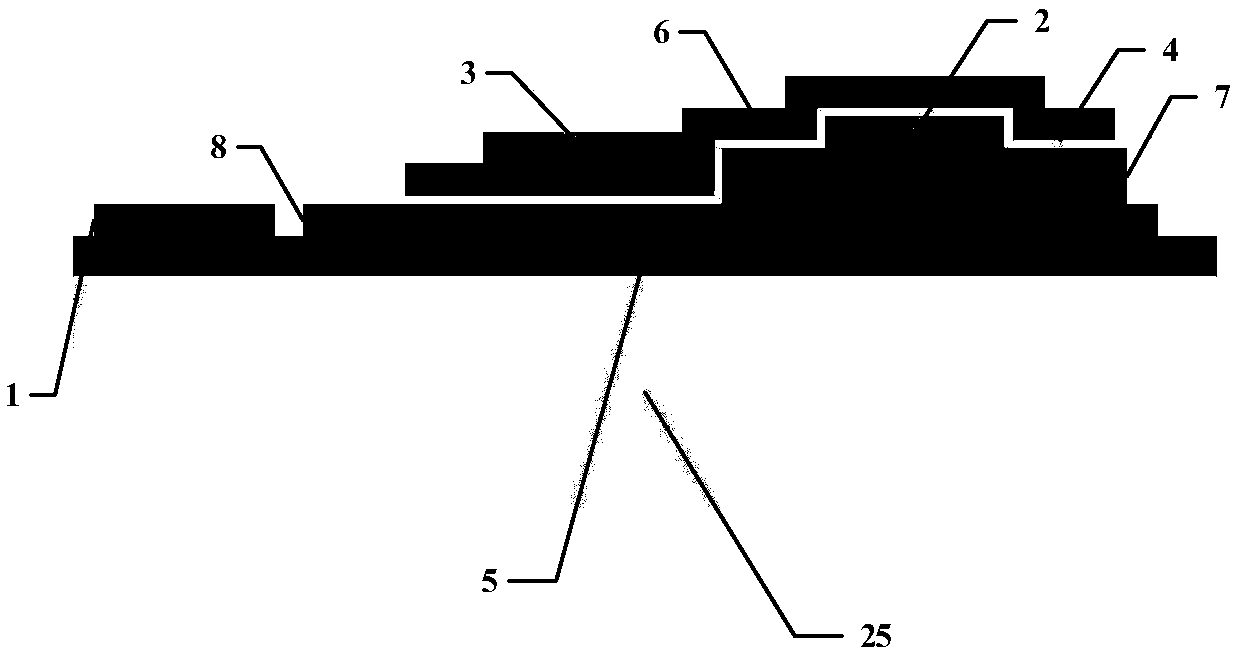

RDL (radiological defense laboratory) technology-compatible inductive component and manufacture method

InactiveCN102779807AHigh quality factorImprove performanceSemiconductor/solid-state device detailsSolid-state devicesSpin coatingMetal deposition

The invention relates to an RDL (radiological defense laboratory) technology-compatible inductive component and a manufacture method. The method is characterized by comprising the following steps of: using a thin film metal deposition technology on a silicon substrate and simultaneously forming a first layer metal interconnection transmission line and a shielding layer; carrying out the spin coating of a photosensitive medium layer, and developing in an exposure way, forming into a metal interconnection through hole, annealing, performing dry etching on plasmas to remove the developing remaining part, and filling the metal interconnection through hole with plated metal; forming a second layer metal interconnection transmission line and an inductance coil; forming an outermost layer metal through hole; and manufacturing an electrical inductor with the metal shielding layer under the condition that the original technological steps are not increased. The invention is compatible with the main-stream re-wiring technology in wafer level encapsulation, under the condition that the technological steps are not increased, the electrical inductor with the shielding layer can be manufactured at low cost, the substrate eddy current of the silicon substrate can be effectively cut off, the quality factor of the electric inductor can be improved, the series resistance of the electric inductor can be reduced, and the electromagnetic interference of the vortex current to a chip can be reduced.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

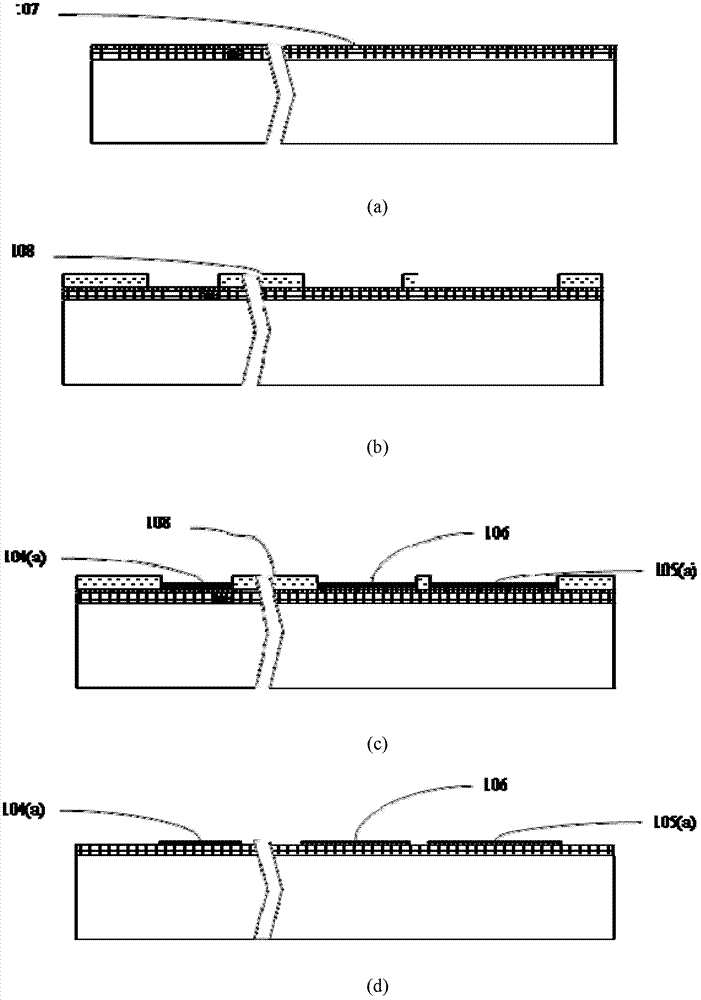

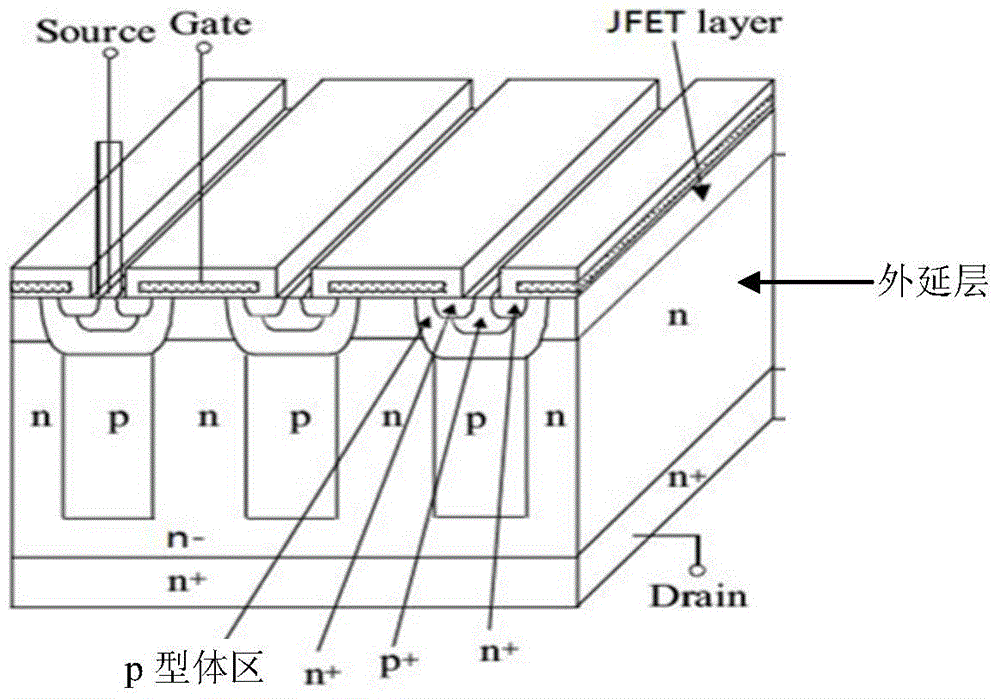

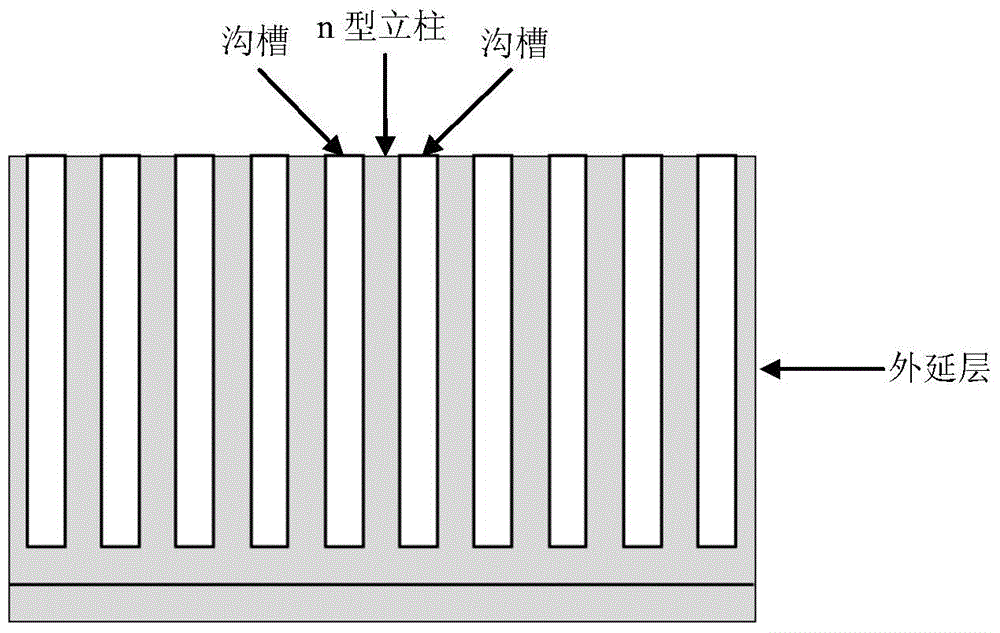

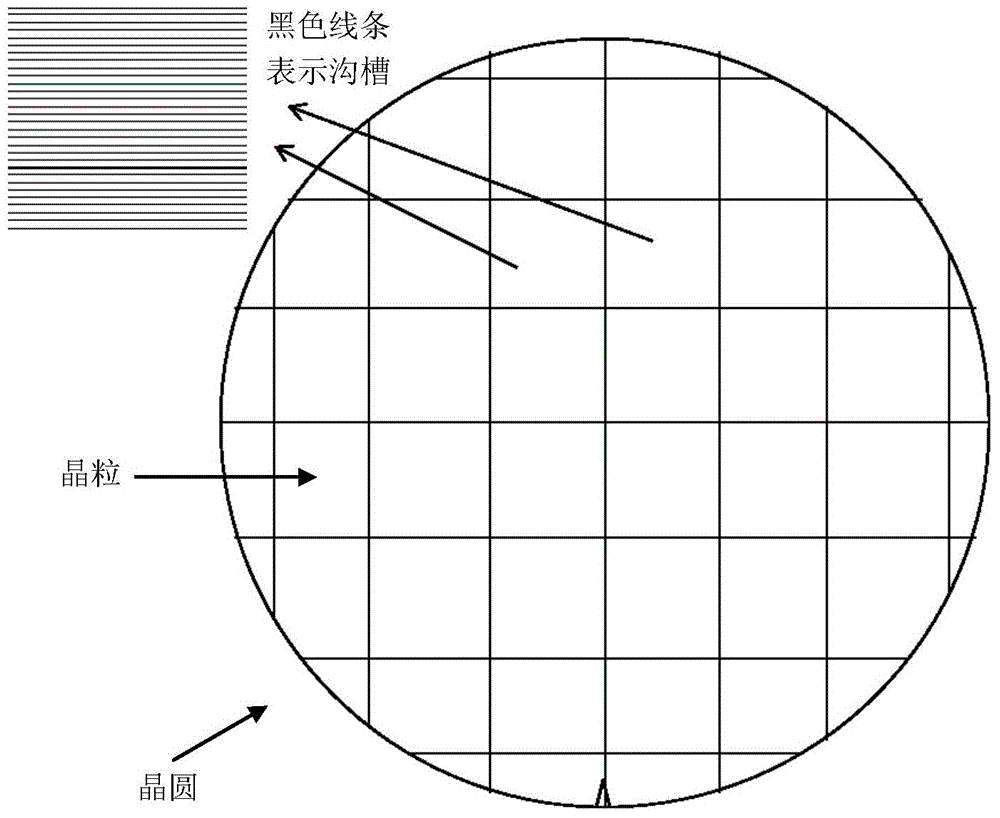

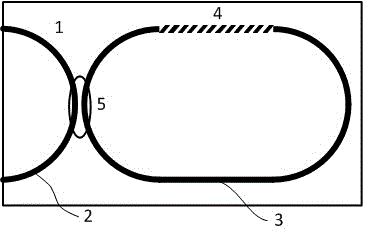

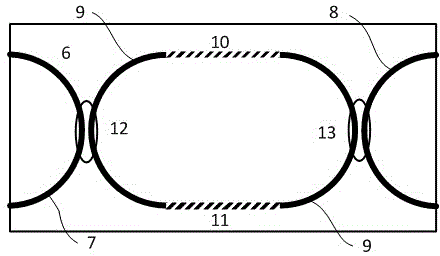

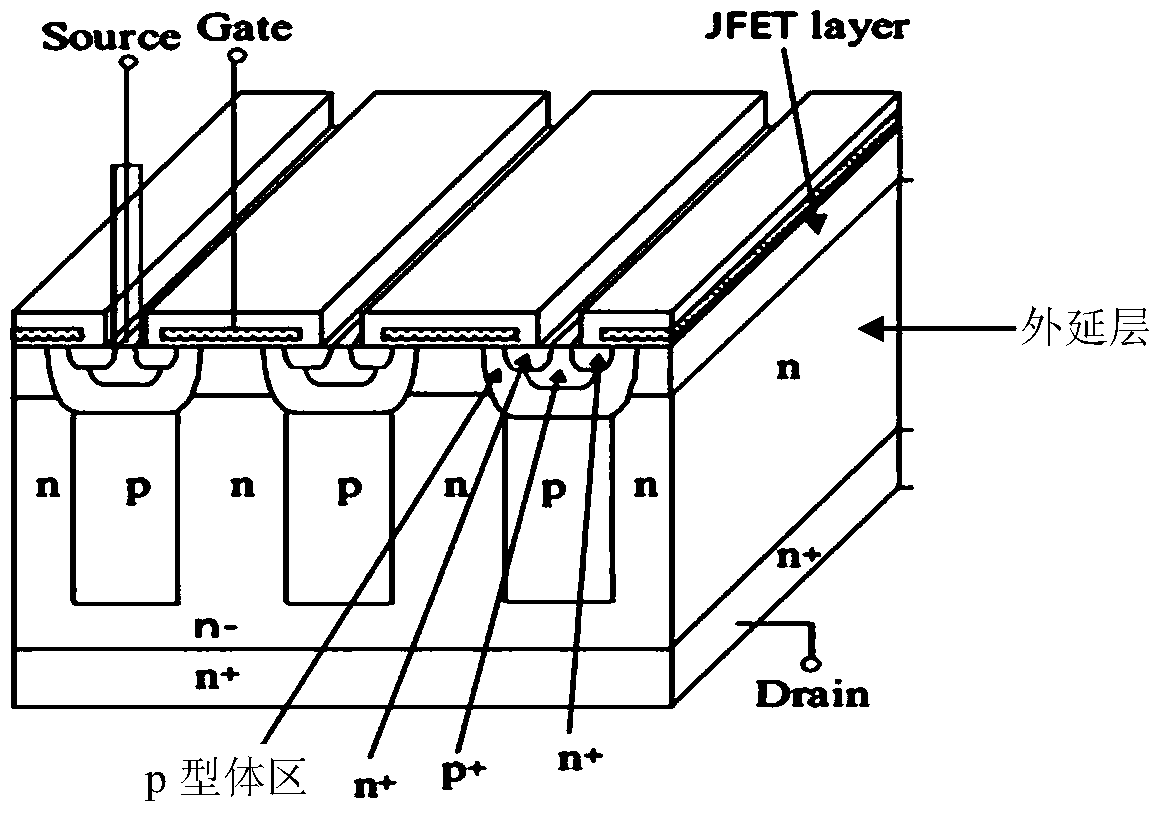

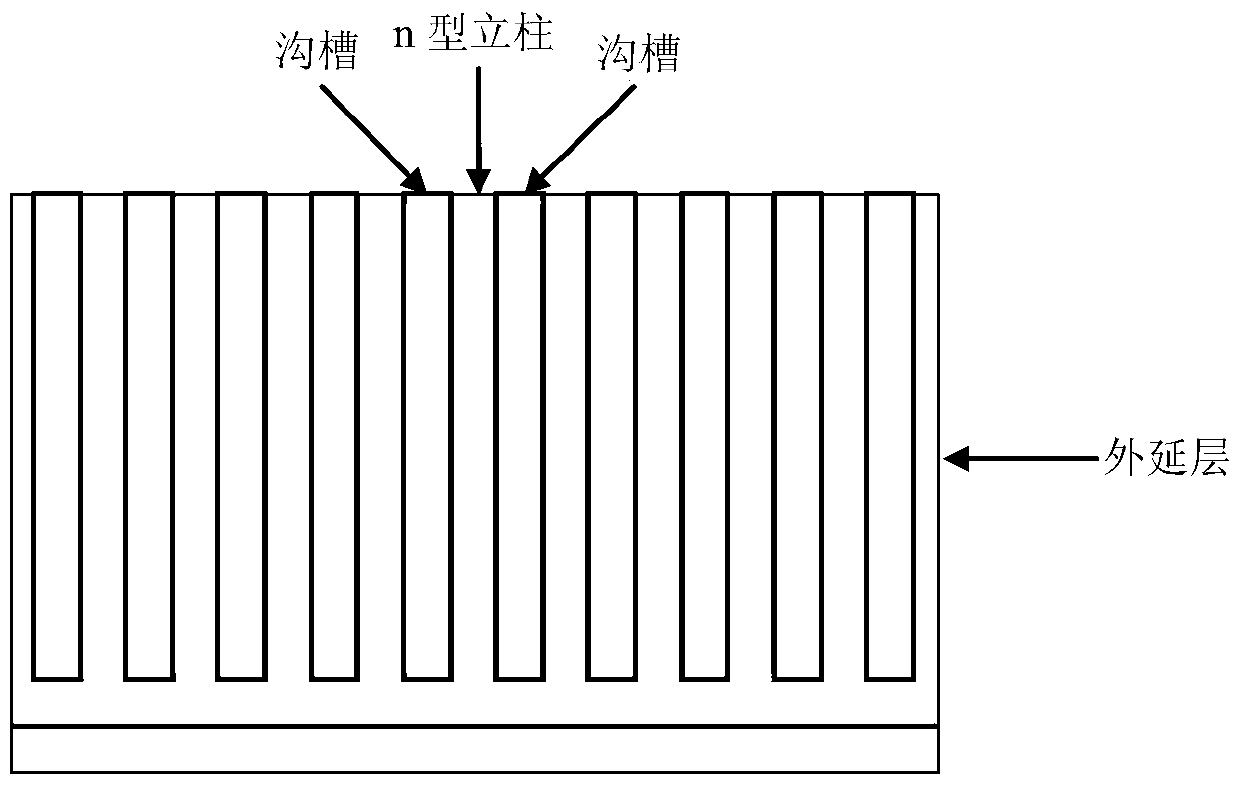

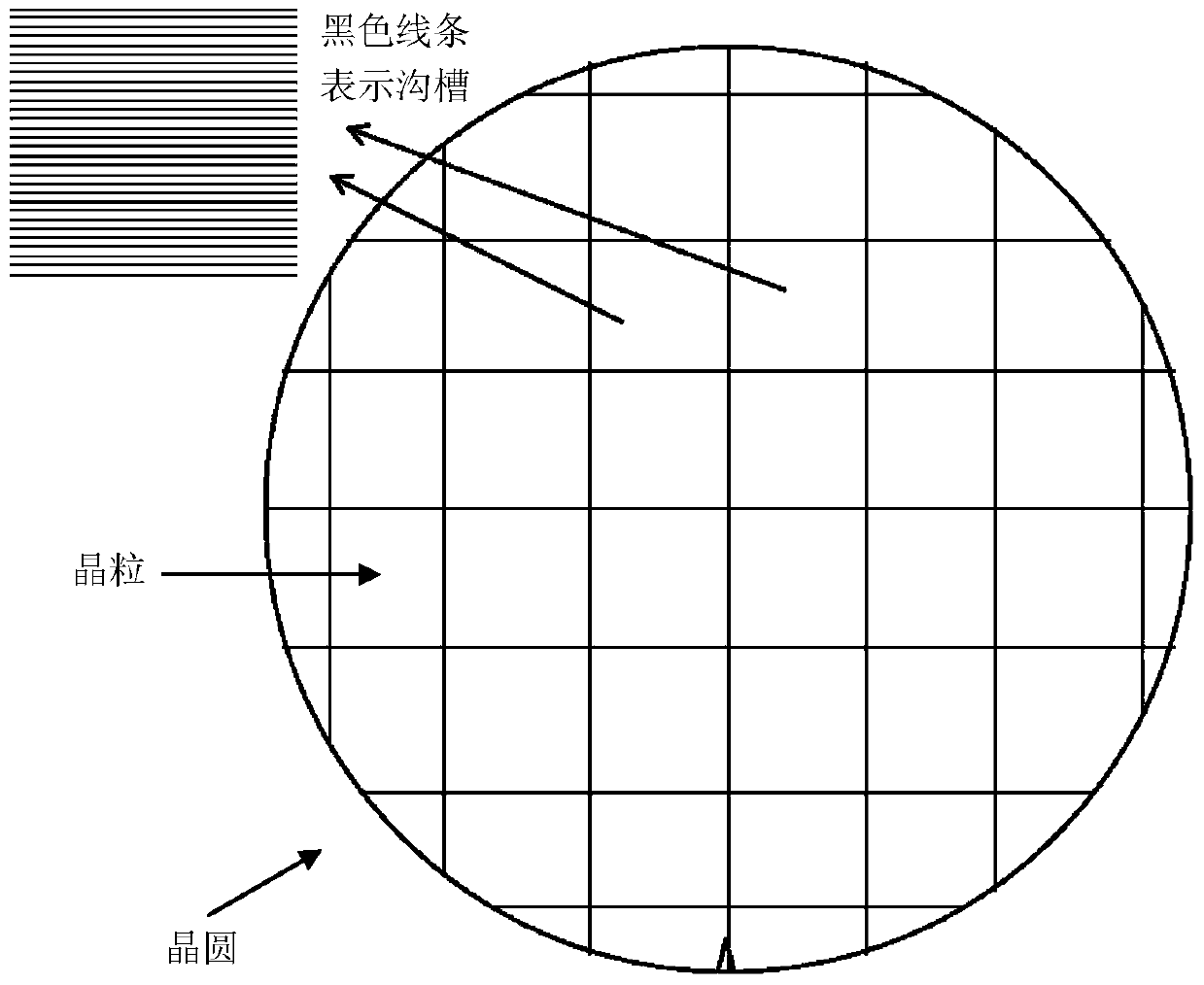

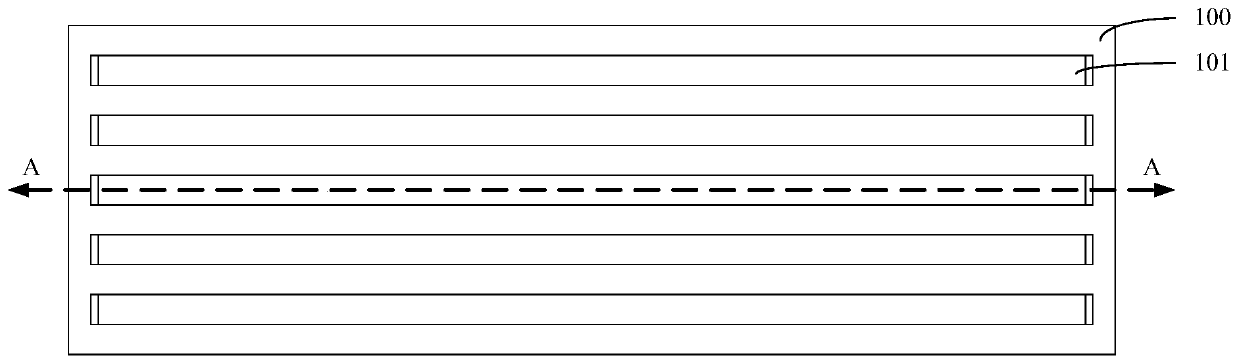

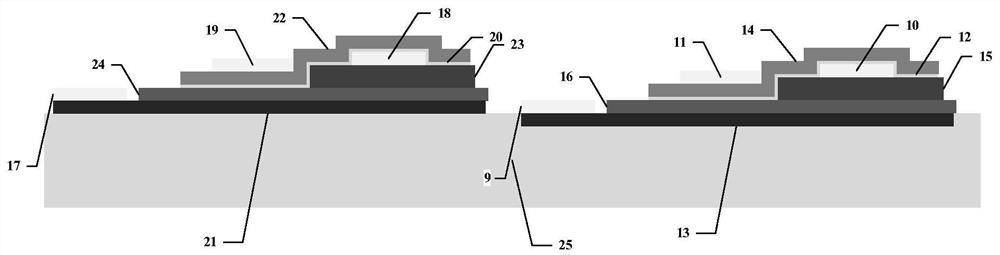

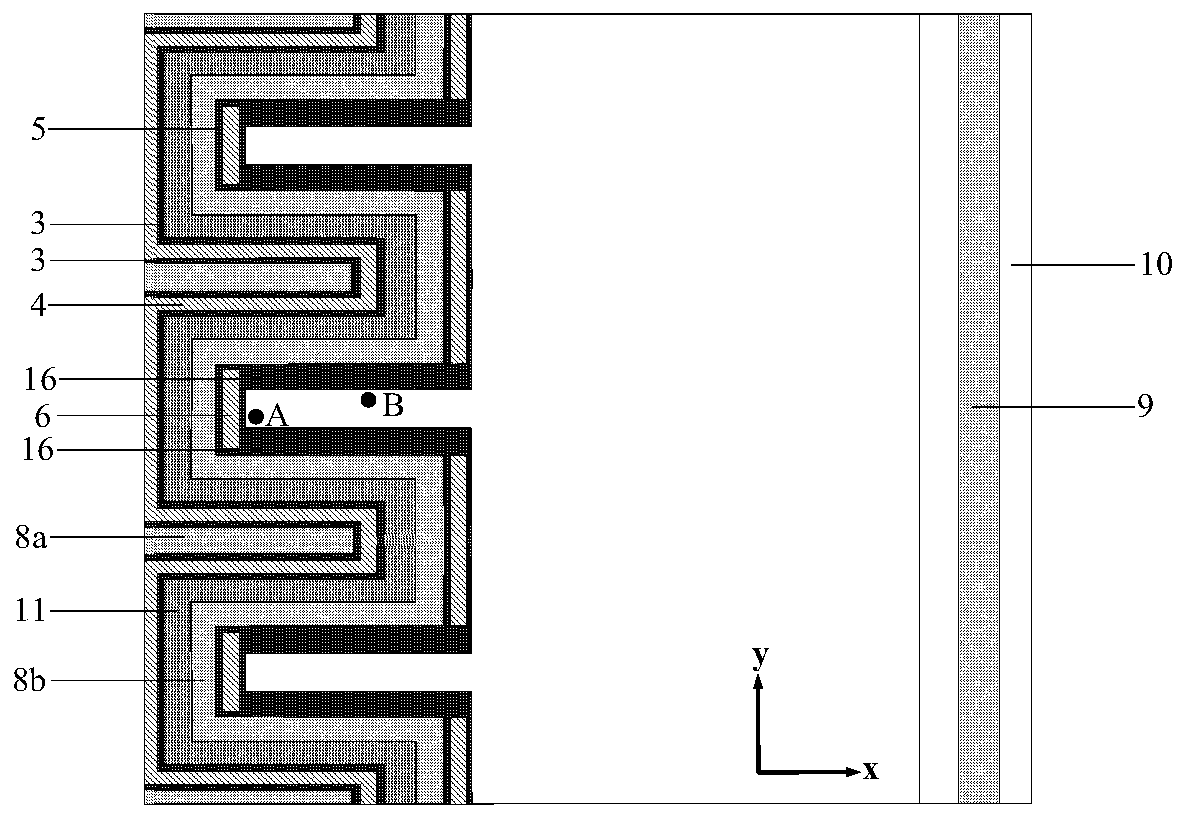

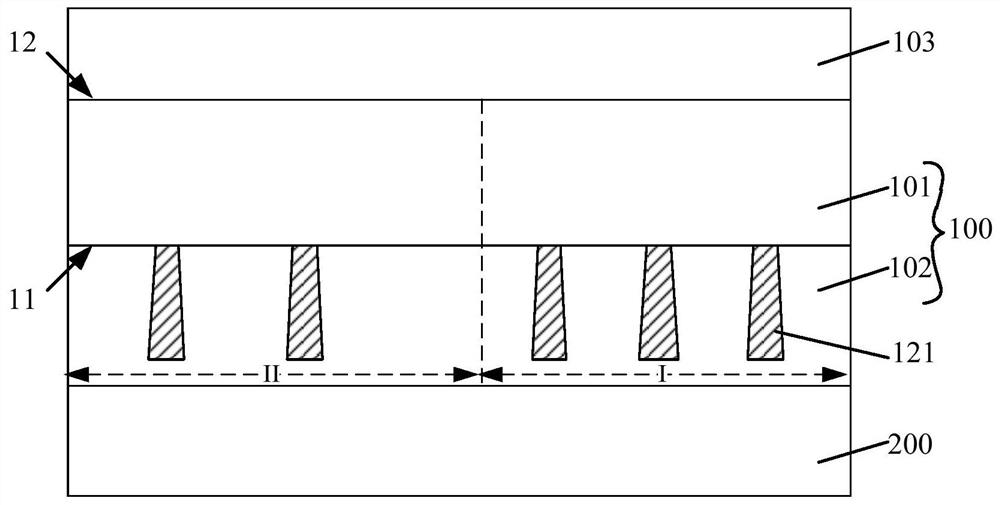

Trench-type super-junction device layout structure and manufacturing method thereof

ActiveCN104617133AAvoid Wafer WarpageOffset stressSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDislocation

The invention discloses a trench-type super-junction device layout structure. A plurality of grooves for forming a column in each grain, the adjacent parallel grooves as a groove array, the array direction of the grooves adjacent to each other perpendicular to the array. The present application also discloses a method of manufacturing a trench-type super junction devices, it has formed a super junction structure having two or more of an array of channels in each grain, each groove by adjacent and parallel array composed of grooves, the grooves adjacent to the array direction of the array perpendicular to each other; said method comprising the ion implantation process is formed to cover all the grooves of the array ion-implanted region, ion-implanted region is formed at least one groove parallel to the array and at least another array of channels perpendicular to; final on all array of channels are formed super junction devices. This application is arranged perpendicular to each other by adjacent grains or cell array of channels, and to counteract the stress of deep trenches etched, and overcome the dislocations and other defects.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

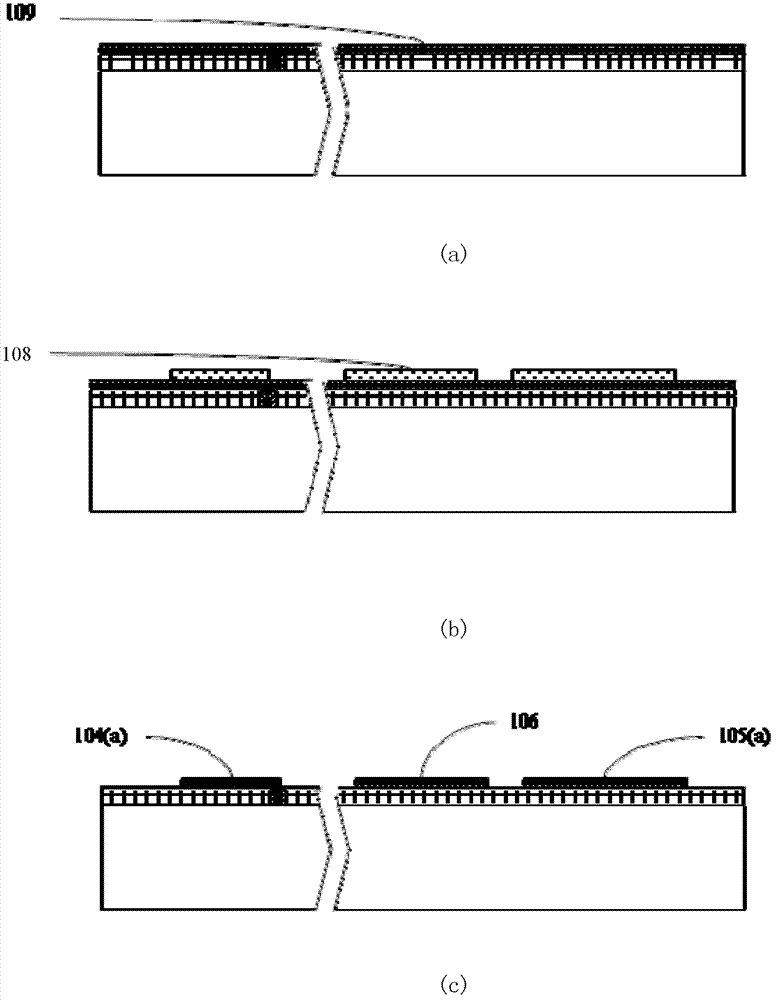

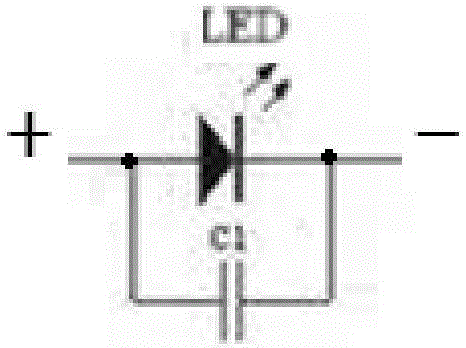

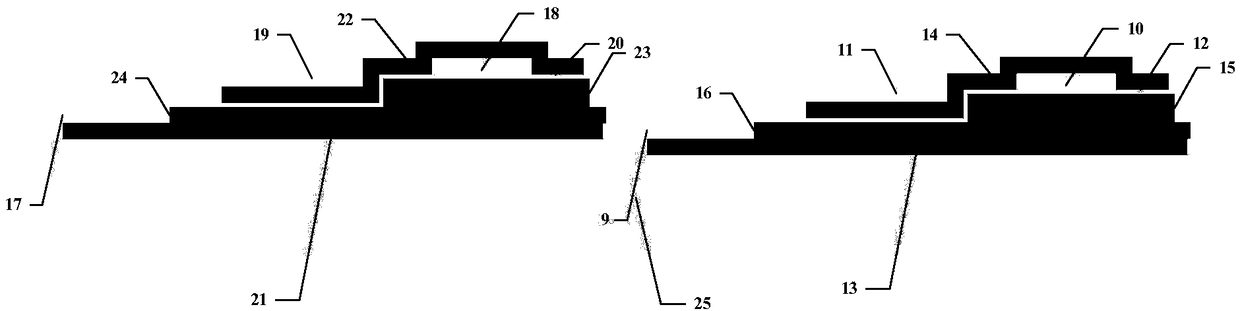

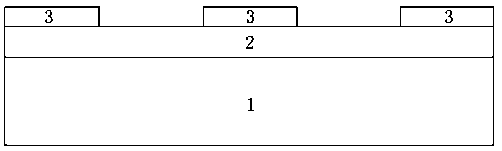

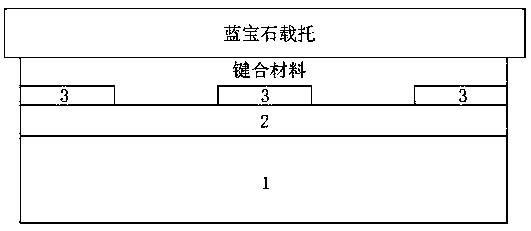

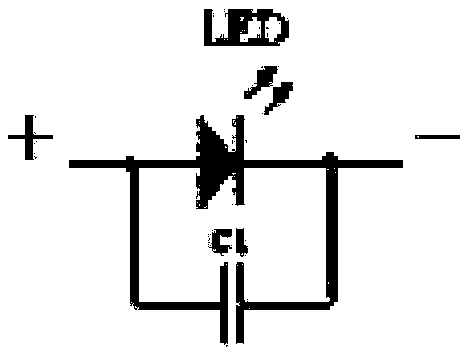

Light-emitting diode (LED) chip with capacitance structure and preparation method thereof

ActiveCN106784173APlay a protective effectImprove reliabilitySemiconductor devicesCapacitanceQuantum well

The invention provides a light-emitting diode (LED) chip with a capacitance structure and a preparation method thereof. The LED chip comprises an N-type semiconductor layer, a multi-quantum well light-emitting layer, a P-type semiconductor layer, an N electrode and a P electrode, wherein the N electrode is electrically connected with the N-type semiconductor layer, the P electrode is electrically connected with the P-type semiconductor layer, the LED chip is electrically connected with the capacitance structure, the capacitance structure comprises a first conductive layer, a second conductive layer and a dielectric material layer, the first conductive layer and the second conductive layer are parallel to each other and are arranged at intervals, the dielectric material layer is arranged between the first conductive layer and the second conductive layer, the first conductive layer is electrically connected with the P electrode, the second conductive layer is electrically connected with the N electrode, and the first conductive layer and the second conductive layer in the capacitance structure and the P electrode and the N electrode of the LED chip are arranged in parallel. By additionally arranging the capacitance structure on the LED chip, the capacitance structure can play a protection role on the LED chip, ripple can be filtered, surge impact is prevented, and the reliability of the LED chip is improved.

Owner:FOCUS LIGHTINGS SCI & TECH

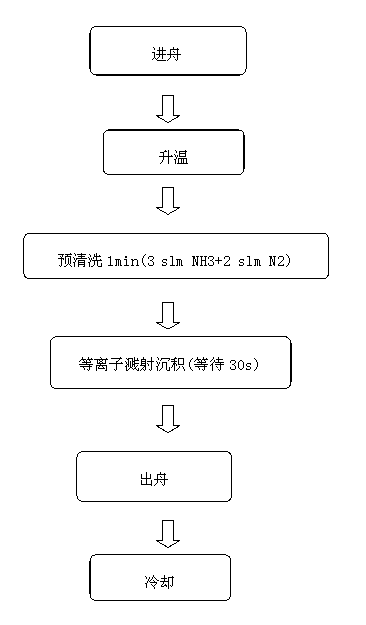

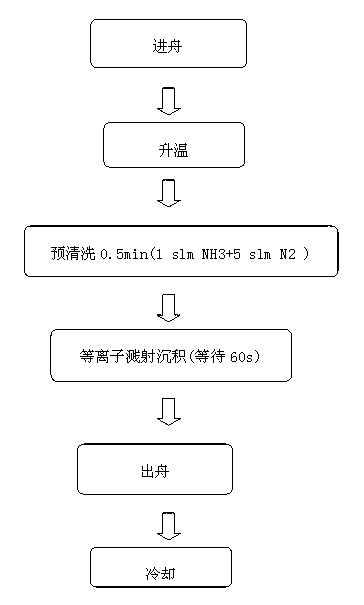

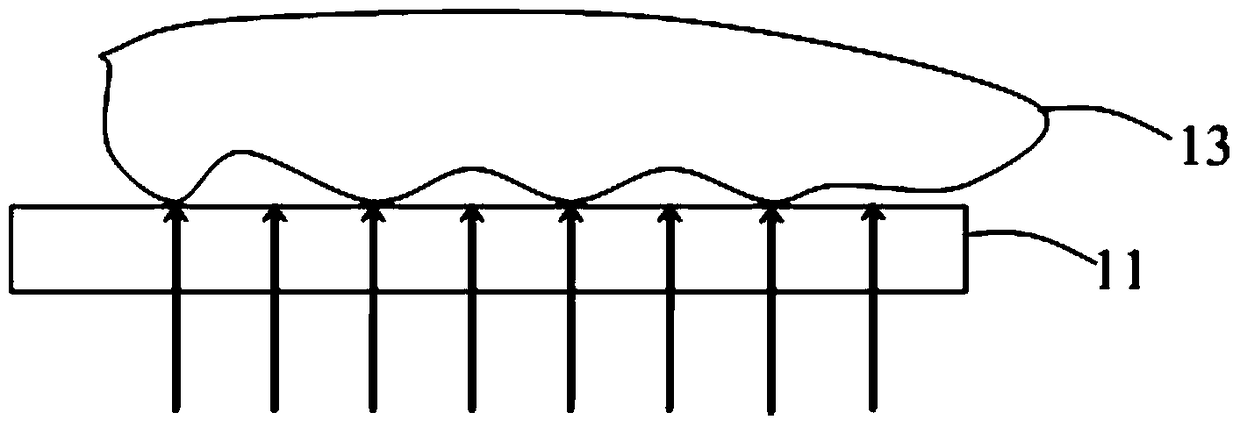

Coating process of crystalline silicon solar cell

ActiveCN103290374AReduced pre-cleaning timeReduce processing timeFinal product manufactureVacuum evaporation coatingSilanesNitrogen

The invention provides a coating process of a crystalline silicon solar cell. The coating process comprises the following steps of: (1) entering a boat: putting a silicon wafer into a quartz boat; (2) heating after nitrogen is added; (3) precleaning: simultaneously adding nitrogen and ammonia, and turning on radio frequency to preclean; (4) plasma sputtering deposition: adding ammonia and silane, and turning on the radio frequency to perform plasma sputtering deposition; (5) going out of the boat; (6) cooling. The coating process has the beneficial effects that the production time is shortened, the production capacity is improved, and the process running time is shortened by six minutes; the ammonia consumption and the production cost are reduced; the uniformity of a silicon nitride film is improved; the conversion efficiency of the cell is improved; the method is simple and practicable, and additional processing procedures and materials do not need to be added.

Owner:泗阳腾晖光电有限公司 +1

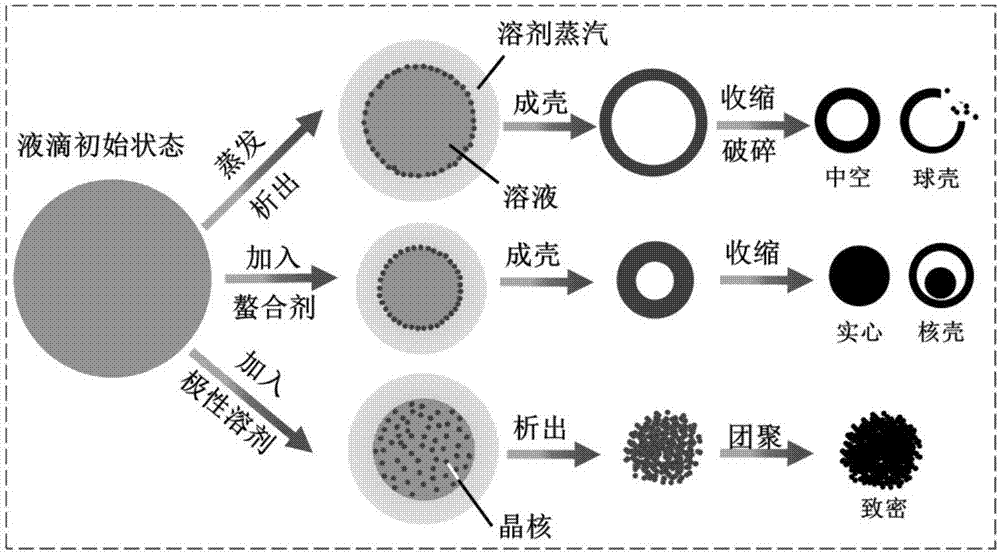

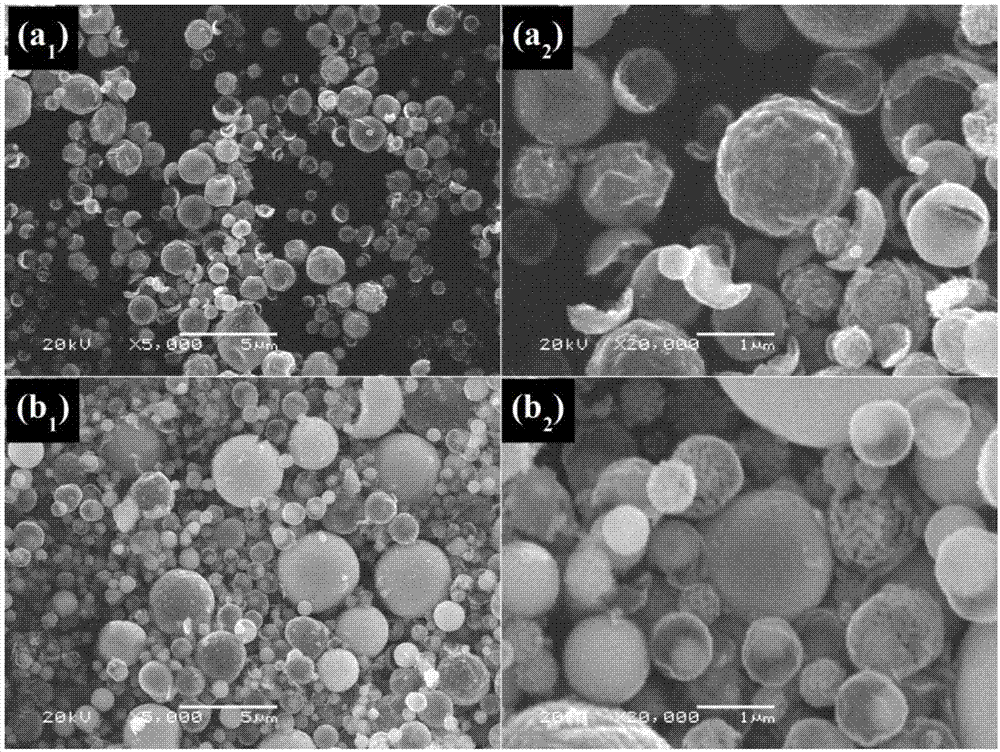

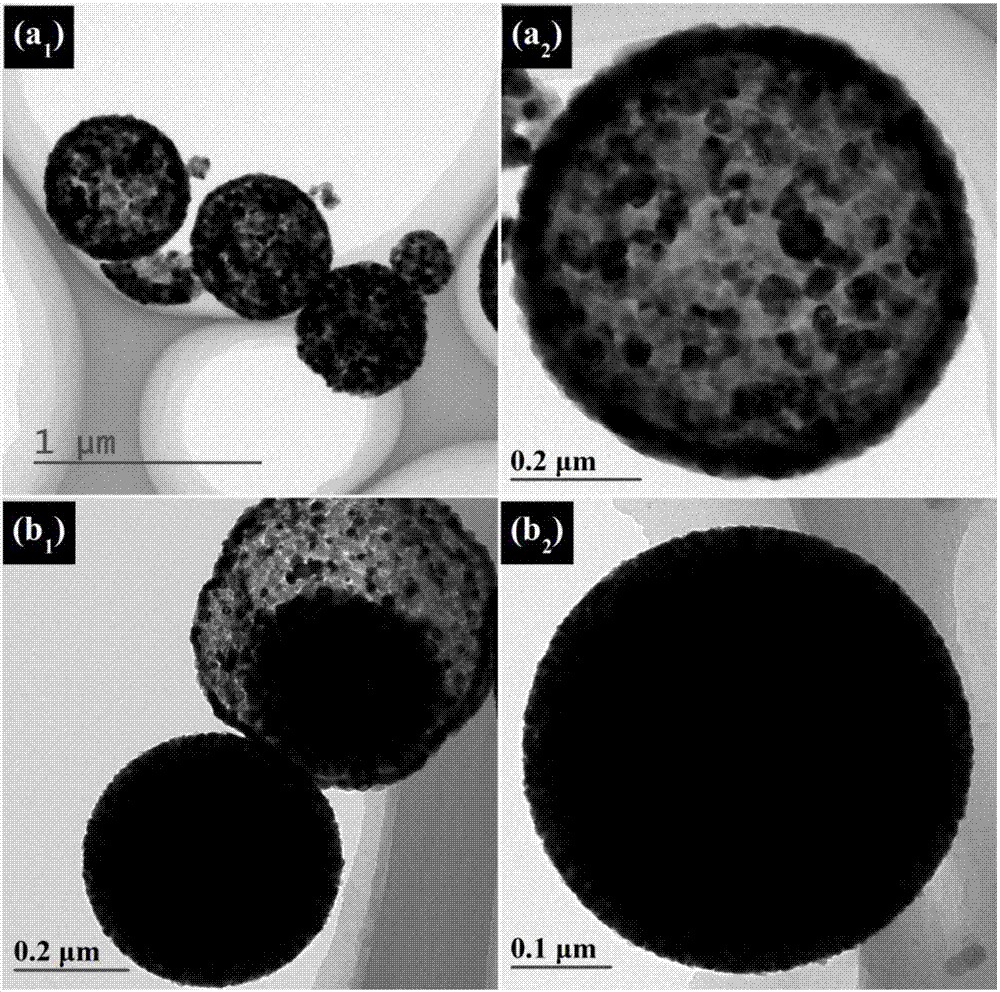

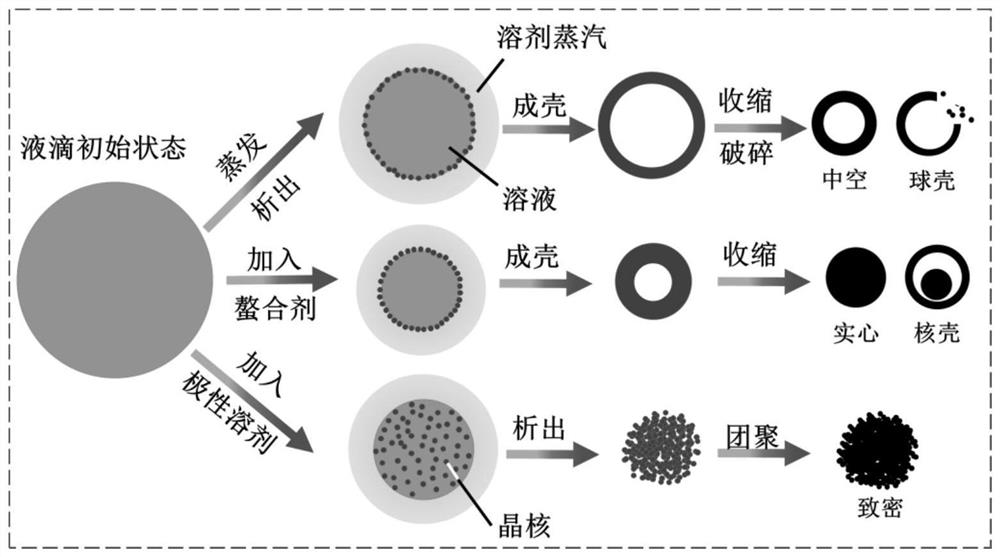

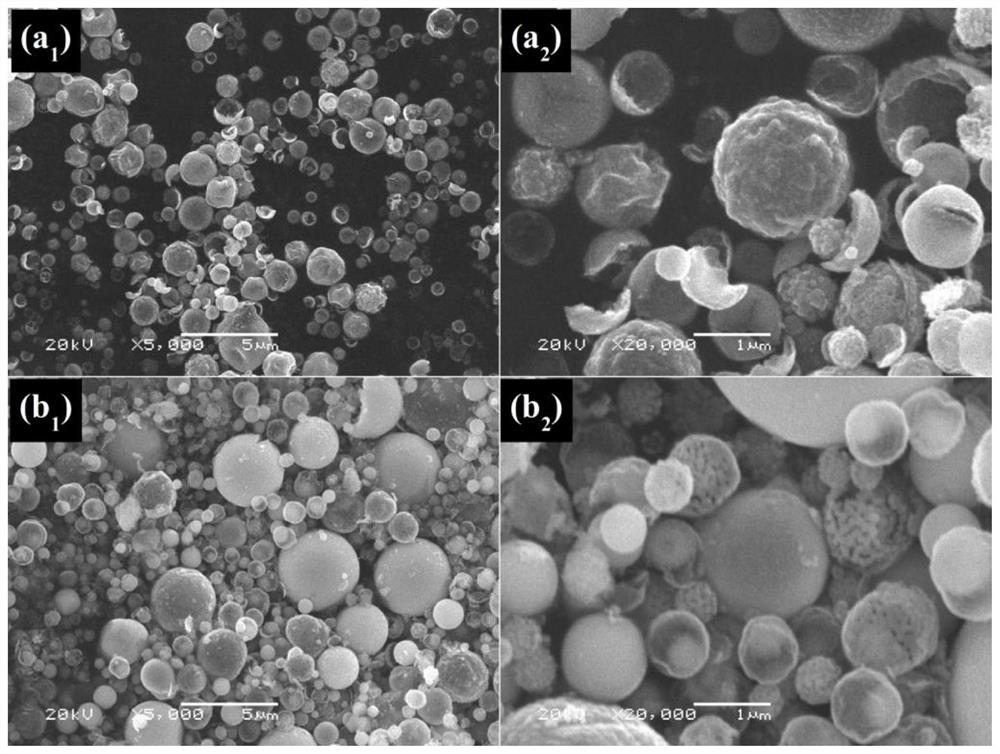

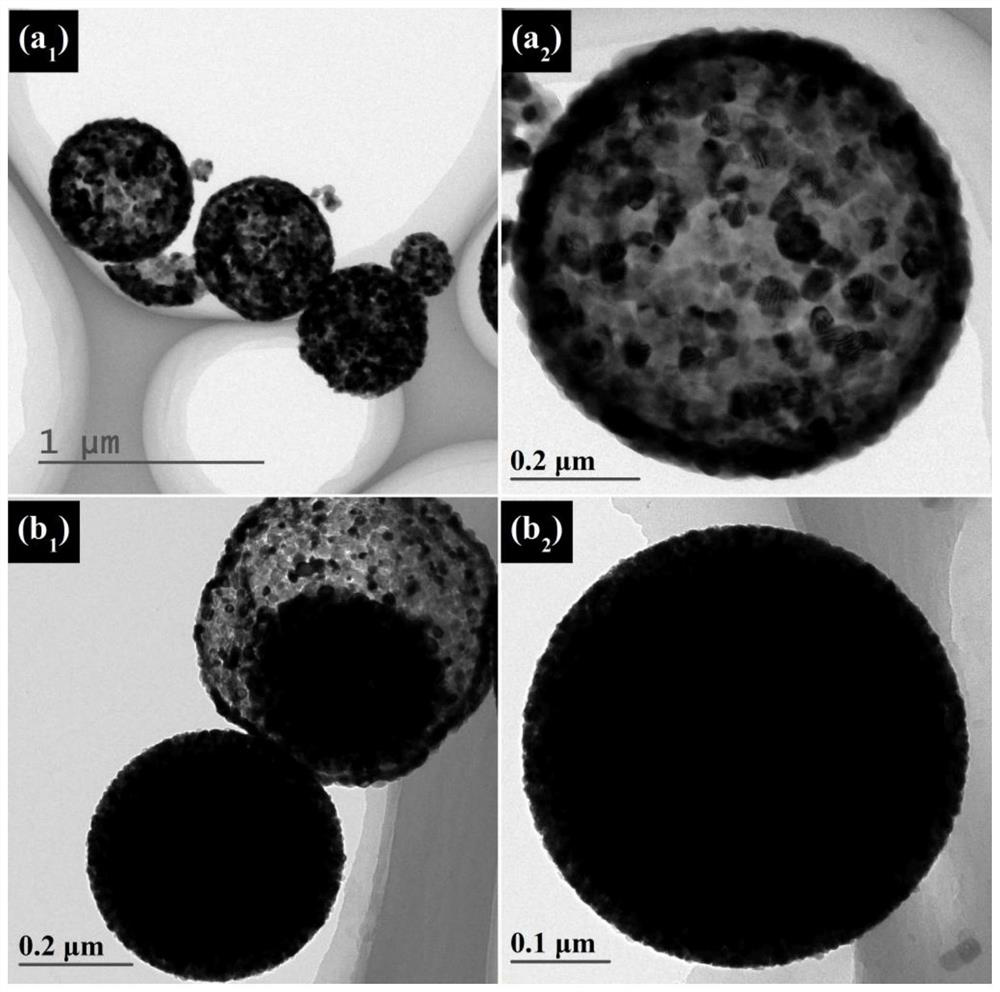

High-tap-density metal oxide, preparation method and lithium-ion battery

ActiveCN107482162AHigh tap densityLow effective concentrationElectrode thermal treatmentAcetic acidN dimethylformamide

The invention provides a preparation method of high-tap-density metal oxide. The preparation method comprises the following steps: S1, dissolving metal salt with a solvent; adding an organic additive and uniformly mixing to prepare a precursor solution, wherein the solvent is one or two of de-ionized water and distilled water, and the organic additive is one or more of N,N-dimethylformamide, tartaric acid, acetic acid and dimethyl sulfoxide; S2, atomizing the spraying precursor solution in step S1 by utilizing an atomizer; conveying the precursor solution into a spraying pyrolyzing furnace by utilizing carrying gas, and carrying out pyrolysis; collecting a pyrolysis product by utilizing a powder collector, so as to obtain the high-tap-density metal oxide. The invention further provides the high-tap-density metal oxide prepared by the method and a high-energy-density lithium-ion battery. According to the preparation method provided by the invention, any auxiliary facility does not need to be added, and technology steps do not need to be added; prepared powder grains have good sphericility degree, are dense and compact and have high tap density; the preparation method has the advantages of simple operation, high efficiency, short flow and high practicability.

Owner:CENT SOUTH UNIV

Moisture-absorbing and environment-protection type fabric

InactiveCN105919198AGood hygroscopicityMoisture absorptionProtective garmentSpecial outerwear garmentsSurface layerIsolation layer

The invention discloses a moisture-absorbing and environment-protection type fabric. The moisture-absorbing and environment-protection type fabric is characterized by comprising the following raw materials in percentage by mass: 12 to 20% of hemp fiber, 10 to 26% of chinlon, 2 to 5% of fluon, and 6 to 14% of copper ammonia fiber, wherein color cotton and the chinlon are blended to form an inner layer of the moisture-absorbing and environment-protection type fabric; the hemp fiber and wool fiber are blended to form an isolation layer of the moisture-absorbing and environment-protection type fabric; the copper ammonia fiber and the fluon are blended to form a surface layer of the moisture-absorbing and environment-protection type fabric. The moisture-absorbing and environment-protection type fabric has the advantages that the fabric is light, thin and comfortable, the moisture-absorbing effect is good, and the moisture-absorbing, drying and heat-insulation effects are realized by utilizing different raw materials in different positions; if the moisture-absorbing and environment-protection type fabric is not worn after use, the moisture-absorbing and environment-protection type fabric can be automatically degraded after a period of time, so that the time and labor are saved, and the environment-protection effect is realized; the production cost is lower, the production technology is simple, any additional technological step is not needed, and the production efficiency is improved.

Owner:南通中兴多元复合钢管有限公司

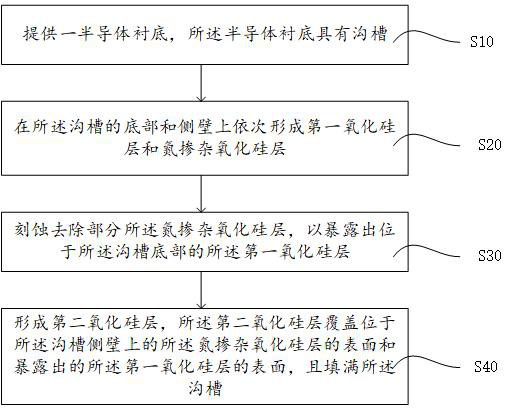

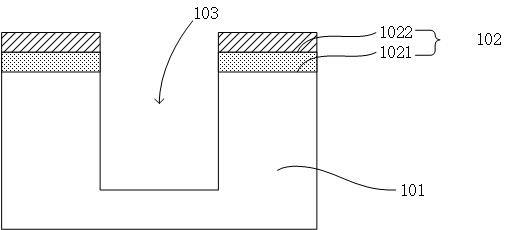

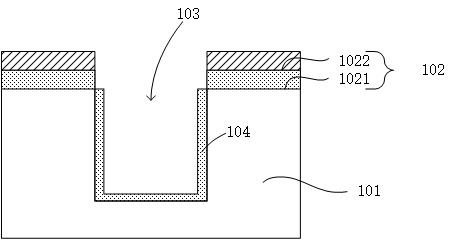

Semiconductor structure and manufacturing method thereof

InactiveCN111933572AImprove process efficiencyAvoid the phenomenon of void defects caused by premature sealingSemiconductor/solid-state device manufacturingPhysicsNitrogen doping

The invention provides a semiconductor structure and a manufacturing method thereof, and the method comprises the steps: providing a semiconductor substrate which is provided with a trench; sequentially forming a first silicon oxide layer and a nitrogen-doped silicon oxide layer at the bottom and on the side wall of the trench; etching to remove part of the nitrogen-doped silicon oxide layer so asto expose the first silicon oxide layer at the bottom of the trench; and forming a second silicon dioxide layer which covers the surface of the nitrogen-doped silicon oxide layer on the side wall ofthe trench and the exposed surface of the first silicon oxide layer and fills the trench. Because the growth rate of the second silicon dioxide on the first silicon oxide layer is greater than the growth rate of the second silicon dioxide on the silicon oxynitride layer, the growth rate of the second silicon dioxide at the bottom of the trench is greater than the growth rate of the silicon oxynitride layer on the side wall of the trench, and the phenomenon that the second silicon dioxide layer on the side wall of the trench grows too fast to cause premature sealing to generate a cavity defectis avoided.

Owner:晶芯成(北京)科技有限公司

Waterproof anti-ultraviolet fabric

InactiveCN108720140AGood hygroscopicityReduce manufacturing costGarment special featuresSynthetic resin layered productsEnvironmental resistanceSurface layer

The invention discloses waterproof anti-ultraviolet fabric. The waterproof anti-ultraviolet fabric is creatively characterized by being composed of, by mass, 13-17% of colored cotton, 12-12% of jute fiber, 25-43% of polyamide fiber, 14-18% of wool fiber, 12-15% of fluorine fiber and 16-24% of copper ammonia fiber, the colored cotton and the polyamide fiber are blended as an inner layer of the waterproof anti-ultraviolet fabric, the jute fiber and the wool fiber are blended as an interlayer of the waterproof anti-ultraviolet fabric, and the copper ammonia fiber and the fluorine fiber are blended as a surface layer of the waterproof anti-ultraviolet fabric. The waterproof anti-ultraviolet fabric is light, thin, comfortable, good in moisture absorption effect and conducive to allowing different raw materials to play roles in absorbing moisture, drying and holding temperature at different positions. After being used, the fabric can be degraded by itself if it does not need to be worn anymore, so that the fabric is time-saving, labor-saving and environment-friendly. The fabric is low in production cost and simple in production process, and adding of any process step is not needed, so that production efficiency is improved.

Owner:NANTONG BOTAI ART PATTERN DESIGN CO LTD

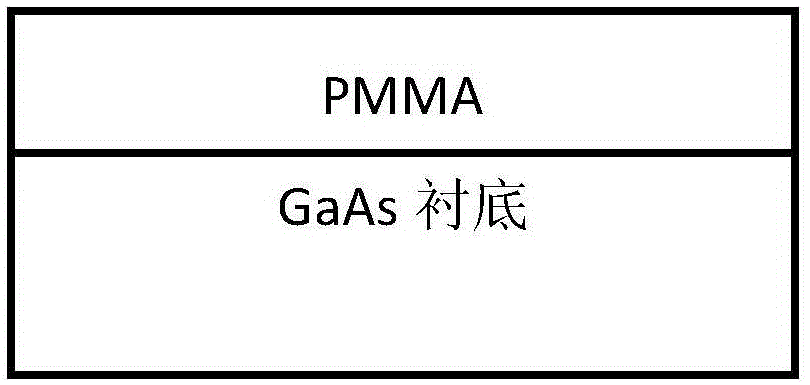

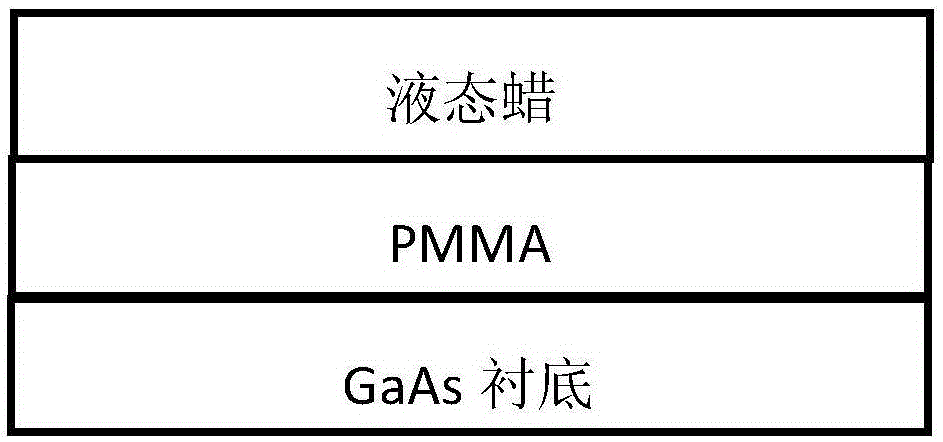

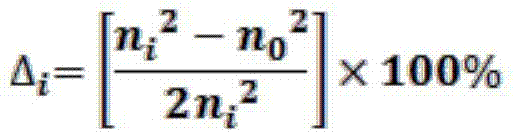

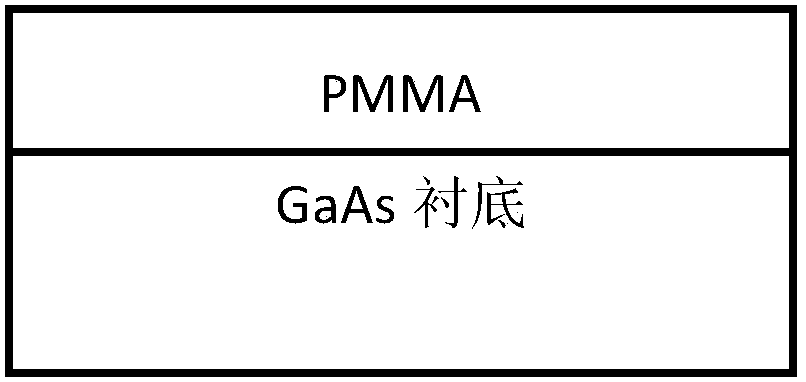

Liquid wax for dice bonding in GaAs MMIC thinning technology

InactiveCN105018025ANo miscibility problemsSolve the problem of slow glue removal and difficult glue removalWax adhesivesWaxDissolution

The invention discloses liquid wax for dice bonding in a GaAs MMIC thinning technology. The liquid wax is composed of a certain amount of a Crystal bond 509 energetic binder and acetone capable of dissolving the amount of the Crystal bond 509 energetic binder. The liquid wax obtained by dissolving the Crystal bond 509 energetic binder in acetone replaces high temperature wax used in a traditional dice bonding technology. Thus, mutual dissolution will not happen to a part where the liquid wax and a photoresist are contacted, and hardly-removed organic matters generated by mutual dissolution of a photoresist and high temperature wax are avoided. In addition, as the liquid wax and a photoresist are both easy to dissolve in acetone, the liquid wax and the photoresist are separated from each other only by being immersed in acetone. Therefore, the problem that removing of a photoresist is slow and hard during dice bonding by the use of high wax in a traditional technology is solved. Besides, the liquid wax provided by the invention has strong adhesiveness, and the problem of fragments during subsequent polishing and thinning processes is effectively solved.

Owner:GUILIN UNIV OF ELECTRONIC TECH

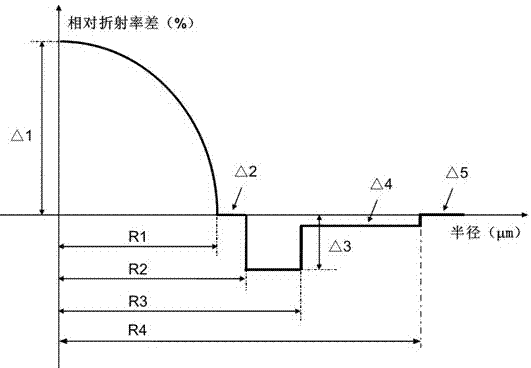

High-bandwidth bending insensitive multimode optical fiber

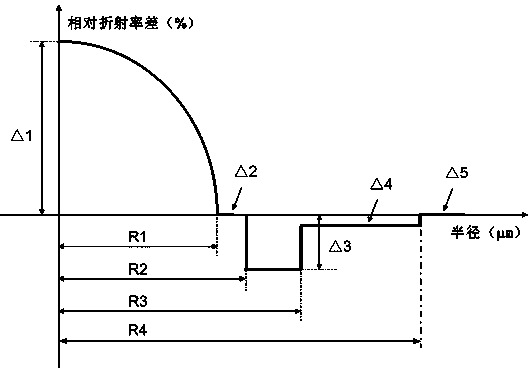

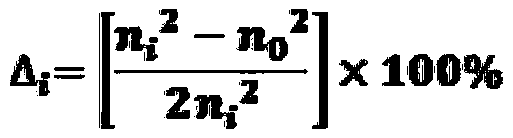

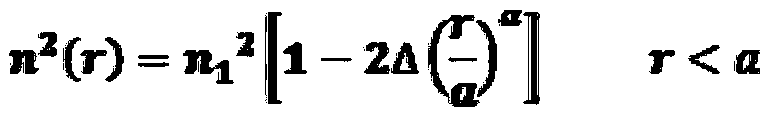

ActiveCN107193080AHigh viscosityReasonable viscosityOptical fibre with graded refractive index core/claddingOptical fibre with multilayer core/claddingStress distributionHigh bandwidth

The present invention relates to a high-bandwidth bending insensitive multimode optical fiber. The high-bandwidth bending insensitive multimode optical fiber comprises a core layer and claddings surrounding the core layer. The refractive index cross section of the core layer is in the shape of a parabola. The high-bandwidth bending insensitive multimode optical fiber is characterized in that the claddings include an inner cladding, a first recessed cladding, a second recessed cladding and an outer cladding which are distributed sequentially from inside to outside; the unilateral radial width (R2-R1) of the inner cladding ranges from 1 to 3 microns, and the relative refractive index difference delta 2 of the inner cladding ranges from -0.2% to 0.05%; the unilateral radial width (R3-R2) of the first recessed cladding ranges from 3 to 8 microns, and the relative refractive index difference delta 3 of the first recessed cladding ranges from -0.9% to 0.3%; the unilateral radial width (R4-R3) of the second recessed cladding ranges from 6 to 30 microns, and R4 is smaller than or equal to 58 microns, and the relative refractive index difference delta 4 of the second recessed cladding ranges from -0.15% to 0.01%; and the radius R5 of the outer cladding ranges from 60 to 65 microns, and the relative refractive index difference delta 5 of the outer cladding ranges from -0.15% to 0.15%. The optical fiber of the invention has the advantages of reasonable material composition and structural design, convenient process control, improved and reduced inner stress distribution, enhanced bending resistance and increased bandwidth.

Owner:YANGTZE OPTICAL FIBRE & CABLE CO LTD

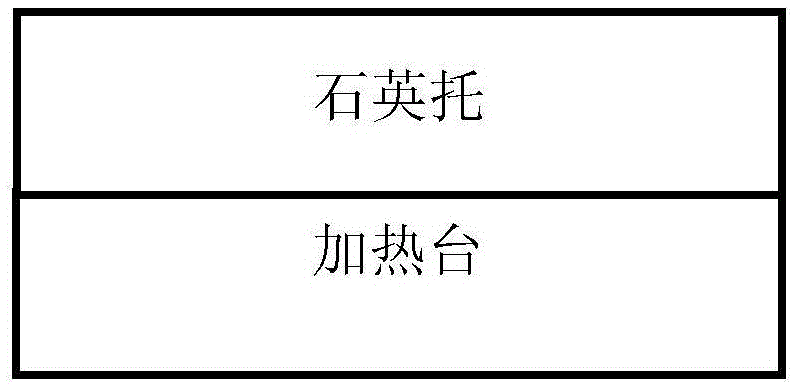

A chip bonding method for gaas MMIC thinning process

ActiveCN105140155BNo miscibility problemsStrong adhesionSemiconductor/solid-state device manufacturingWaxDissolution

The invention discloses a die bonding method used for a GaAs MMIC thinning technology. The method comprises the steps of: evenly coating an electron beam photoresist on the front surface of a substrate and pasting the surface of the substrate to a quartz holder with liquid wax, wherein the liquid wax is composed of a certain amount of Crystalbond 509 strong adhesive and acetone capable of dissolving the amount of the Crystalbond 509 strong adhesive. According to the invention, the liquid wax of a special formula is used instead of conventional high-temperature wax, and in the usage environment, organic matters, which are difficult to remove and generated by mutual dissolution of the photoresist and the high-temperature wax, are prevented without adding other barrier layers; secondly, both the liquid wax and the photoresist are freely soluble in acetone, so that the problem in the conventional technology, that glue removing is slow and difficult when the high-temperature wax is used in the die bonding process, is solved; in addition, good adhesiveness is achieved between the substrate and the quartz holder, and the fragment problem in the polishing and thinning processes is effectively solved.

Owner:GUILIN UNIV OF ELECTRONIC TECH

High Bandwidth Bend Insensitive Multimode Fiber

ActiveCN107193080BHigh viscosityReasonable viscosityOptical fibre with graded refractive index core/claddingOptical fibre with multilayer core/claddingHigh bandwidthRelative refractive index

The present invention relates to a high-bandwidth bending insensitive multimode optical fiber. The high-bandwidth bending insensitive multimode optical fiber comprises a core layer and claddings surrounding the core layer. The refractive index cross section of the core layer is in the shape of a parabola. The high-bandwidth bending insensitive multimode optical fiber is characterized in that the claddings include an inner cladding, a first recessed cladding, a second recessed cladding and an outer cladding which are distributed sequentially from inside to outside; the unilateral radial width (R2-R1) of the inner cladding ranges from 1 to 3 microns, and the relative refractive index difference delta 2 of the inner cladding ranges from -0.2% to 0.05%; the unilateral radial width (R3-R2) of the first recessed cladding ranges from 3 to 8 microns, and the relative refractive index difference delta 3 of the first recessed cladding ranges from -0.9% to 0.3%; the unilateral radial width (R4-R3) of the second recessed cladding ranges from 6 to 30 microns, and R4 is smaller than or equal to 58 microns, and the relative refractive index difference delta 4 of the second recessed cladding ranges from -0.15% to 0.01%; and the radius R5 of the outer cladding ranges from 60 to 65 microns, and the relative refractive index difference delta 5 of the outer cladding ranges from -0.15% to 0.15%. The optical fiber of the invention has the advantages of reasonable material composition and structural design, convenient process control, improved and reduced inner stress distribution, enhanced bending resistance and increased bandwidth.

Owner:YANGTZE OPTICAL FIBRE & CABLE CO LTD

Optical waveguide resonator with high polarization extinction ratio based on tilted waveguide grating structure

Owner:ZHEJIANG UNIV

High tap density metal oxide, preparation method and lithium ion battery

ActiveCN107482162BHigh tap densityLow effective concentrationElectrode thermal treatmentHigh energyLithium-ion battery

The invention provides a preparation method of high-tap-density metal oxide. The preparation method comprises the following steps: S1, dissolving metal salt with a solvent; adding an organic additive and uniformly mixing to prepare a precursor solution, wherein the solvent is one or two of de-ionized water and distilled water, and the organic additive is one or more of N,N-dimethylformamide, tartaric acid, acetic acid and dimethyl sulfoxide; S2, atomizing the spraying precursor solution in step S1 by utilizing an atomizer; conveying the precursor solution into a spraying pyrolyzing furnace by utilizing carrying gas, and carrying out pyrolysis; collecting a pyrolysis product by utilizing a powder collector, so as to obtain the high-tap-density metal oxide. The invention further provides the high-tap-density metal oxide prepared by the method and a high-energy-density lithium-ion battery. According to the preparation method provided by the invention, any auxiliary facility does not need to be added, and technology steps do not need to be added; prepared powder grains have good sphericility degree, are dense and compact and have high tap density; the preparation method has the advantages of simple operation, high efficiency, short flow and high practicability.

Owner:CENT SOUTH UNIV

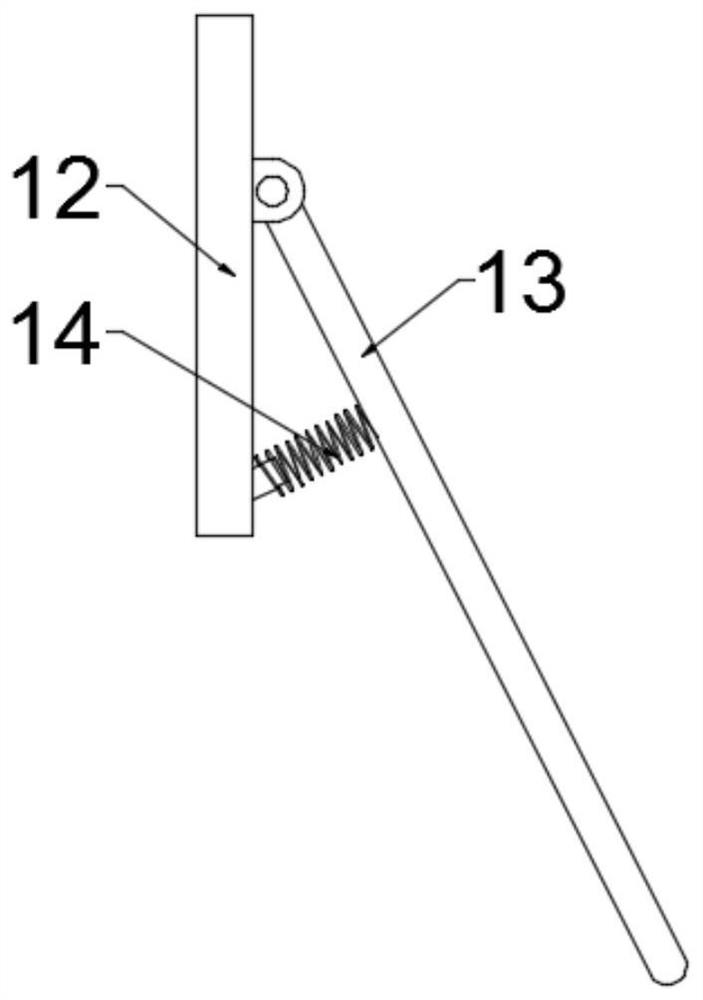

A kind of anti-adhesion radio frequency mechanical switch and preparation method thereof

ActiveCN111180837BSimple structureImprove reliabilityElectrostatic/electro-adhesion relaysElectric switchesCantilevered beamCoplanar waveguide

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

Layout structure and manufacturing method of trench type super junction device

ActiveCN104617133BAvoid Wafer WarpageOffset stressSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDislocation

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Gated diode and method of forming the same

ActiveCN107369710BIncrease distanceIncrease the lengthSemiconductor/solid-state device manufacturingSemiconductor devicesGate controlMaterials science

The present invention provides a grid-controlled diode and a formation method thereof. The formation method comprises: providing a substrate, and forming a plurality of fin portions; forming a first control structure, wherein the first control structure comprises of a plurality of first grids crossing the fin portions, and the part of the side wall and the top portion of the fin portions are coated with the first grids; and forming a first doped region and a second doped region. The first control structure is arranged between the first doped region and the second doped region, the first control structure comprises a plurality of the first grids, and the size of the first control structure along the extension directions of the fin portions is larger than the size of a single first grid. The arrangement of the first control structure can effectively increase a distance between the first doped region and the second doped region to effectively prolong the length of the current channel of the grid-controlled diode and effectively expand the depth of the current channel of the grid-controlled diode so as to effectively improve the current jamming problem of the grid-controlled diode and improve the device performances.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

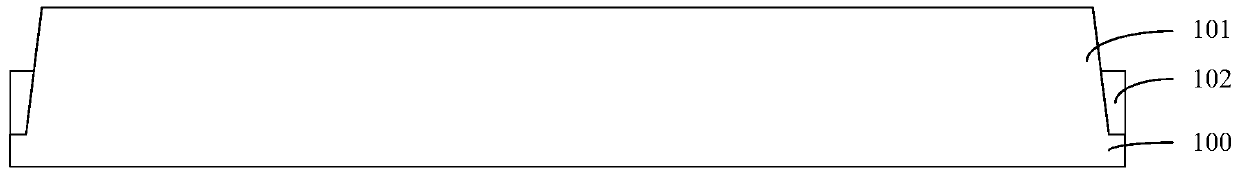

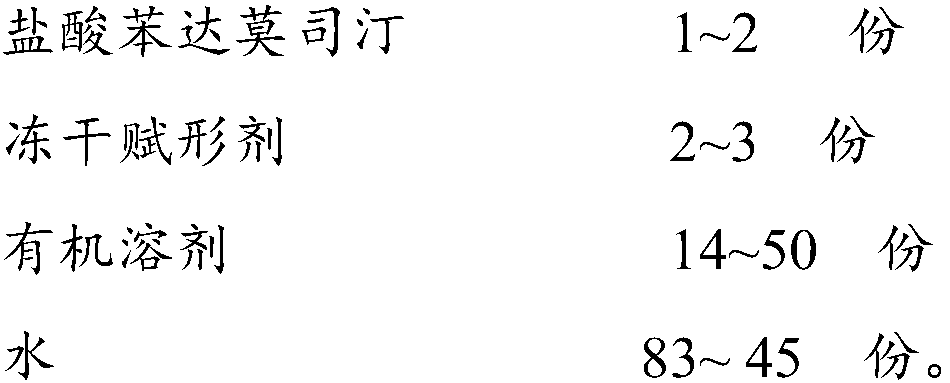

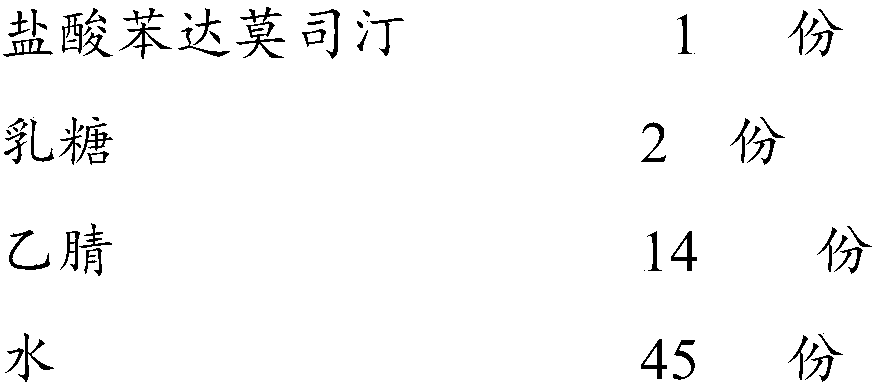

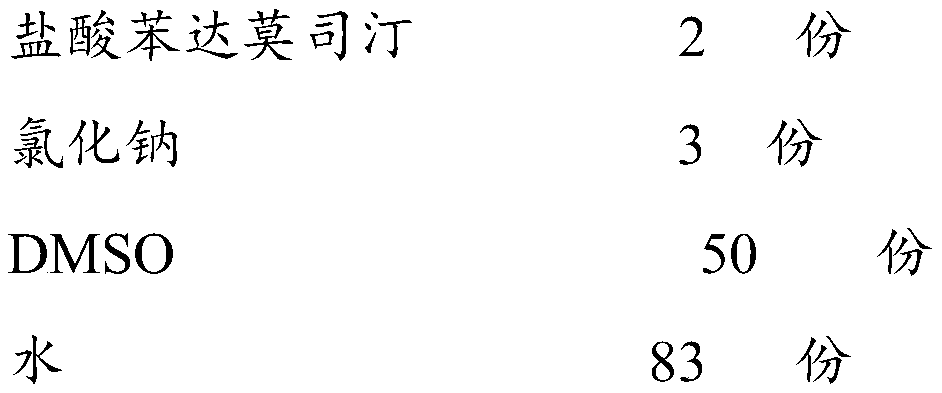

A kind of bendamustine hydrochloride freeze-dried powder injection and preparation method thereof

ActiveCN108078931BImprove stabilityImprove solubilityOrganic active ingredientsPowder deliveryOrganic solventBendamustine hydrochloride

The invention discloses a bendamustine hydrochloride freeze-dried powder injection. The freeze-dried liquid medicine is prepared from the following raw materials: 1 to 2 parts of bendamustine hydrochloride, 2 to 3 parts of freeze-dried excipients, 14 to 50 parts of organic solvents and 45 to 83 parts of water. The use of organic solvent formulations, low-temperature liquids, filling and freeze-drying techniques can effectively control the level of impurities in products.

Owner:KINDOS PHARM CO LTD +1

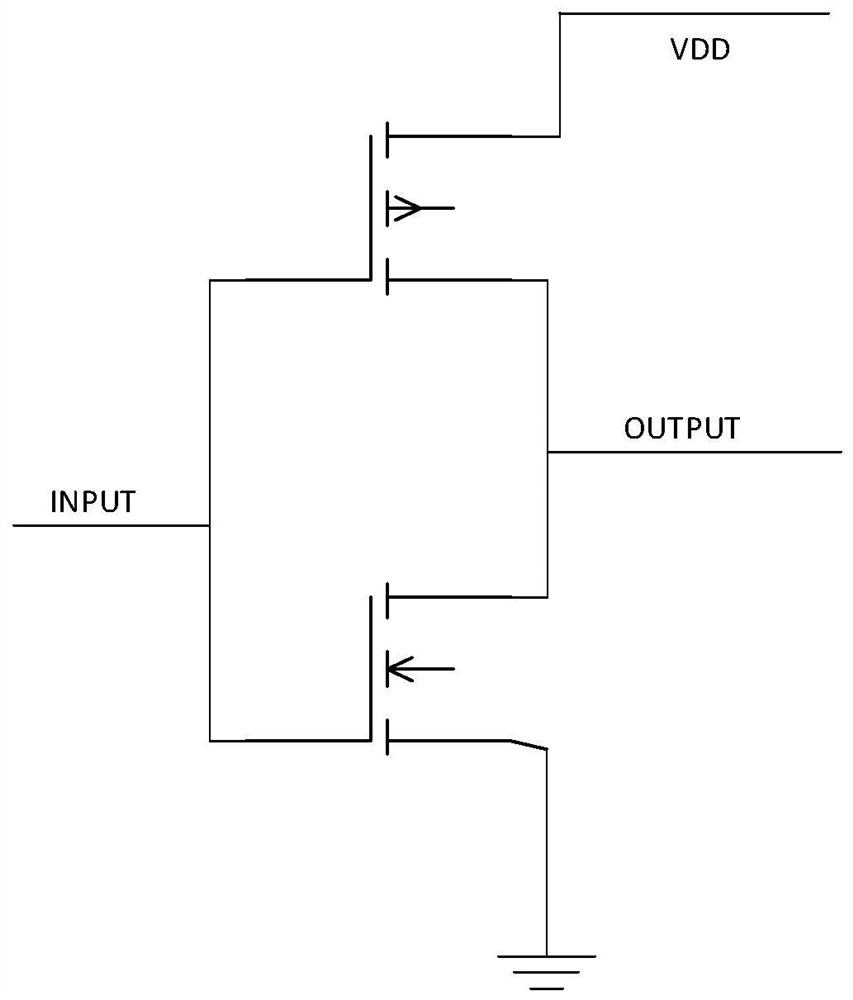

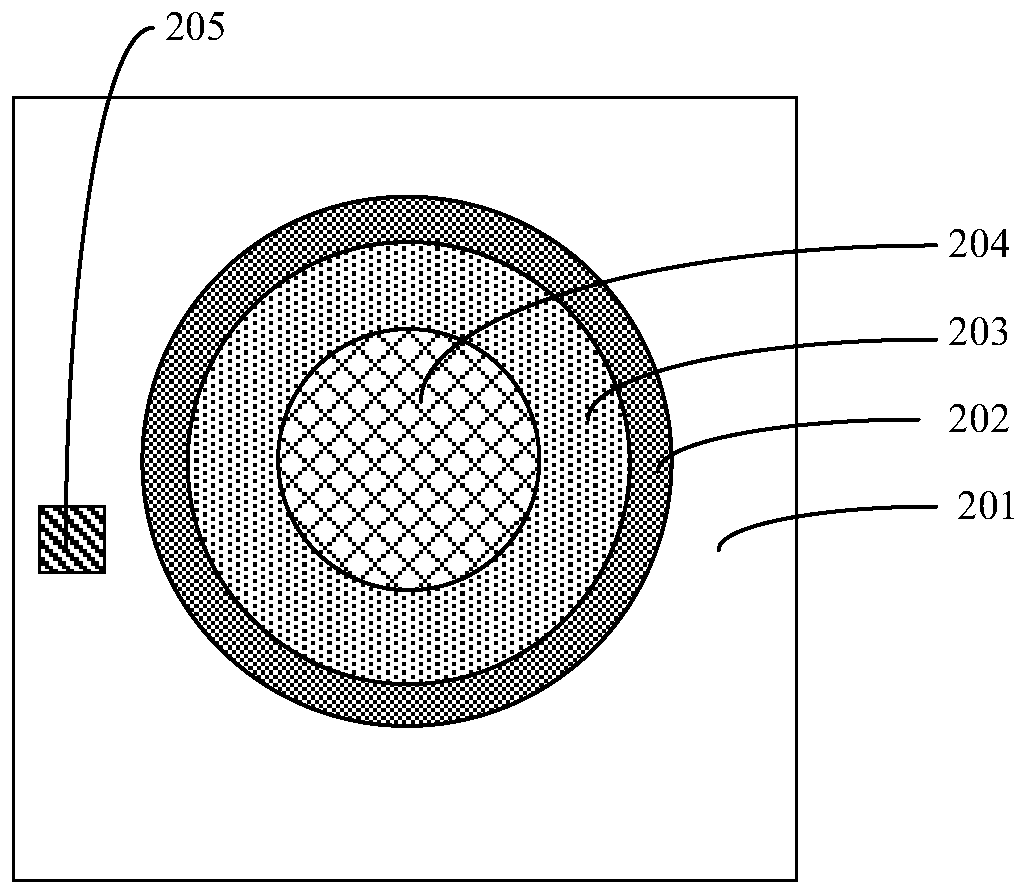

A graphene-based tunneling transistor, inverter and preparation method thereof

ActiveCN109461772BHigh speed responseImprove control abilityTransistorSemiconductor/solid-state device manufacturingHemt circuitsEngineering

Owner:SOUTHEAST UNIV

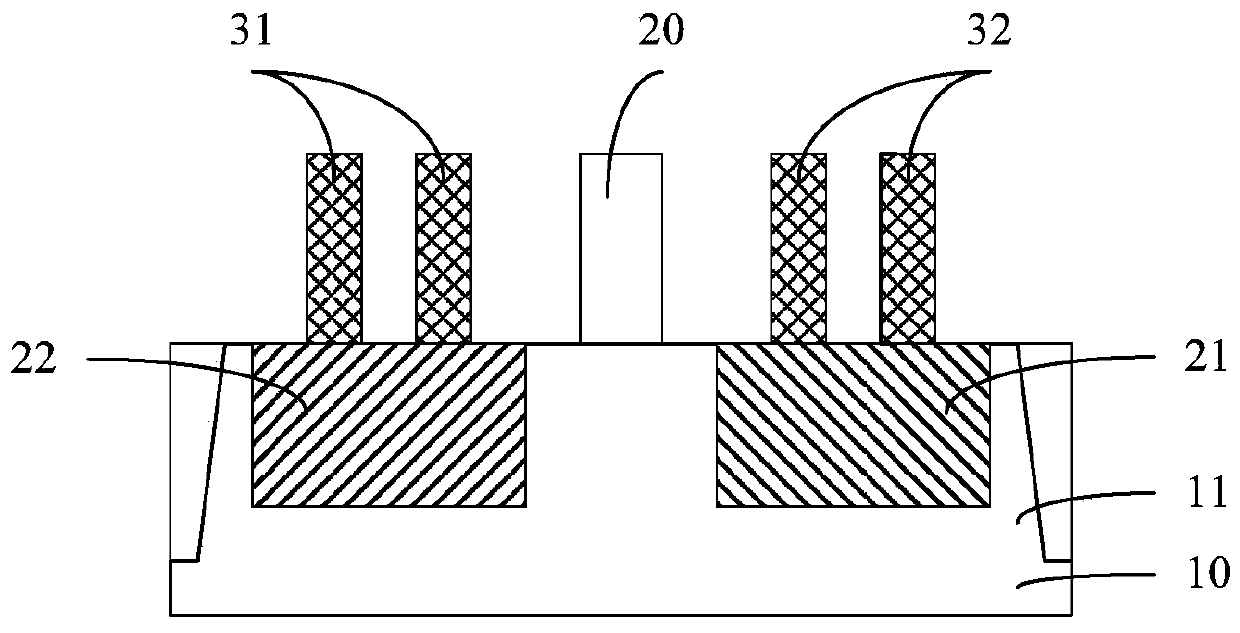

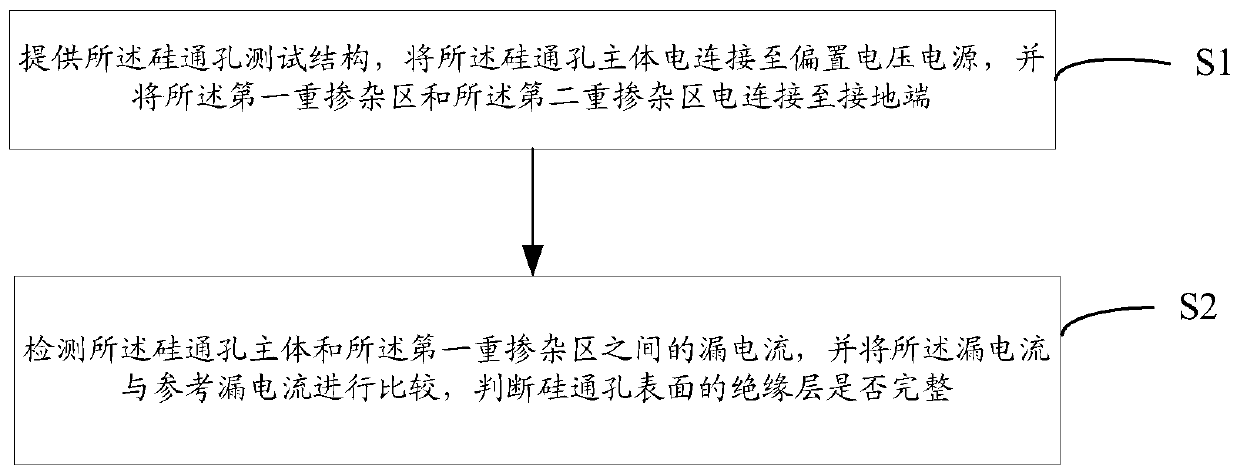

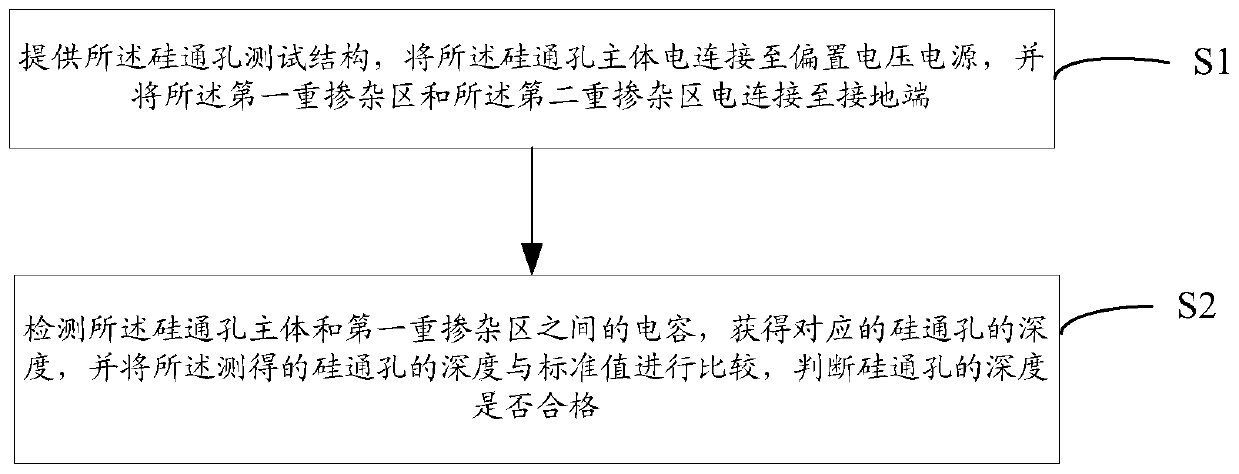

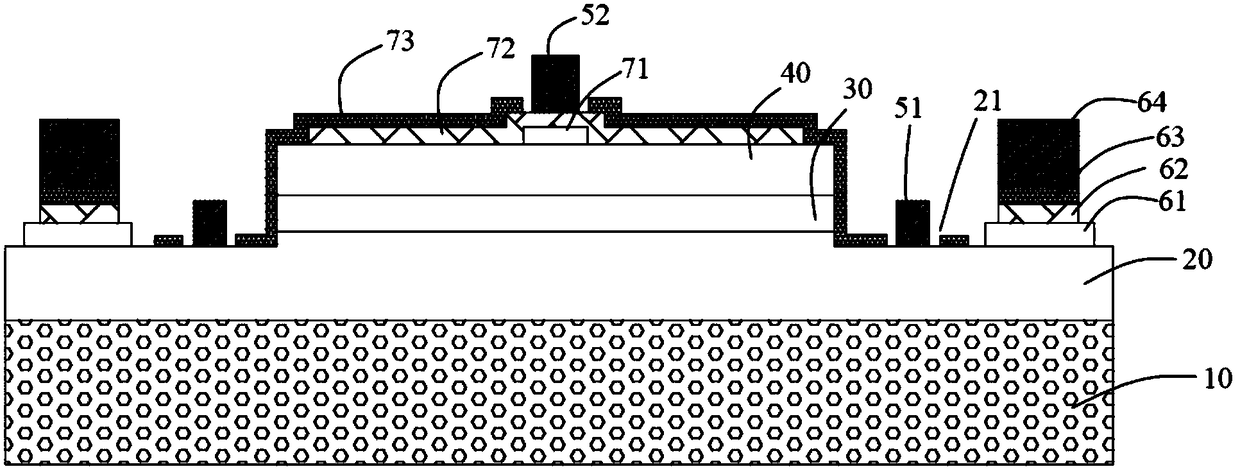

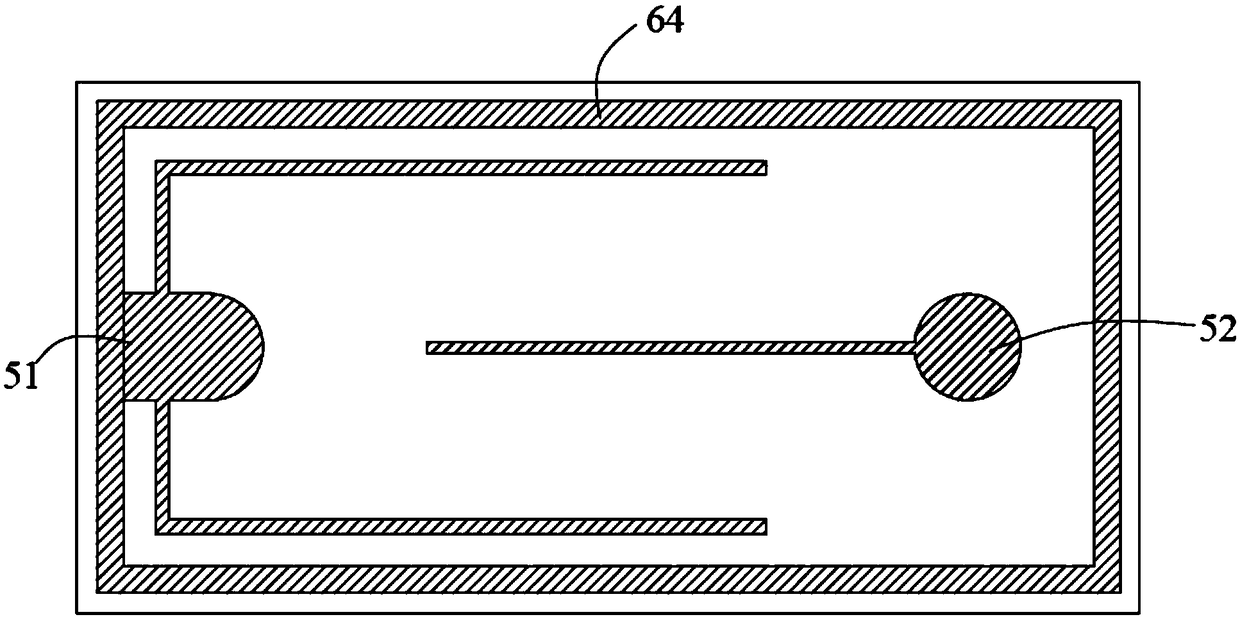

A through-silicon via test structure and test method thereof

ActiveCN107919291BNo additional process steps requiredSimple structureSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCapacitanceElectrical connection

The invention provides a silicon through hole testing structure and method, and the structure comprises a semiconductor substrate which is of a first conductive type; a silicon through hole which is located in the semiconductor substrate and comprises a through hole main body and an insulating layer from the inside to the outside; a first heavy doped region which is of a second conductive type, islocated in the semiconductor substrate and is set around the silicon through hole; a second heavy doped region which is of a first conductive type, is located in the semiconductor substrate and is set outside the first heavy doped region at intervals; and an interconnection structure which is electrically connected with the silicon through hole, the first heavy doped region and the second heavy doped region. The structure can measure whether there is a leaked current or not to judge whether an insulating layer is complete or not, and also can measure a capacitance value to judge whether the depth of the silicon through hole reaches a standard value or not. Moreover, the leaked current and the capacitance value are more accurate and sensitive, thereby achieving the more accurate testing ofwhether the insulating layer is complete or not and whether the depth of the silicon through hole reaches the standard value or not.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Phase inverter for tunneling transistor based on graphite, and preparation method thereof

ActiveCN109461772AHigh speed responseImprove control abilityTransistorSemiconductor/solid-state device manufacturingWork functionGraphite

The invention discloses a phase inverter for a tunneling transistor based on graphite, and a preparation method thereof. The graphene tunneling transistor comprises a source electrode, a grid electrode, a drain electrode, a graphene film, a semiconductor or metal substrate, a tunneling layer, a drain electrode insulating layer, a grid electrode insulating layer, a graphene passivation layer and adirect current bias voltage source, wherein the source electrode and a silicon substrate are connected, the drain electrode and the graphene film are connected, one tunneling layer is arranged betweenthe graphene and the substrate, and the grid electrode is arranged on the top of an electron tunneling part. If the work function of the semiconductor or metal substrate is small, the drain electrodeselects metal with a large work function, and the device is of an n type; and otherwise, the drain electrode adopts the metal with the large work function, and the device is of a p type. The p-type pipe drain electrode is connected with a high level, an n-type pipe source electrode is connected with a low level, the common grid electrode of two pipes serves as the input end of a circuit, and a p-type pipe source electrode and an n-type pipe drain electrode are connected to serve as the output end of the circuit. By use of the novel graphene tunneling transistor structure, a digital logic phase inverter with a high response rate and low static power consumption is realized.

Owner:SOUTHEAST UNIV

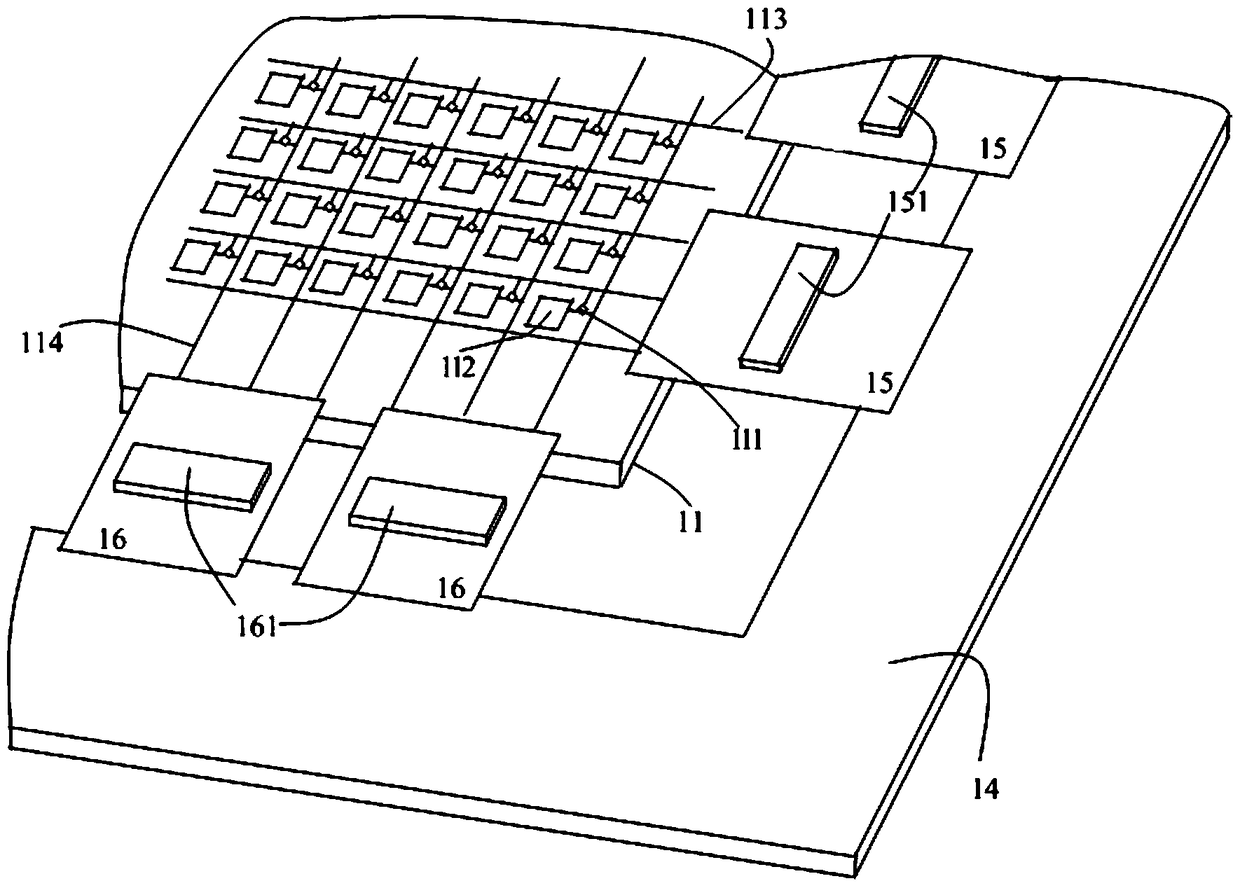

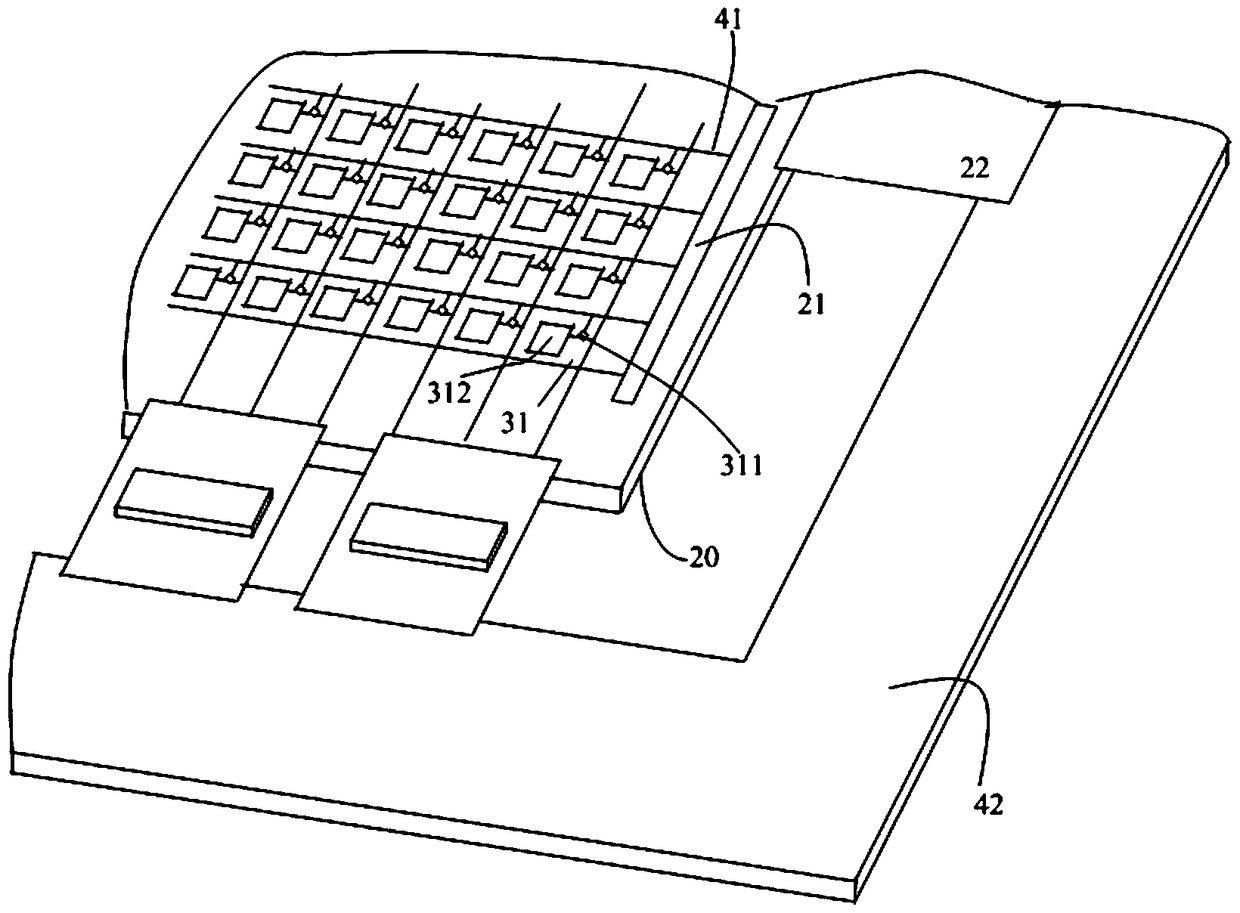

Area array sensor device and method of forming the same

ActiveCN105336752BSmall footprintImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringElectrical and Electronics engineering

Owner:SHANGHAI OXI TECH

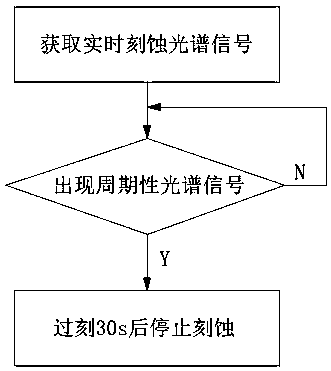

An endpoint monitoring method for backhole etching of high electron mobility transistors

ActiveCN106505007BImprove visibilityHigh sensitivitySemiconductor/solid-state device testing/measurementEtchingMonitoring system

The invention provides a terminal point monitoring method of high-electron-mobility transistor back hole etching. Two kinds of metal are alternatively grown on a wiring layer of a device right side technology so as to form a periodic metal layer. The periodic metal layer is located above a position of a back side through hole to be etched. The terminal point monitoring method comprises the following steps of S1, acquiring a real-time etching spectrum signal; S2, determining whether to generate a periodic spectrum signal; S3, if the periodic spectrum signal is generated, stopping etching after 30s over etching; and S4, if the periodic spectrum signal is not generated, repeatedly executing the step S2. In the invention, through a periodic lamination design wiring a periodic metal layer in a right side, an identification degree and sensitivity of a terminal point signal of a terminal point monitoring system are increased and accuracy and validity of terminal point decision are increased too; the method is especially suitable for silicon-carbide-based gallium nitride high-electron-mobility transistor back hole etching with an exposed area proportion which is not high (<2%); and technology reliability of back hole etching can be obviously improved and a high practical value is possessed.

Owner:CHENGDU HIWAFER SEMICON CO LTD

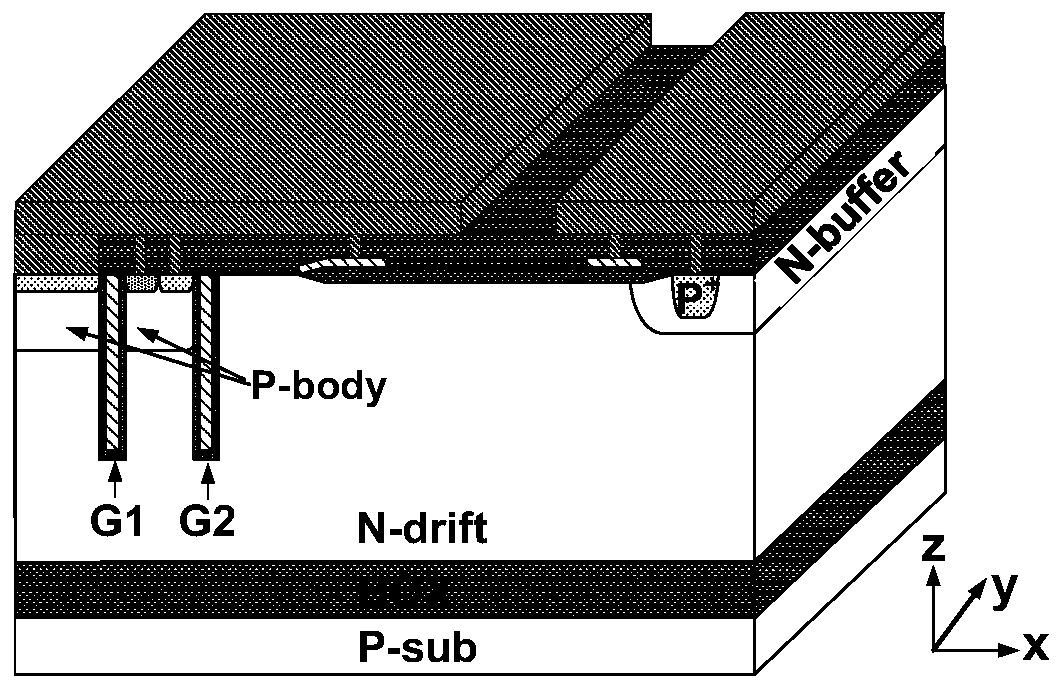

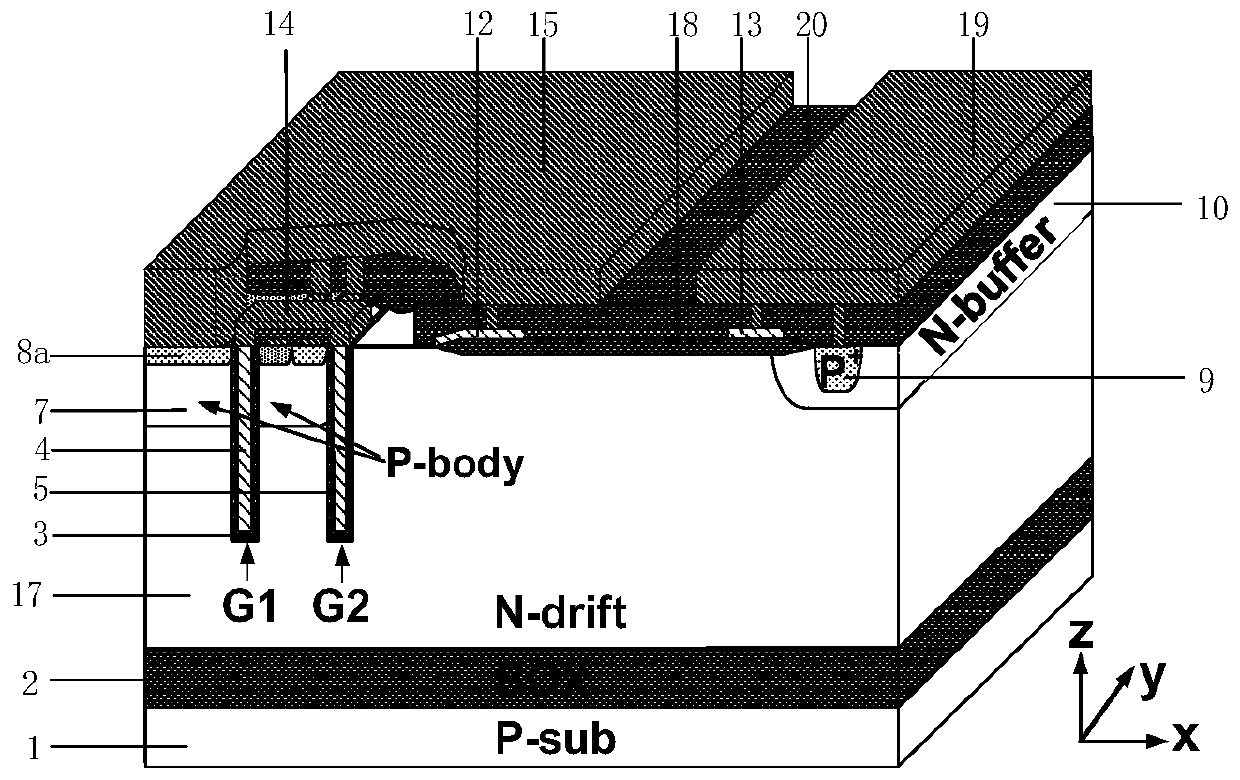

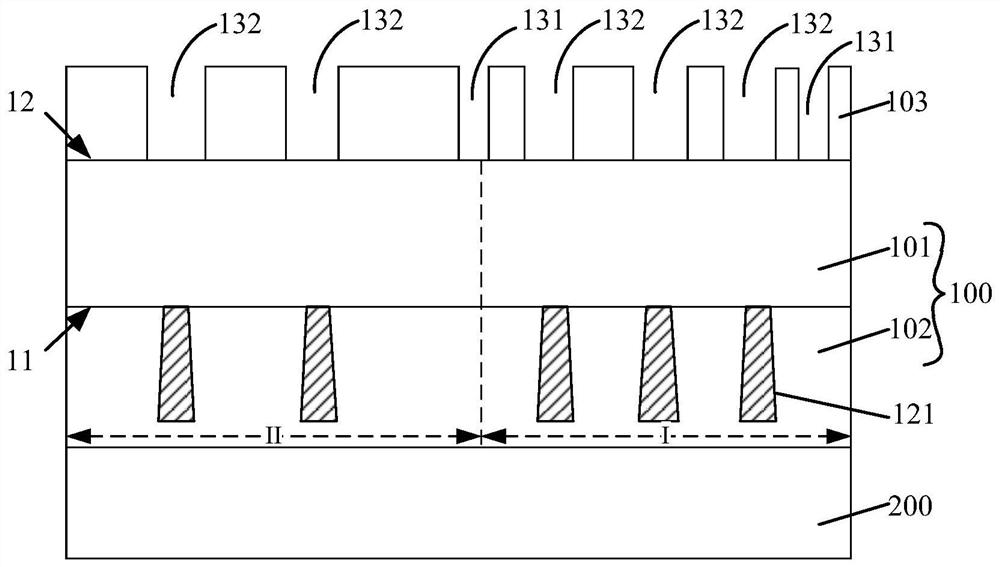

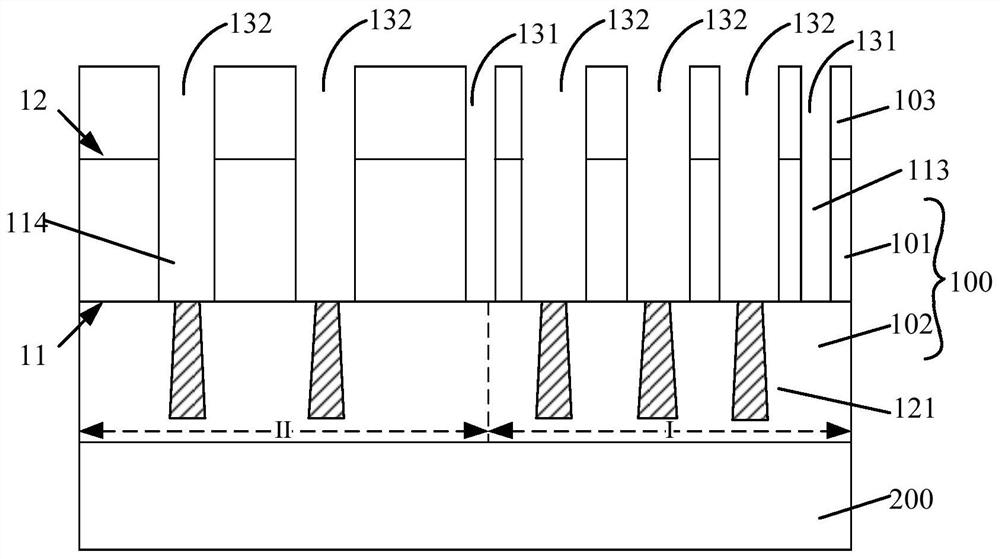

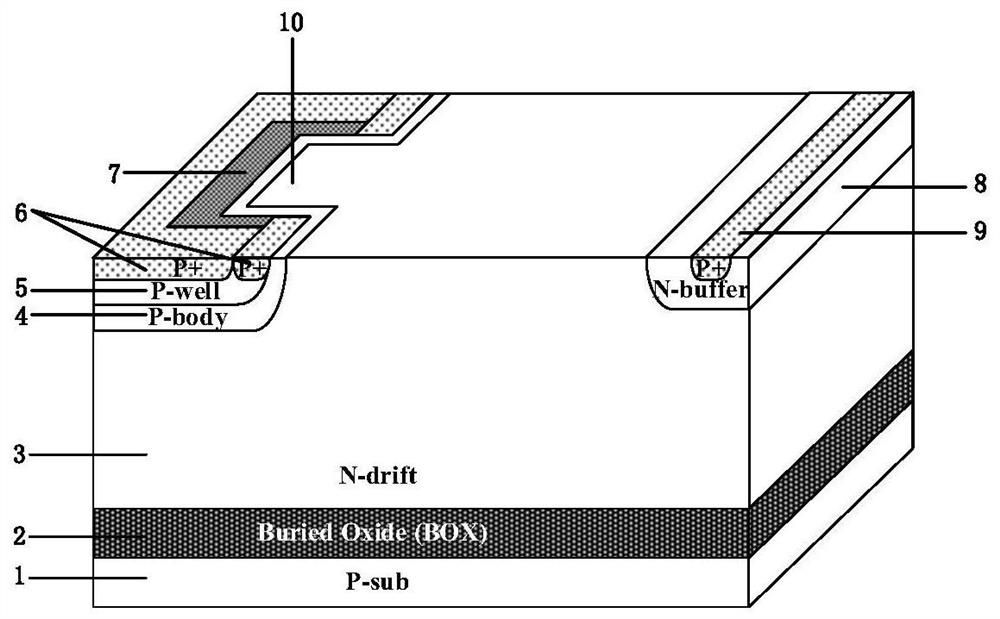

Trench gate type silicon-on-insulator lateral insulated gate bipolar transistor device

ActiveCN110729345AImprove controlFast switching speedEfficient power electronics conversionSemiconductor devicesSquare waveformEngineering

The invention discloses a trench gate type silicon-on-insulator transverse insulated gate bipolar transistor device. According to the device of the invention, buried oxide is arranged on a P-type substrate; an N-type drift region is arranged on the buried oxide; a P-type body region and an N-type buffer region are arranged on the N-type drift region; a P-type collector region is arranged in the N-type buffer region; a square-wave-shaped heavily-doped N-type emitter region and a square-wave-shaped heavily-doped P-type emitter region are arranged in the P-type body region side by side; and a first square-wave-shaped longitudinal trench and a second square-wave-shaped longitudinal trench are formed on two sides of the square-wave-shaped heavily-doped N-type emitter region and the square-wave-shaped heavily-doped P-type emitter region; the first longitudinal trench is provided with a first polycrystalline silicon layer wrapped by a voltage-withstanding medium; a portion of the second longitudinal trench, which is parallel to the heavily doped P-type collector region, is filled with a second polycrystalline silicon layer wrapped by a voltage-withstanding medium; and a portion of the second longitudinal trench, which is located in a direction from the heavily-doped N-type emitter region to the heavily-doped P-type collector region, is filled with a third polycrystalline silicon layerand an oxide block body, wherein the third polycrystalline silicon layer is wrapped by a voltage-withstanding medium, and the oxide block body is positioned above the third polycrystalline silicon layer; and the second polycrystalline silicon layer is connected with the third polycrystalline silicon layer.

Owner:SOUTHEAST UNIV

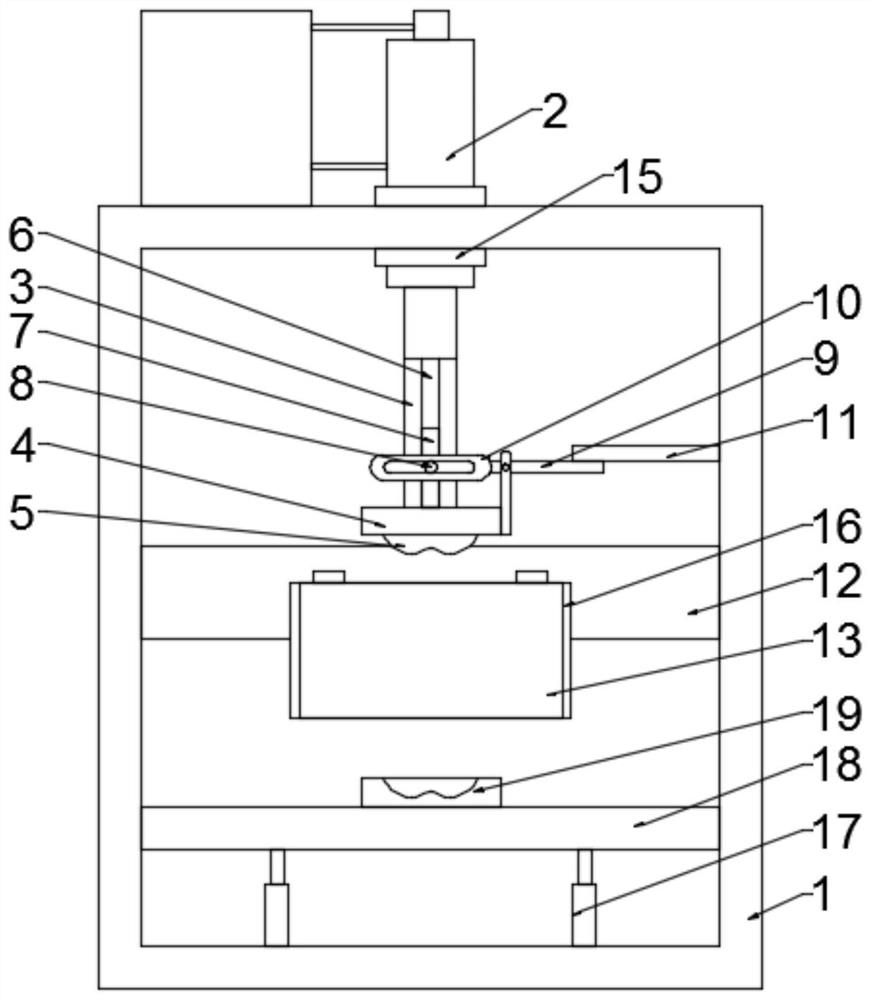

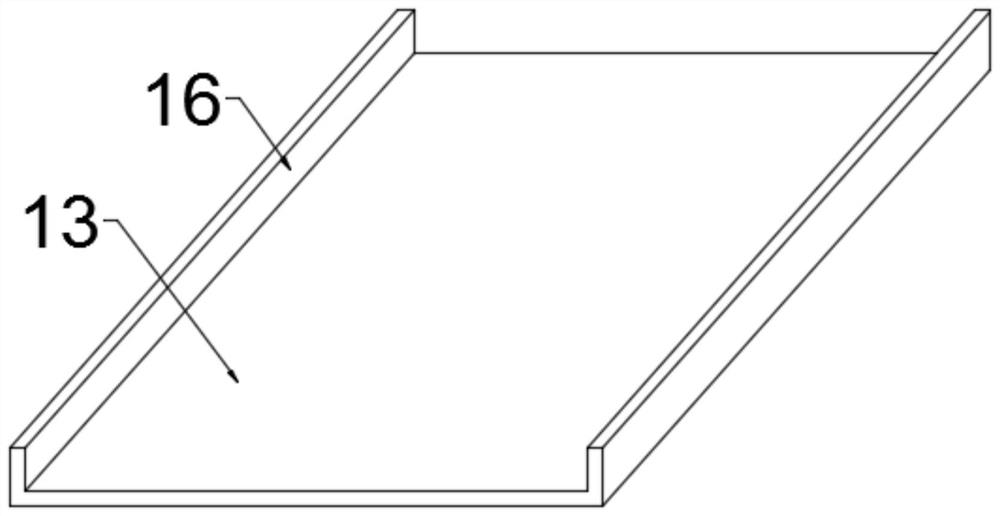

A stamping equipment for mechanical stamping parts

The invention discloses stamping equipment used for mechanical stamped parts, and relates to stamping equipment. The stamping equipment comprises a frame, a hydraulic oil cylinder is fixedly connectedto the top of the frame, a connecting rod is fixedly connected to the output end of the hydraulic oil cylinder, a stamping upper die is fixedly connected to the bottom of the connecting rod through ahorizontal seat, the connecting rod is made of a nonferromagnetic material, a sliding groove is formed in the middle of the connecting rod, a magnet is slidably connected to the inner side of the sliding groove, and a transmission rod is fixedly connected to the middle of the front side of the magnet. A swing rod is rotationally connected to the right side of the connecting rod through a verticalrod, a transmission groove is fixedly connected to the left side of the swing rod, the transmission groove sleeves the outer side of the transmission rod, a limiting stop rod is fixedly connected tothe right side of the frame, and the limiting stop rod is matched with the right end of the swing rod. The stamping equipment is simple in structure and convenient to use, the stamped parts are stamped through hydraulic driving during use, the machined stamped parts can be effectively and rapidly discharged through the up-and-down movement of a plunger rod after stamping is completed, and processsteps do not need to be added.

Owner:RUIAN VEHICLE FITTING FACTORY

LED chip with capacitive structure and preparation method thereof

ActiveCN106784173BPlay a protective effectImprove reliabilitySemiconductor devicesCapacitanceQuantum well

Owner:FOCUS LIGHTINGS SCI & TECH

Anti-sweat fabric

InactiveCN108656646AGood hygroscopicityMoisture absorptionGarment special featuresLayered productsSurface layerMoisture absorption

The invention discloses anti-sweat fabric. The anti-sweat fabric has the characteristics of comprising the following materials: in percent by mass, 15-27% of colored cotton, 33-45% of hemp fiber, 15-37% of nylon, 8-16% of wool fiber, 3-4% of fluon and 5-17% of copper ammonia fiber, wherein the colored cotton and nylon are blended so that the obtained substance is adopted as the inner layer of anti-sweat fabric, the hemp fiber and wool fiber are blended so that the obtained mixture is adopted as the interlayer of the anti-sweat fabric, and the copper ammonia fiber and fluon are blended so thatthe obtained matter is adopted as the surface layer of the anti-sweat fabric. The anti-sweat fabric has the advantages of light, thin and comfortable fabric and a good effect of moisture absorption, and by applying different raw materials to different positions, the functions of moisture absorption, drying and heat preservation are achieved; if the product is not worn no longer after use is conducted, self degradation can be achieved after a period of time, so that time-labor saving and environmental protection are achieved; the product has low production cost, the production process is simple, no addition of other process steps is needed, so that the production efficiency is improved.

Owner:NANTONG DISONG TEXTILE CO LTD

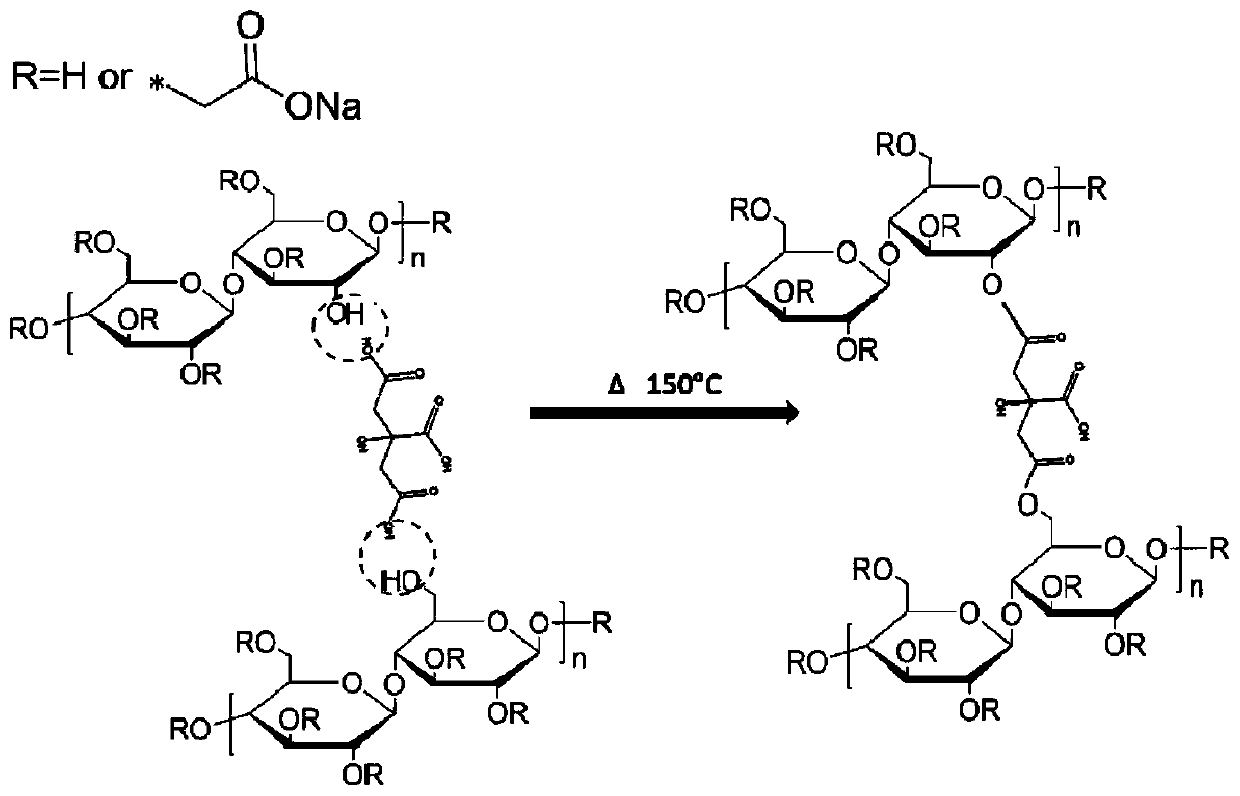

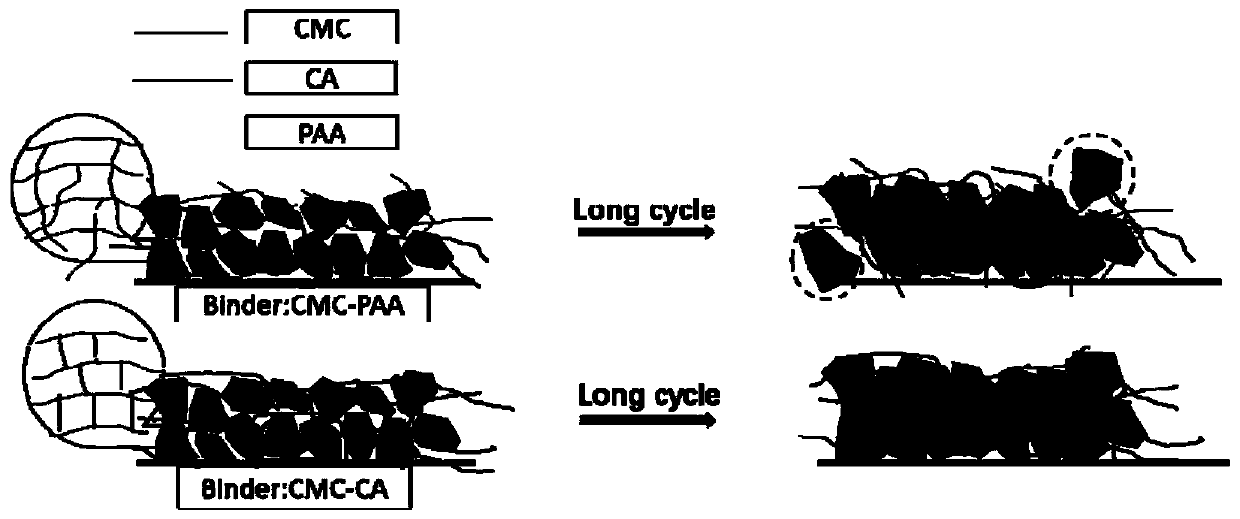

Three-dimensional network type aqueous binder, preparation method thereof and electrode plate

PendingCN111540903AInhibition of volume changeEasy to fixSecondary cellsElectrode collector coatingCarboxymethyl celluloseCellulose

The invention relates to an electrode binder, and particularly discloses a three-dimensional network type aqueous binder, a preparation method thereof and an electrode plate. The three-dimensional network type aqueous binder is of a three-dimensional network type molecular structure formed by a bonding reaction between a water-based binder and citric acid (CA), and the water-based binder is carboxymethyl cellulose (CMC) and / or sodium carboxymethyl cellulose (NaCMC). According to the invention, regulation and control of the network spacing of the binder are realized by utilizing the bilateral cooperation of small molecular citric acid, so that the ligand utilization efficiency is improved, and the fixing effect of the binding network is enhanced. By improving the production process, large-scale application can be realized without increasing process steps, and electrode pulverization and shedding of silicon-carbon negative electrodes and other negative electrode materials with large volume change in the cycle process can be effectively prevented, so that the cycle performance is improved, and the service life is prolonged.

Owner:桑顿新能源科技(长沙)有限公司

Memory structure and method of forming the same

ActiveCN112567514BImprove performanceReduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingParasitic capacitorEngineering

The present invention relates to a memory structure and a forming method thereof. The memory structure includes: a first base, including: a substrate layer and a storage layer, the substrate layer has a first surface and a second surface opposite to each other, and the storage layer is located on On the first surface of the substrate layer, the first substrate includes a pad area; a dielectric layer located on the second surface of the substrate layer; a solder pad located on the surface of the dielectric layer on the pad area; isolation The structure penetrates through the substrate layer, is located at the edge of the pad region, surrounds the substrate layer in the pad region, and is used to isolate the substrate layer in the pad region from the substrate layer around the isolation structure. In the memory structure of the present invention, the parasitic capacitance between the pad and the substrate layer is reduced, which is beneficial to improving memory performance.

Owner:YANGTZE MEMORY TECH CO LTD

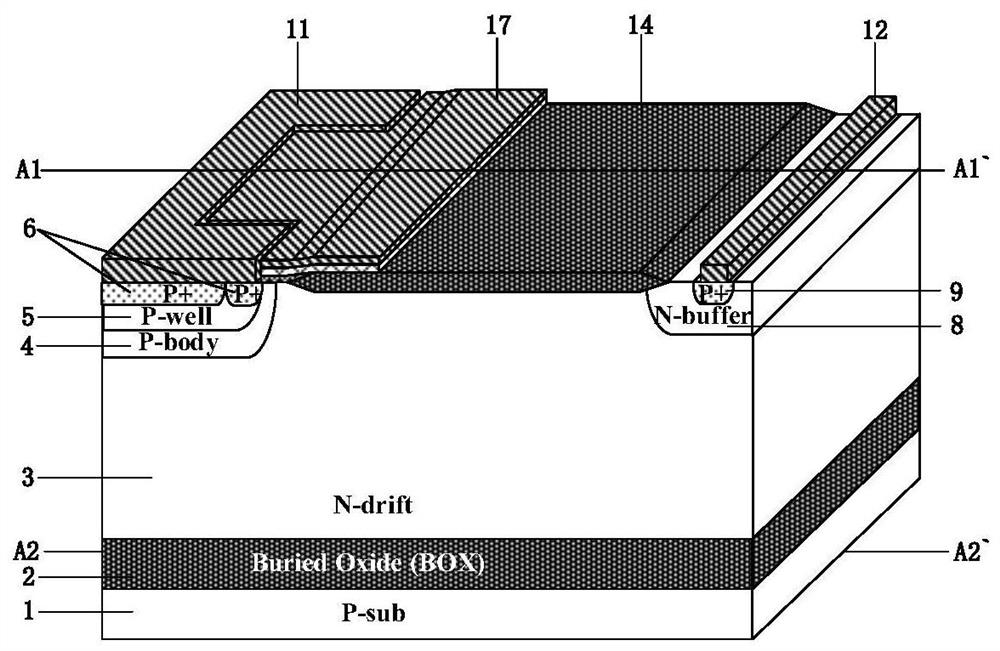

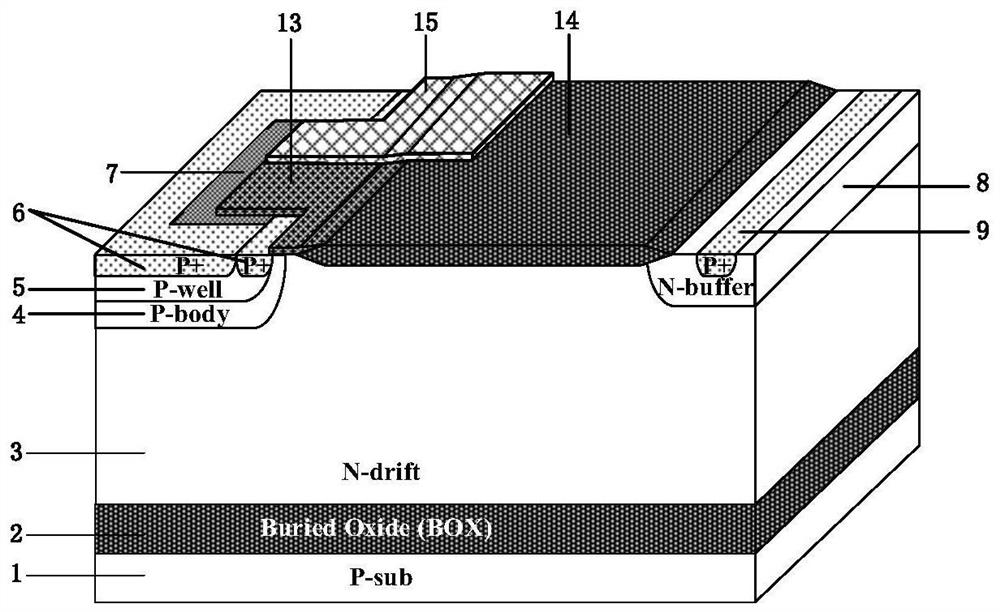

A Lateral Insulated Gate Bipolar Transistor with Low Turn-on Overshoot Current

ActiveCN110190120BNo drop in current capabilityCurrent capability does not affectThyristorEngineeringPolysilicon gate

A lateral insulated gate bipolar transistor with low turn-on overshoot current reduces the current peak value flowing through the device when the second gate pulse is turned on without reducing the current capability and withstand voltage capability. The semiconductor has: a buried oxygen on a P-type substrate, an N-type drift region on the buried oxygen, a P-type body region and an N-type buffer zone on it, and a P-type collector in the N-type buffer zone region, a field oxygen layer is provided above the N-type drift region, a P-type well region is provided in the P-type body region, a P-type emitter region and an emitter region are arranged in the P-type well region, and the inside of the above-mentioned 4 regions The boundary is synchronously invaginated to form a pinch-off region. The surface of the P-type body region is provided with a gate oxide layer, and the gate oxide layer is provided with a polysilicon gate electrode, and the polysilicon gate electrode is composed of the first gate electrode located above the surface of the P-type body region and the pinch-off region and the N-type drift region. Composed of the second grid electrode, the first grid electrode is connected to the first grid resistor, and the second grid electrode is connected to the second grid resistor.

Owner:SOUTHEAST UNIV