Memory structure and method of forming the same

A memory and storage layer technology, which is applied in the manufacturing of semiconductor devices, electric solid state devices, and semiconductor/solid state devices, etc., can solve the problems of increasing process difficulty, circuit breakage, and process cost increase, and achieves the goal of reducing process difficulty, improving performance, and saving Process cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

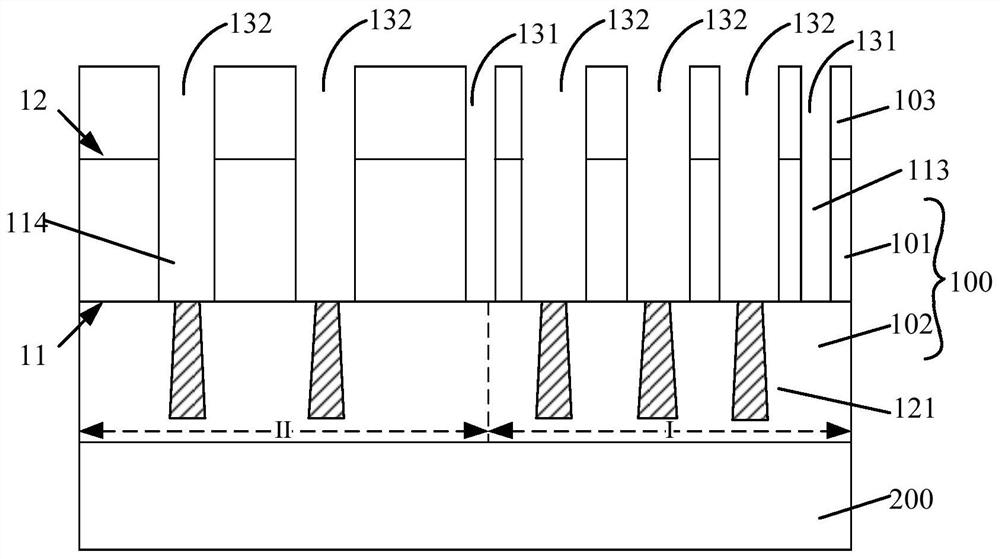

[0031] The specific implementation of the memory structure and its forming method provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

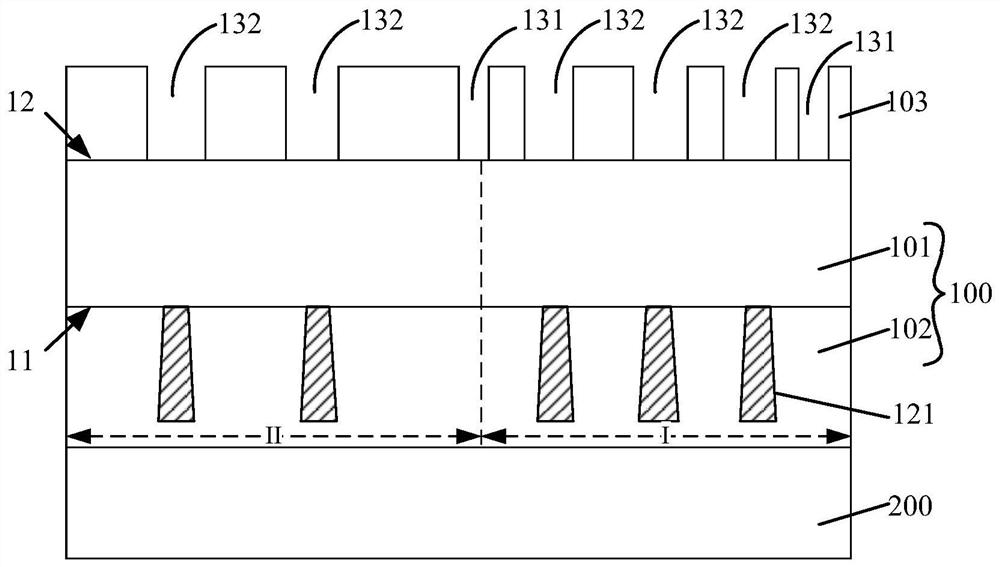

[0032] Please refer to Figure 1 to Figure 7 , is a structural schematic diagram of the forming process of the memory structure according to a specific embodiment of the present invention.

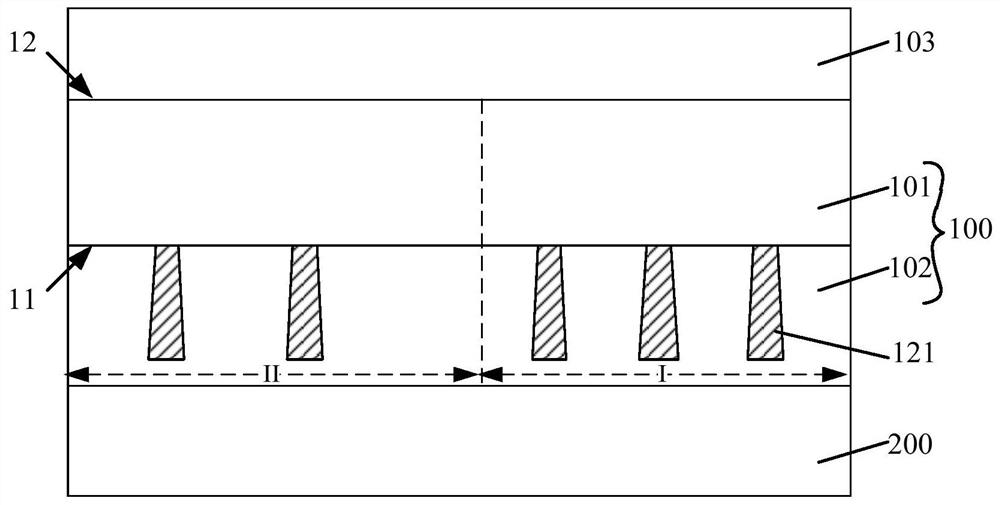

[0033] Please refer to figure 1 , providing a first substrate 100, comprising: a substrate layer 101 and a storage layer 102, the substrate layer 101 has a first surface 11 and a second surface 12 opposite to each other, and the storage layer 102 is located on the first surface of the substrate layer 101 11 , the first substrate 100 includes a pad region I; a dielectric layer 103 is formed on the second surface 12 of the substrate layer 101 .

[0034] figure 1 In this case, the first substrate 100 is in an upside-down state, at this time, the first surface 11 of the substrate layer 101 is t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More