A Lateral Insulated Gate Bipolar Transistor with Low Turn-on Overshoot Current

A bipolar transistor and overshoot current technology, which is applied in thyristors, circuits, electrical components, etc., can solve problems such as slowing down of device switching speed, increase of gate capacitance, and overshoot of gate voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

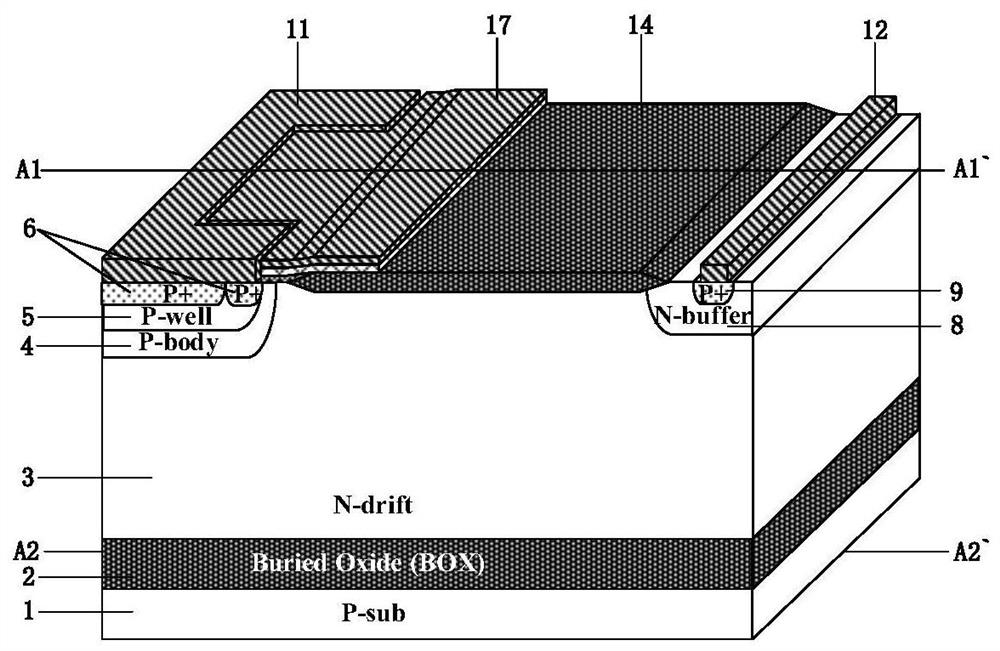

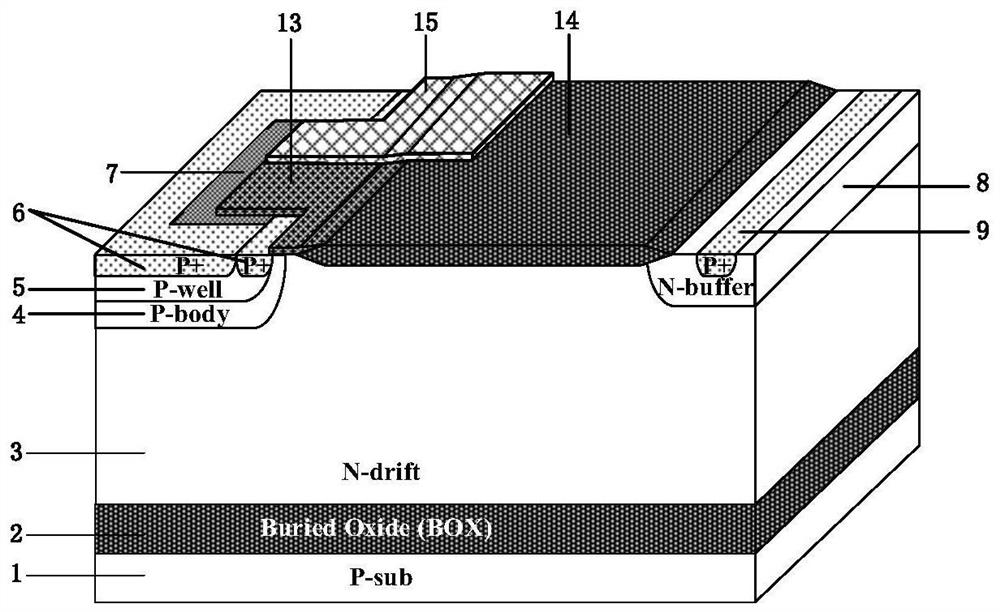

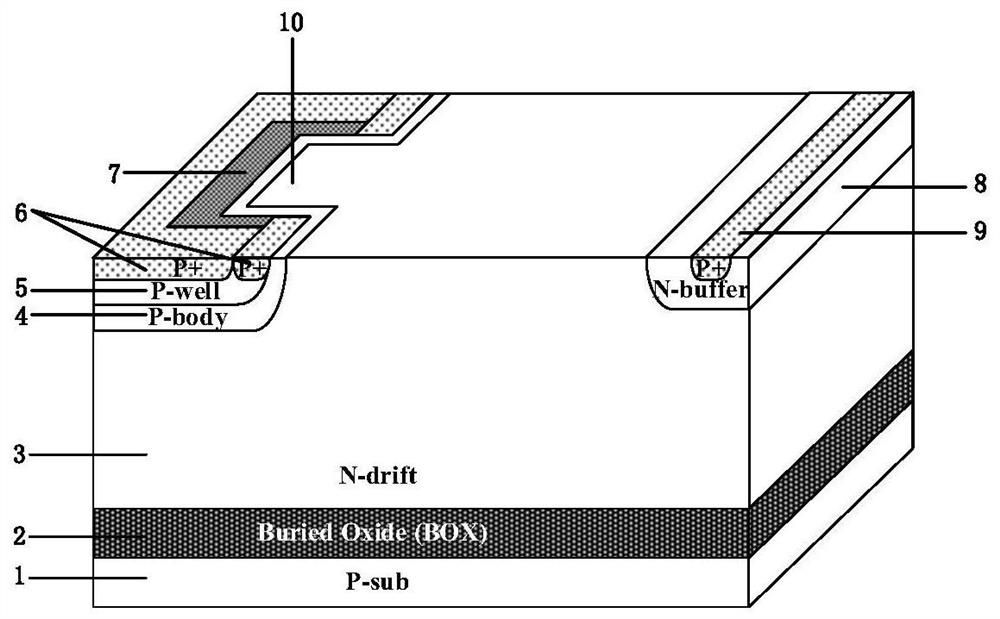

[0029] Combine below Figure 4 , Figure 5 , Figure 6 , Figure 7 , the present invention is described in detail:

[0030]A lateral insulated gate bipolar transistor with low turn-on overshoot current, comprising: a P-type substrate 1, a buried oxide layer 2 is arranged on the P-type substrate 1, and an N-type drift is arranged on the buried oxide layer 2 Zone 3, a P-type body zone 4 and an N-type buffer zone 8 are respectively provided on both sides of the N-type drift zone 3, a field oxide layer 14 is provided above the N-type drift zone 3, and a field oxide layer 14 is provided in the N-type buffer zone 8. There is a heavily doped P-type collector region 9, and a collector metal 12 is connected to the heavily doped P-type collector region 9, and the collector metal 12 is connected to the first peripheral terminal 19a, and in the P-type body region 4 There is a P-type well region 5 inside, and a heavily doped P-type emitter region 6 and a heavily doped N-type emitter re...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistance | aaaaa | aaaaa |

| electrical resistance | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More