A read/write circuit of a parallel interface and a data read/write method

A read-write circuit, data read-write technology, applied in the direction of electrical digital data processing, CAD circuit design, special data processing applications, etc., can solve the stringent requirements for read and write timing, deviation, signal quality susceptible to system interference or design factors issues such as the impact of

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The following will clearly and completely describe the technical solutions in the embodiments of the present application with reference to the drawings in the embodiments of the present application, although the described embodiments are only some of the embodiments of the present application, not all of them. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of this application.

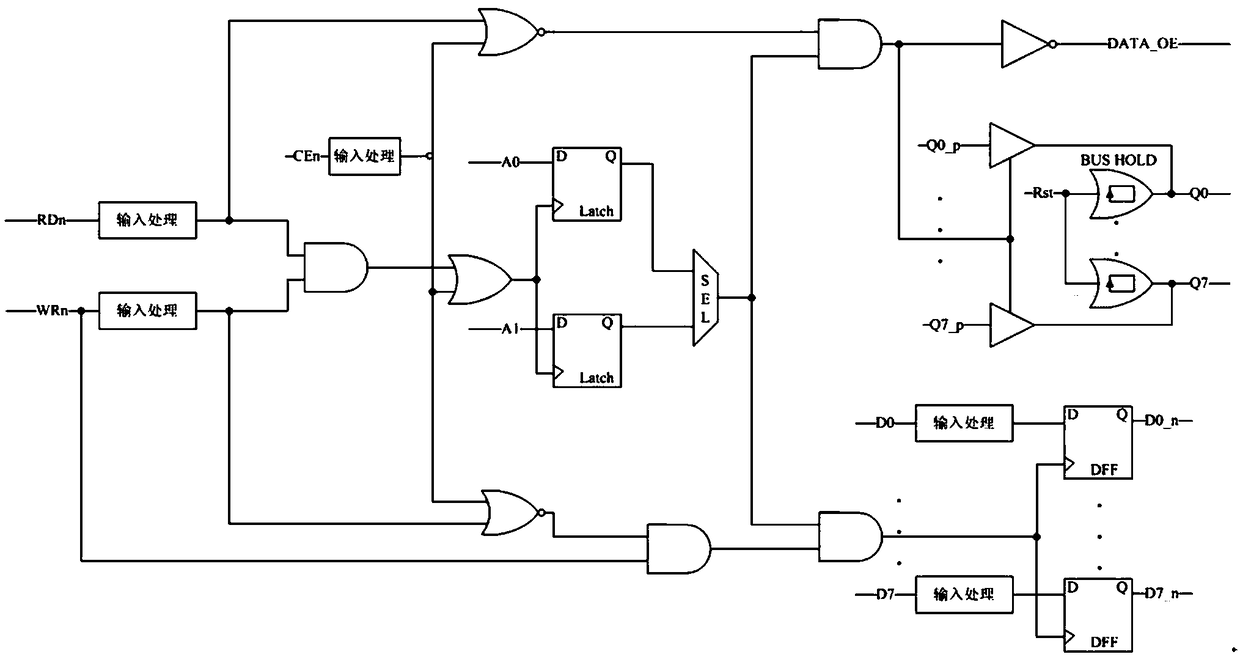

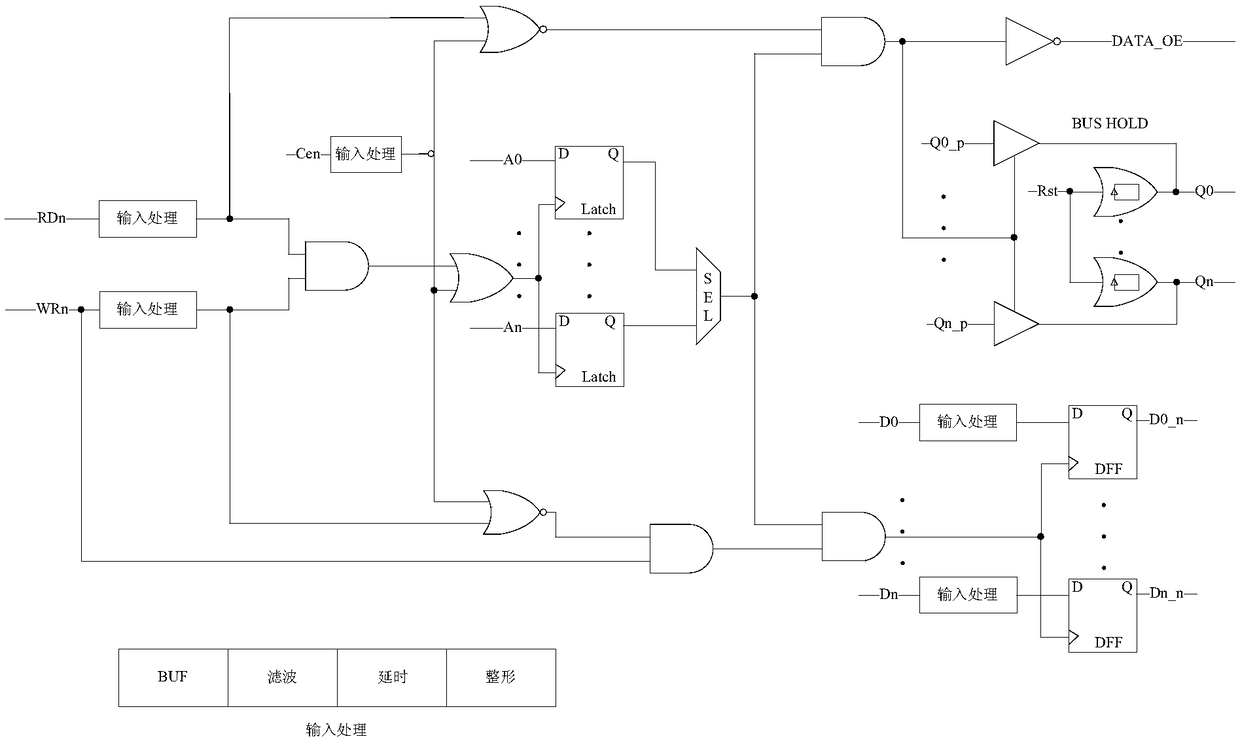

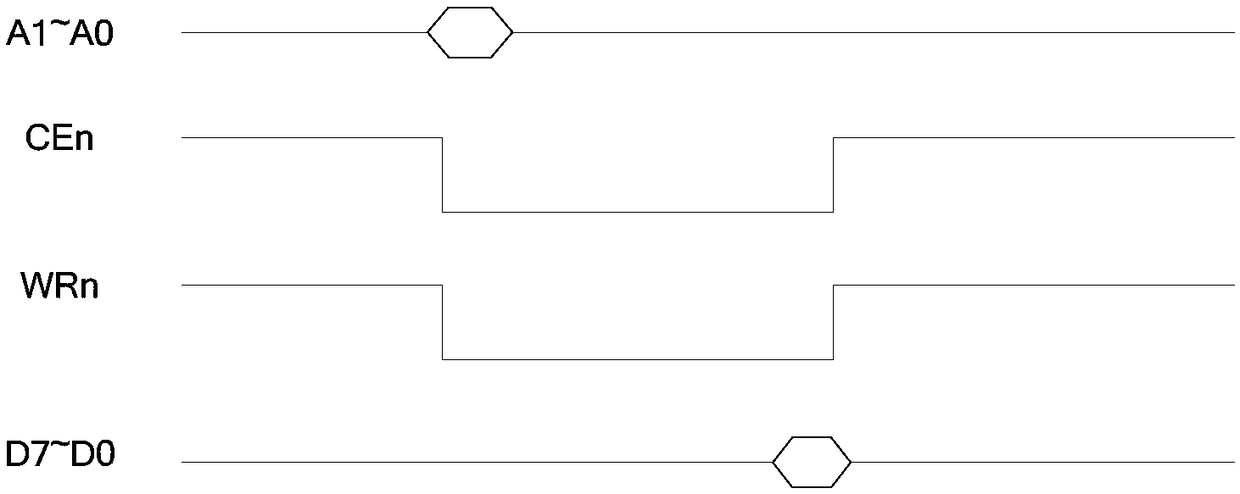

[0027] Such as figure 1 As shown, a parallel interface read-write circuit includes an input processing unit and an address latch group connected to the input processing unit, a data flip-flop group and a BUS HOLD unit; the output end of the address latch group is connected with a SEL unit, The output end of the SEL unit is connected to the clock input end of the data flip-flop group;

[0028] The input processing unit is used to filter, delay and reshape the input...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More