Ceramic capacitor for reducing parasitic inductance

A ceramic capacitor and parasitic inductance technology, applied in the direction of multilayer capacitors, fixed capacitor electrodes, fixed capacitor dielectrics, etc., can solve problems such as large parasitic inductance, reduce the existence of internal parasitic inductance, reduce parasitic inductance, and reduce the transmission path. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

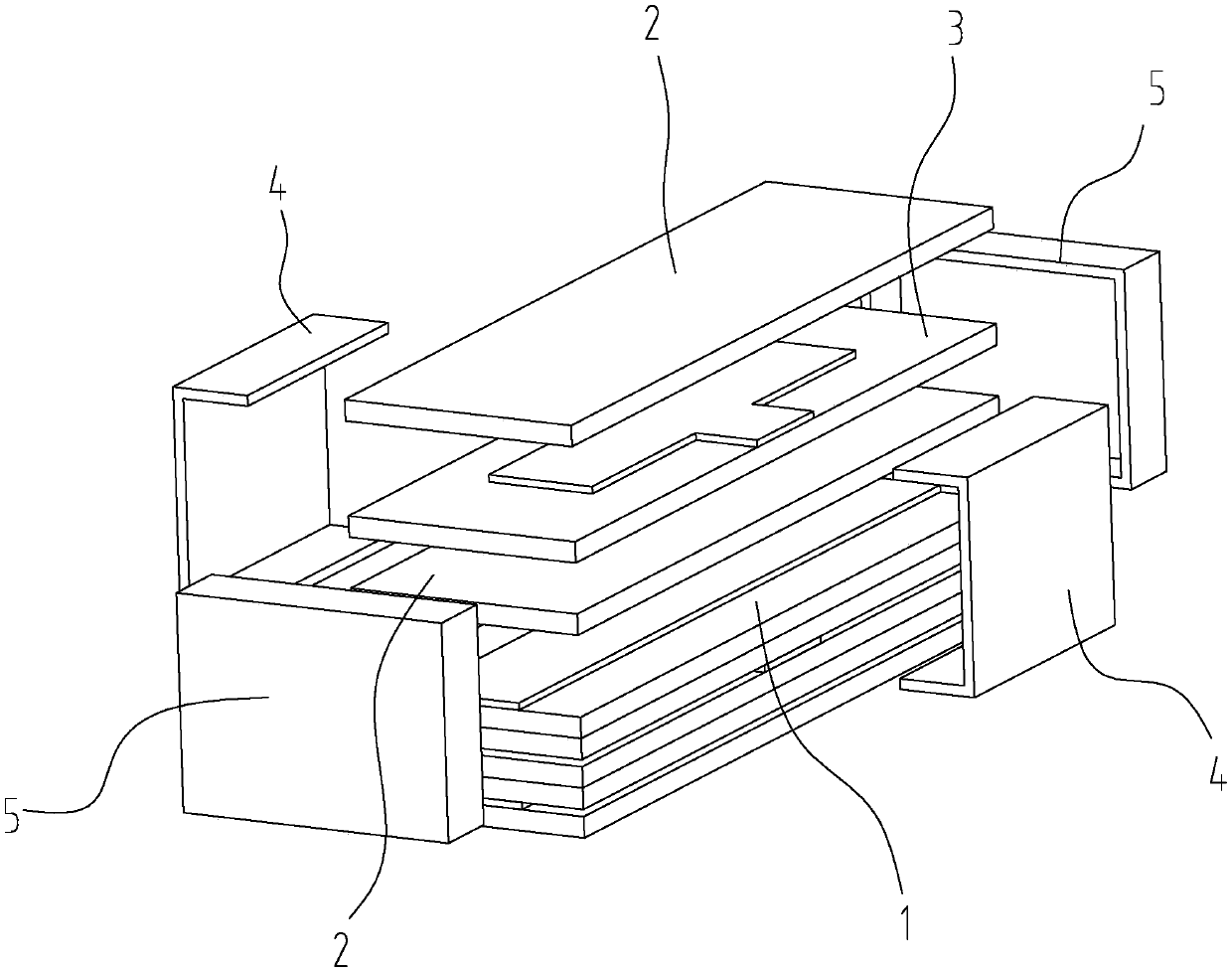

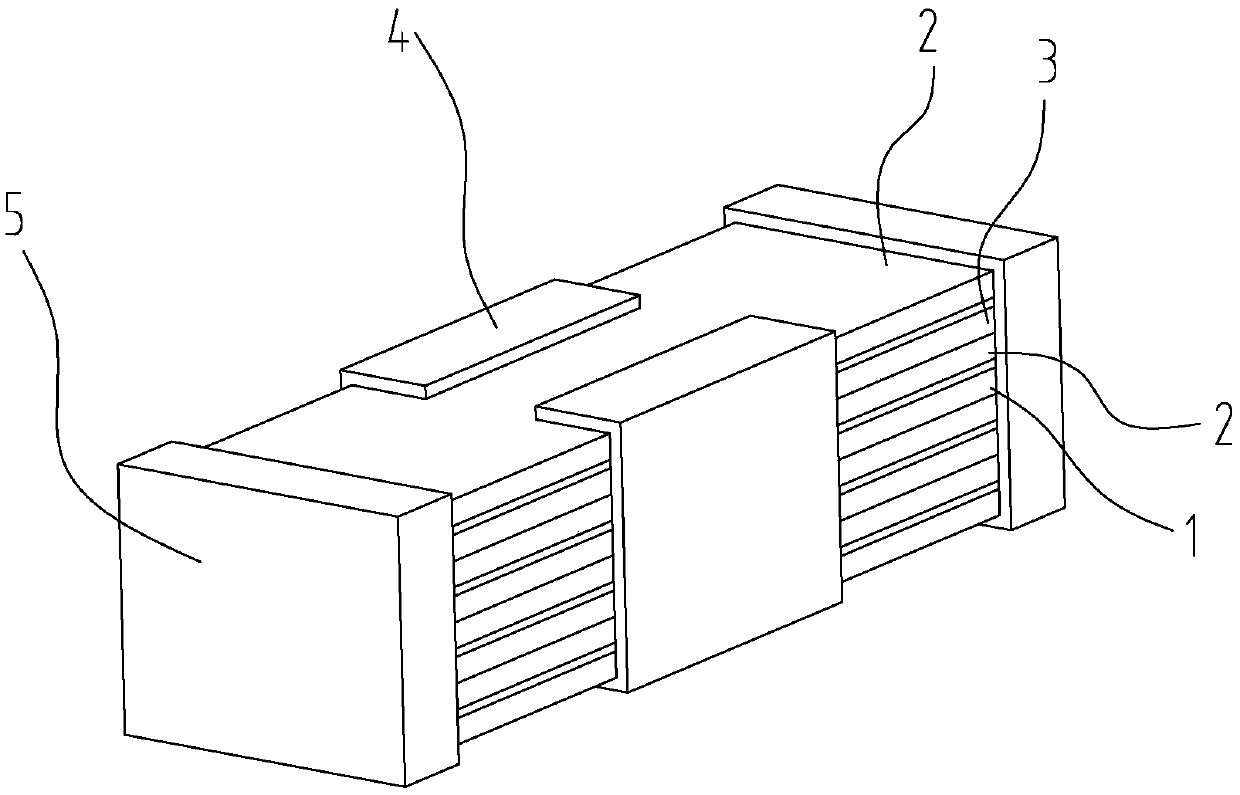

[0023] In order to clearly illustrate the technical characteristics of this solution, the following specific implementation methods are combined with the attached Figure 1 to 6 , To elaborate on the present invention. It should be noted that the components illustrated in the drawings are not necessarily drawn to scale. The present invention omits descriptions of well-known components and well-known technologies to avoid unnecessarily limiting the present invention.

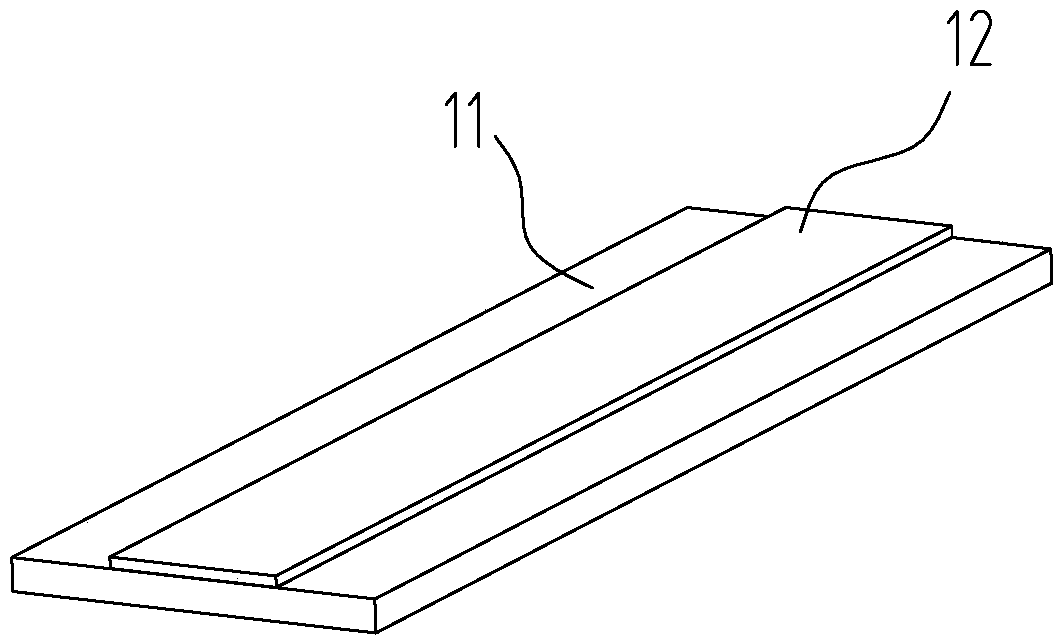

[0024] A ceramic capacitor for reducing parasitic inductance, comprising a first chip 1, a ceramic dielectric sheet 2, a second chip 3, a grounded external electrode plate 4 and a signal external electrode plate 5; the first chip 1 includes a first ceramic substrate 11 and The first internal electrode 12 is provided on the surface of the first ceramic substrate 11, and the first internal electrode 12 extends laterally to the left and right sides of the first ceramic substrate 11. The second chip 3 includes a secon...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More