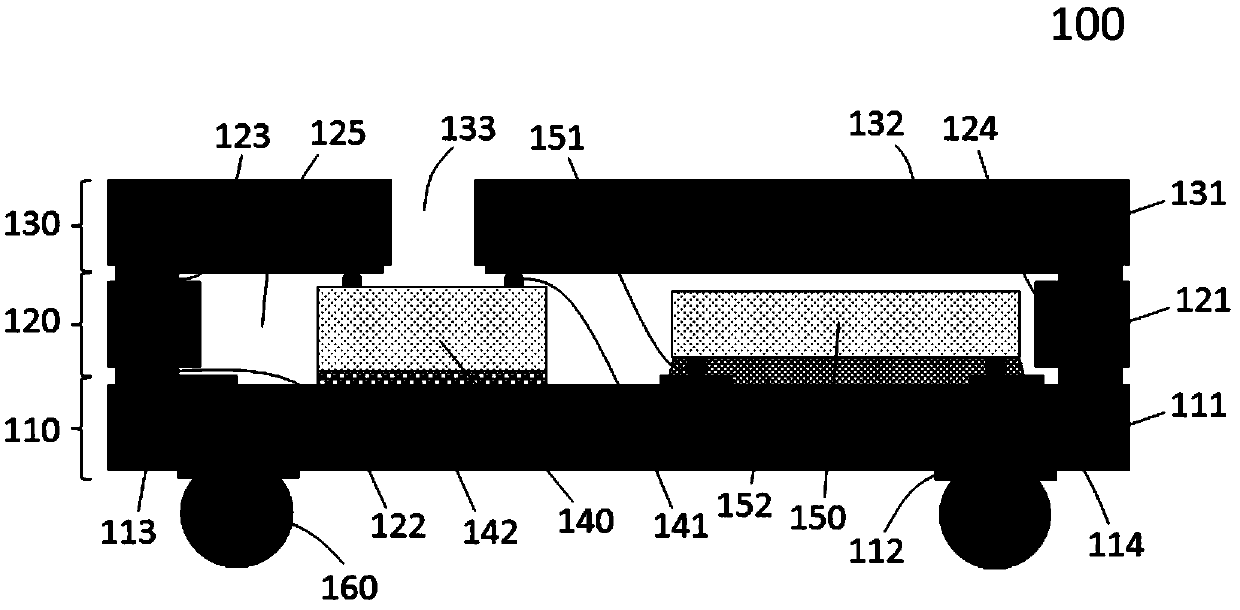

Wafer-level light sensing system-level packaging structure and manufacturing method thereof

A system-level packaging and wafer-level technology, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as high packaging cost, large package size, and inflexible packaging structure design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] In the following description, the present invention is described with reference to various examples. One skilled in the art will recognize, however, that the various embodiments may be practiced without one or more of the specific details, or with other alternative and / or additional methods, materials, or components. In other instances, well-known structures, materials, or operations are not shown or described in detail so as not to obscure aspects of the various embodiments of the invention. Similarly, for purposes of explanation, specific quantities, materials and configurations are set forth in order to provide a thorough understanding of embodiments of the invention. However, the invention may be practiced without these specific details. Furthermore, it should be understood that the various embodiments shown in the drawings are illustrative representations and are not necessarily drawn to scale.

[0053]In this specification, reference to "one embodiment" or "the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More