IDFT-based software phase-locked loop implementation method and device

A technology of software phase-locked loop and implementation method, which is applied in the direction of single-network parallel feeding arrangement, etc., can solve the problems of signal discontinuity, delay signal error, large calculation amount, etc., and achieve easy digital implementation, troubleshooting influence, calculation volume streamlining effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

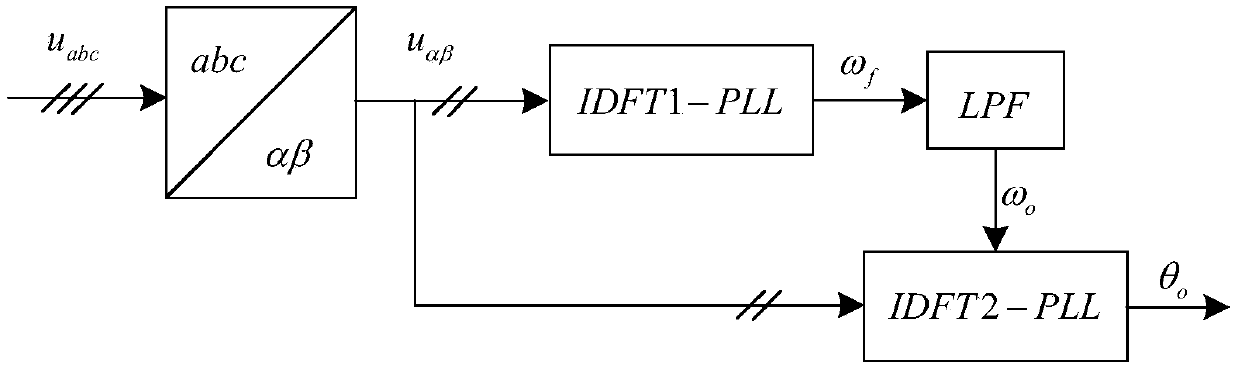

[0105] The implementation method of the software phase-locked loop based on IDFT in this embodiment comprises the following steps:

[0106] Step 1. Combine the attached figure 1 , image 3 , in the nth switching cycle, the voltage signal u a (n), u b (n), u c (n) Convert to the αβ static coordinate system through the clark transformation to get u α (n), u β (n), the conversion formula is as follows:

[0107]

[0108] where u a (n) is the phase A voltage sampling signal of the nth switching cycle, u b (n) is the B-phase voltage sampling signal of the nth switching cycle, u c (n) is the phase C voltage sampling signal of the nth switching cycle.

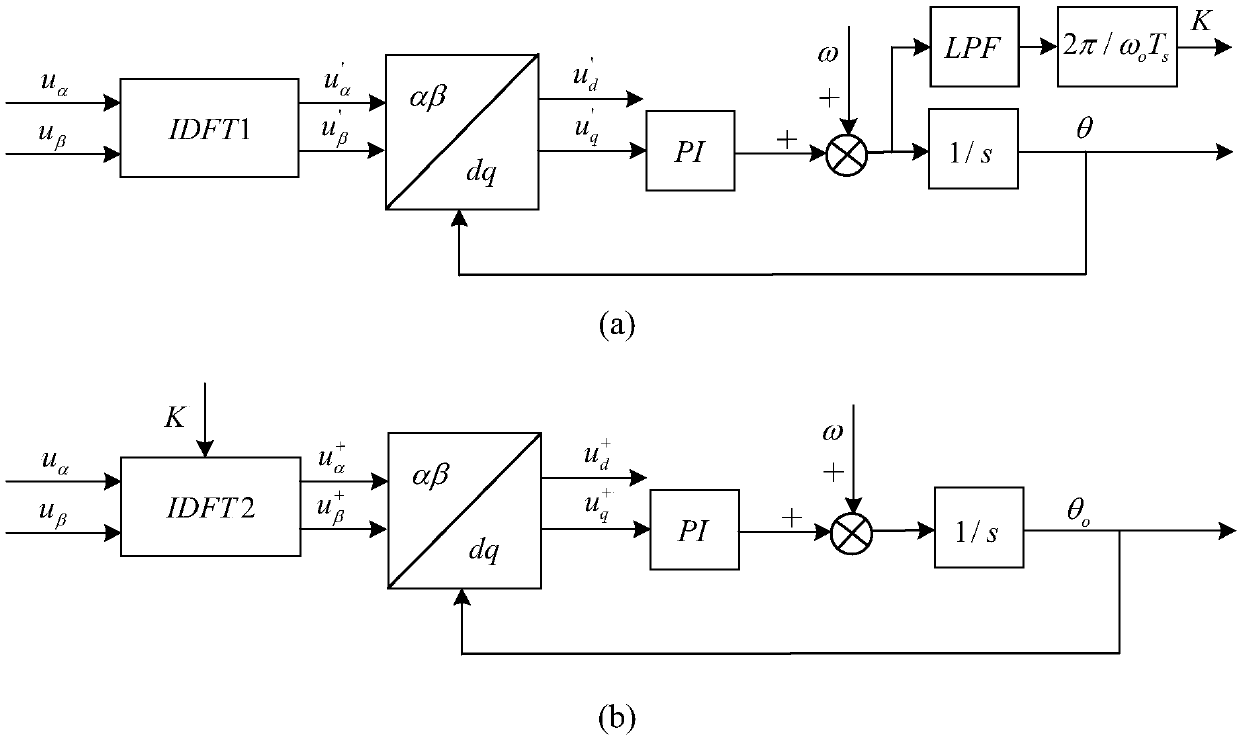

[0109] Step 2, put u α (n), u β (n) Extract the quasi-fundamental positive sequence signal u by Inverse Discrete Fourier Transform 1 (Inverse Discrete FourierTransform 1, IDFT1) α '(n), u β '(n); put u α (n), u β (n) Extract the quasi-fundamental positive sequence signal u through Inverse Discrete Fourier Transform 2 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More