A DRAM output driving circuit and a method for reducing electric leakage thereof

A technology for outputting driving circuits and voltages, applied in the field of DRAM output driving circuits, can solve the problem of large leakage of output stage driving circuits, and achieve the effects of reducing leakage current, reducing leakage current, and reducing leakage current.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

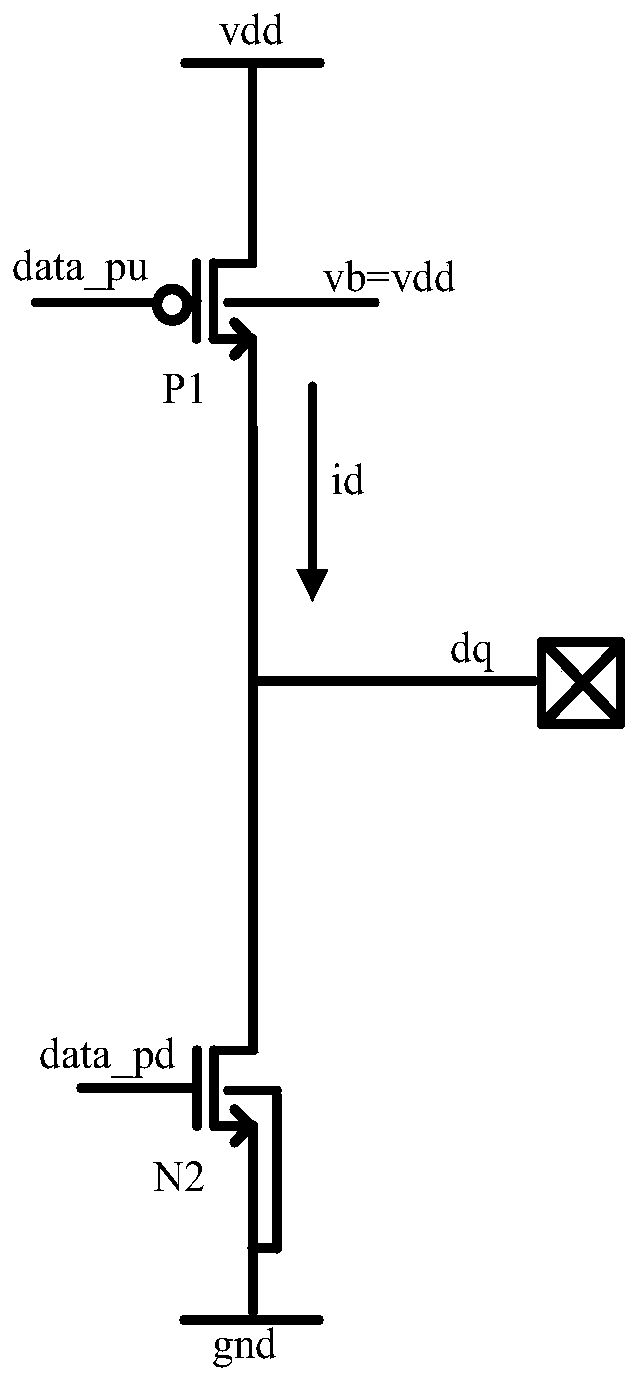

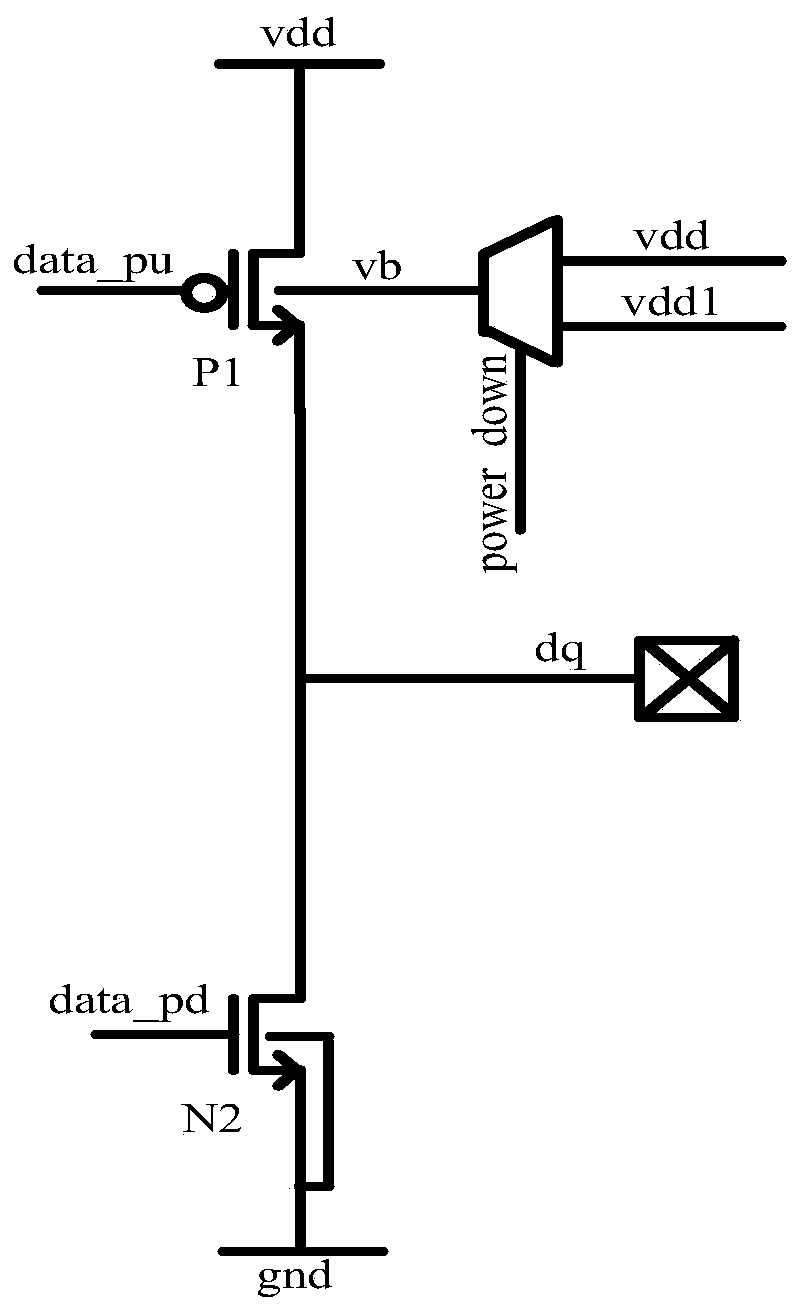

[0023] In this embodiment, when the pull-up transistor of the DRAM output driving circuit is a PMOS.

[0024] The base voltage vb is not directly connected to the working voltage vdd, but is connected to the output of the voltage selector. The input of the voltage selector is the working voltage vdd and the extra working voltage vdd1. Power_down is a voltage selection signal. The extra working voltage vdd1 is a voltage higher than the working voltage vdd.

[0025] Normal working mode: power_down=0, vb=vdd.

[0026] Power saving mode: power_down=1, data_pu=vdd, data_pd=gnd, dq=gnd, vb=vdd1, where vdd1 is a higher voltage than vdd.

[0027] In the power-saving mode, the threshold voltage of the PMOS transistor P1 becomes lower due to the rise of vb, because the leakage current of the PMOS transistor is positively correlated with the threshold voltage, so the leakage current from vdd to dq through P1 becomes smaller. In the normal working mode, vb=vdd, the threshold voltage o...

Embodiment 2

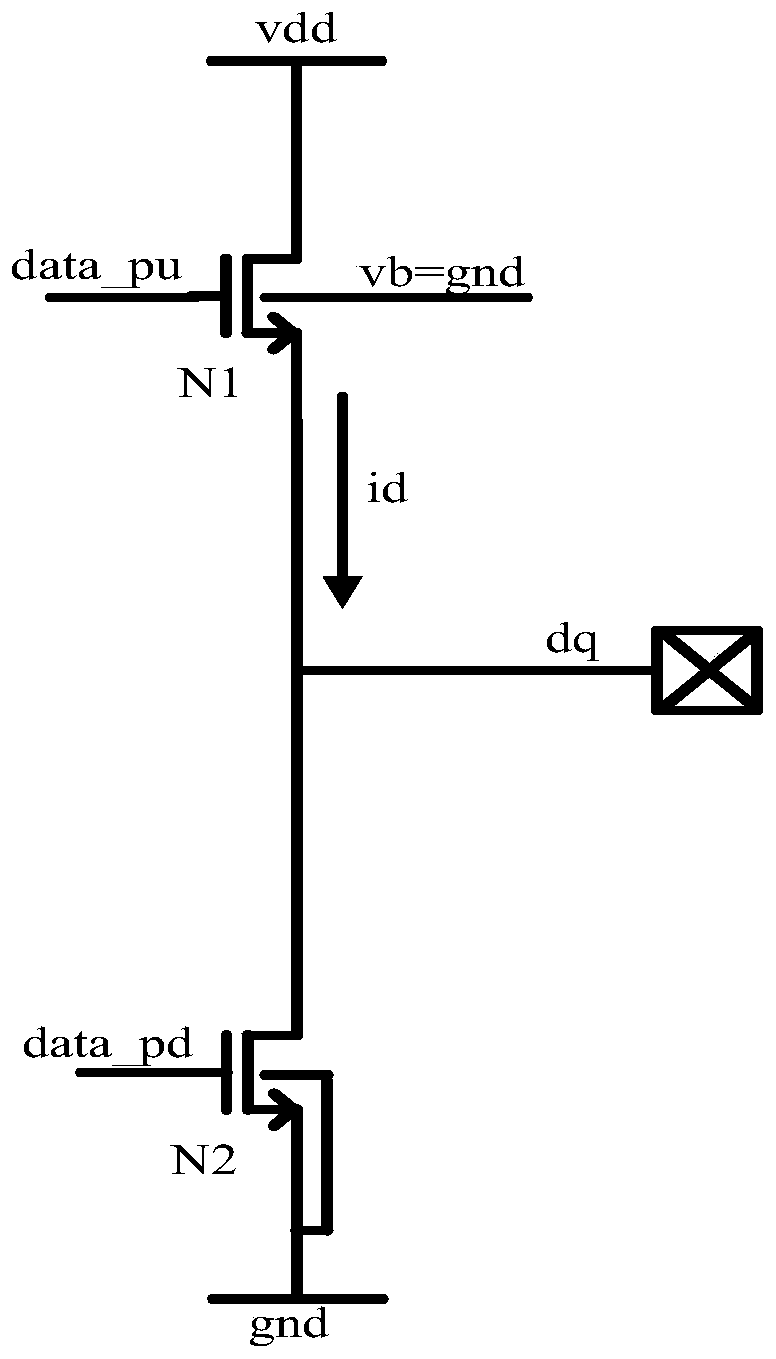

[0029] In this embodiment, the pull-up transistor of the DRAM output driving circuit is NMOS.

[0030] The base voltage vb is not directly connected to the ground voltage gnd, but is connected to the output of the voltage selector. The input of the voltage selector is the ground voltage gnd and the extra ground voltage v_neg. Power_down is a voltage selection signal. Wherein the additional ground voltage v_neg is a voltage lower than the ground voltage gnd.

[0031] Normal working mode: power_down=0, vb=gnd.

[0032] Power saving mode: power_down=1, data_pu=gnd, data_pd=gnd, dq=gnd, vb=v_neg, v_neg is a lower voltage than gnd.

[0033] In the power-saving mode, the threshold voltage of the NMOS transistor N1 increases due to the drop of vb, because the leakage current of the NMOS transistor is negatively correlated with the threshold voltage, so the leakage current from vdd to dq through N1 becomes smaller . In the normal working mode, vb=gnd, the threshold voltage of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More