Fan-out type packaging structure and packaging method of chip

A technology of packaging structure and packaging method, which is applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve the problems affecting the warpage of the package body, and achieve the effect of reducing package deformation warpage and controlling product warpage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The technical solutions of the present invention will be clearly and completely described below in conjunction with the accompanying drawings. Apparently, the described embodiments are some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0022] In addition, the technical features involved in the different embodiments of the present invention described below may be combined with each other as long as there is no conflict with each other.

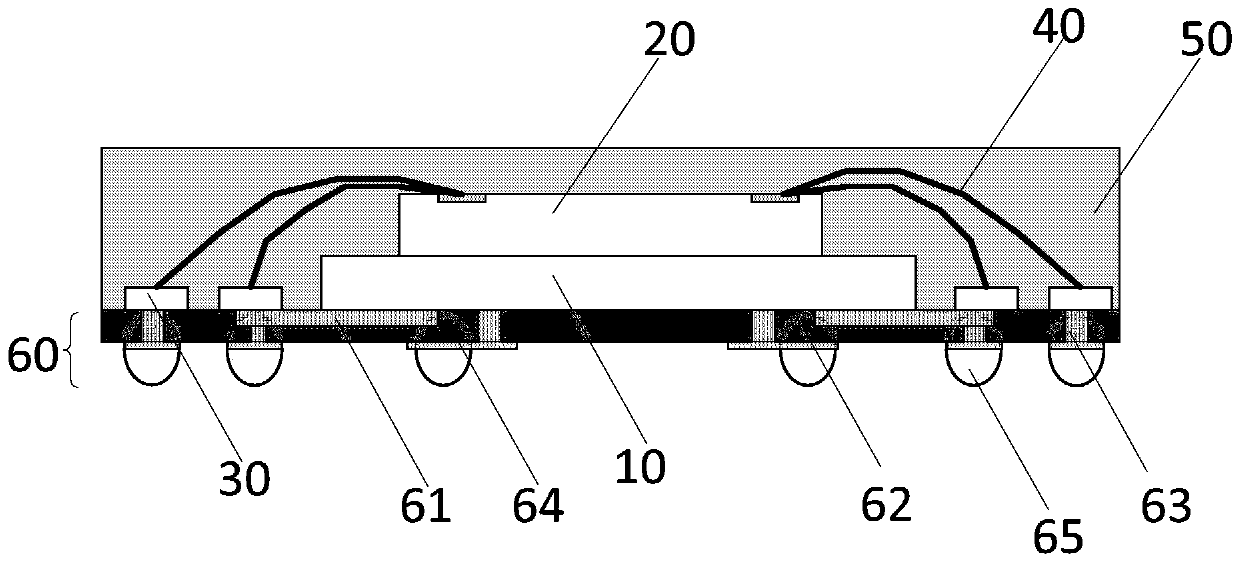

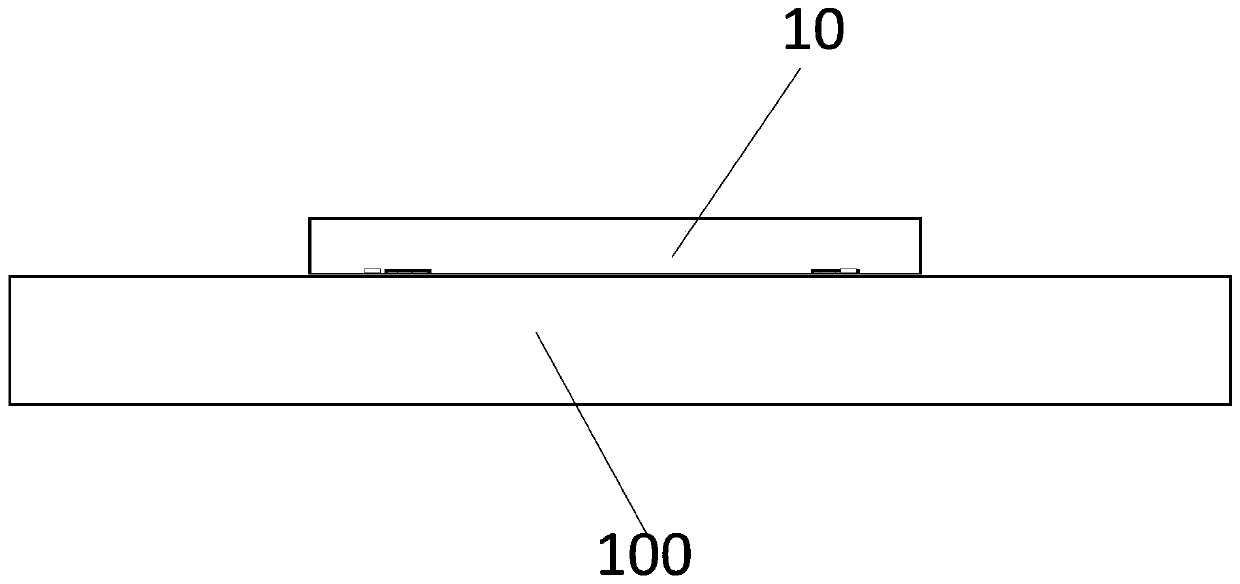

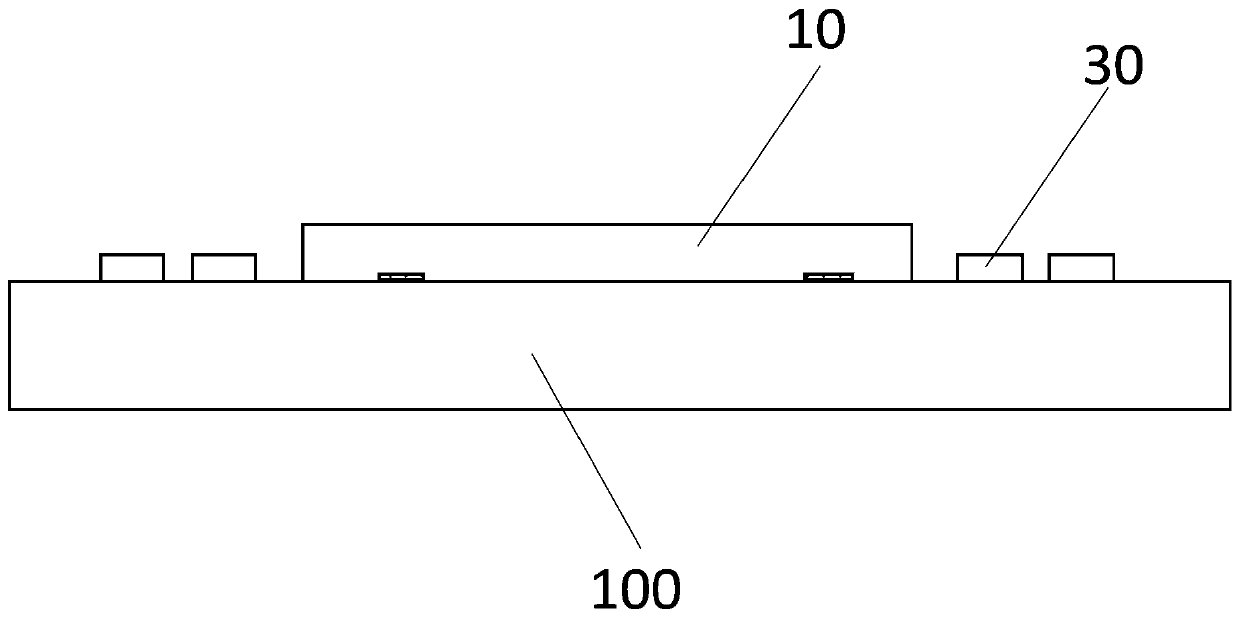

[0023] An embodiment of the present invention provides a chip fan-out packaging structure, such as figure 1 As shown, the structure includes: a first chip 10 and a second chip 20 whose bottom surfaces are relatively bonded; a plurality of metal terminals 30 are distributed around the first chip 10, and one si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More