A kind of erasing enhanced nord flash memory and preparation method thereof

A NORD, enhanced technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of deterioration of erasing performance, reduction of electric field strength, etc., to achieve improved erasing performance, enhanced electric field strength, and productivity Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

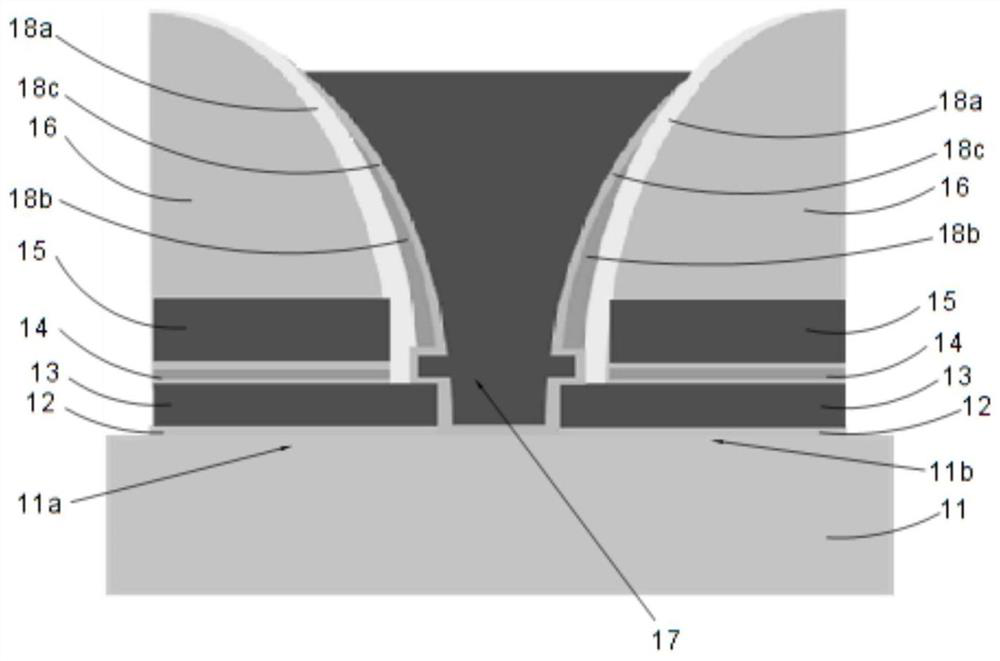

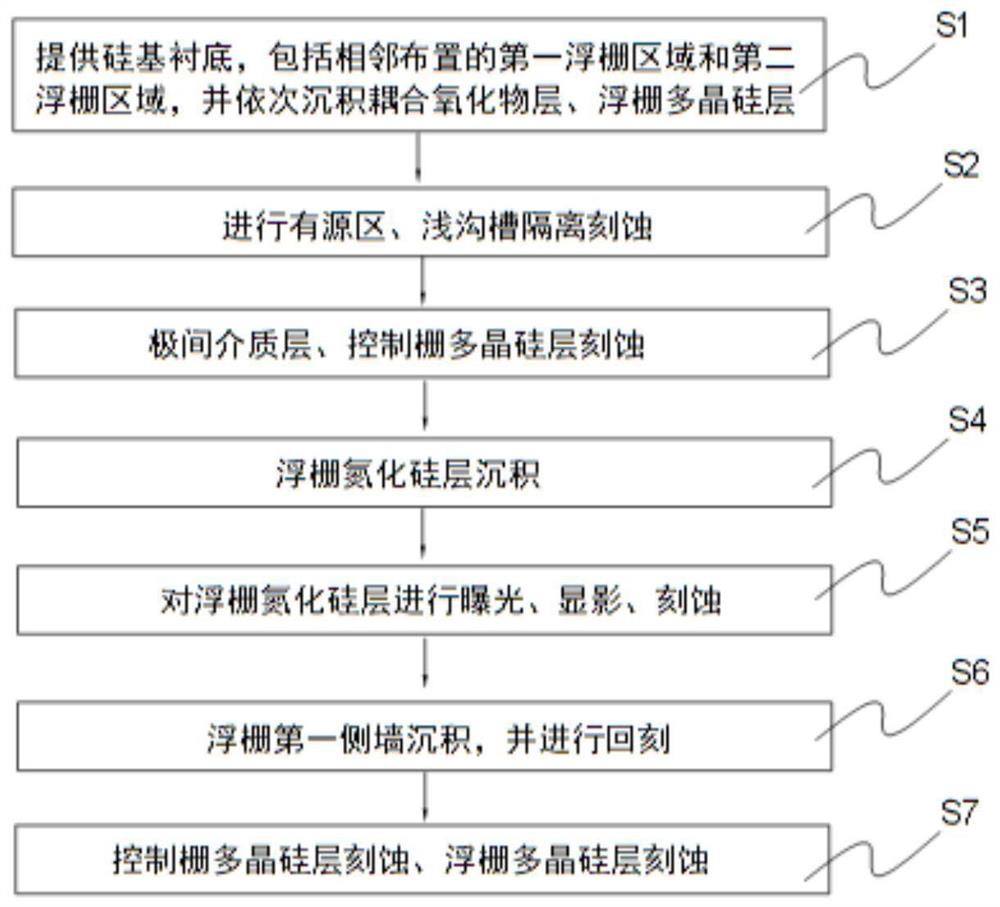

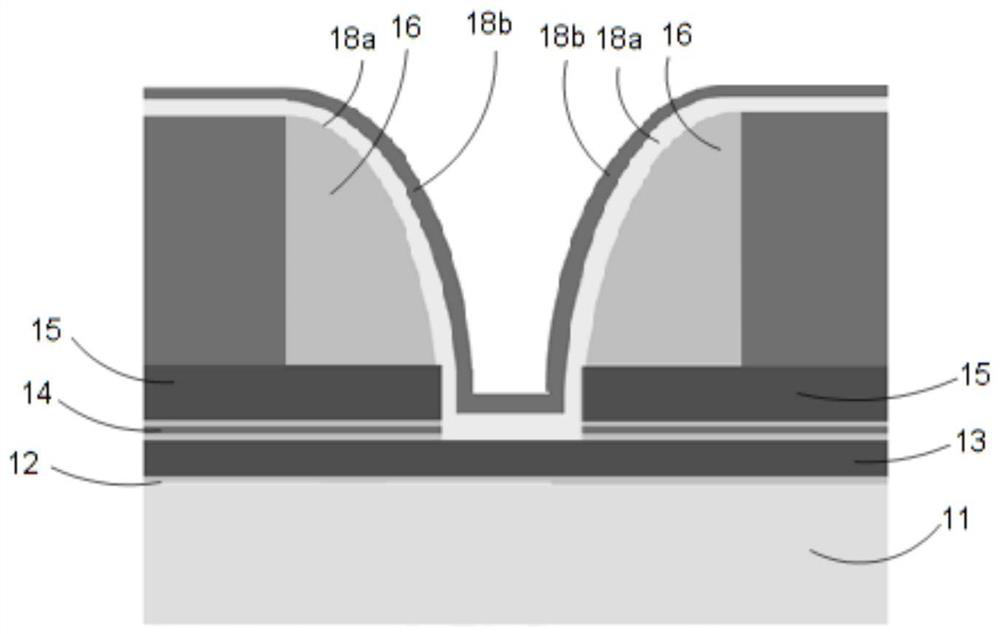

[0036] In order to illustrate the technical content, structural features, achieved goals and effects of the present invention in detail, the following will be described in detail in conjunction with the embodiments and accompanying drawings.

[0037] Due to its advantages of high density, low price, and electrical programmability and erasability, flash memory has been widely used as the best choice for non-volatile memory applications. Generally speaking, floating-gate flash memories have similar original cell structures, and they all have a stacked gate structure, which includes a floating gate and a control gate covering at least the floating gate. Wherein, the control gate is coupled to control storage and release of electrons in the floating gate.

[0038] Nord flash memory erasing occurs through Fowler Nordheim (FN) tunneling between the floating gate (Floating Gate, FG) and the word line (Word Line, WL), through the tunneling between the word line and the control gate ( ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More