An FPGA verification method of a JESD204B controller

1. JESD204B, verification method technology, applied in hardware monitoring, etc., can solve the problems of no hardware verification system and verification method, less verification technology, and inability to verify FPGA board level

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0070] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

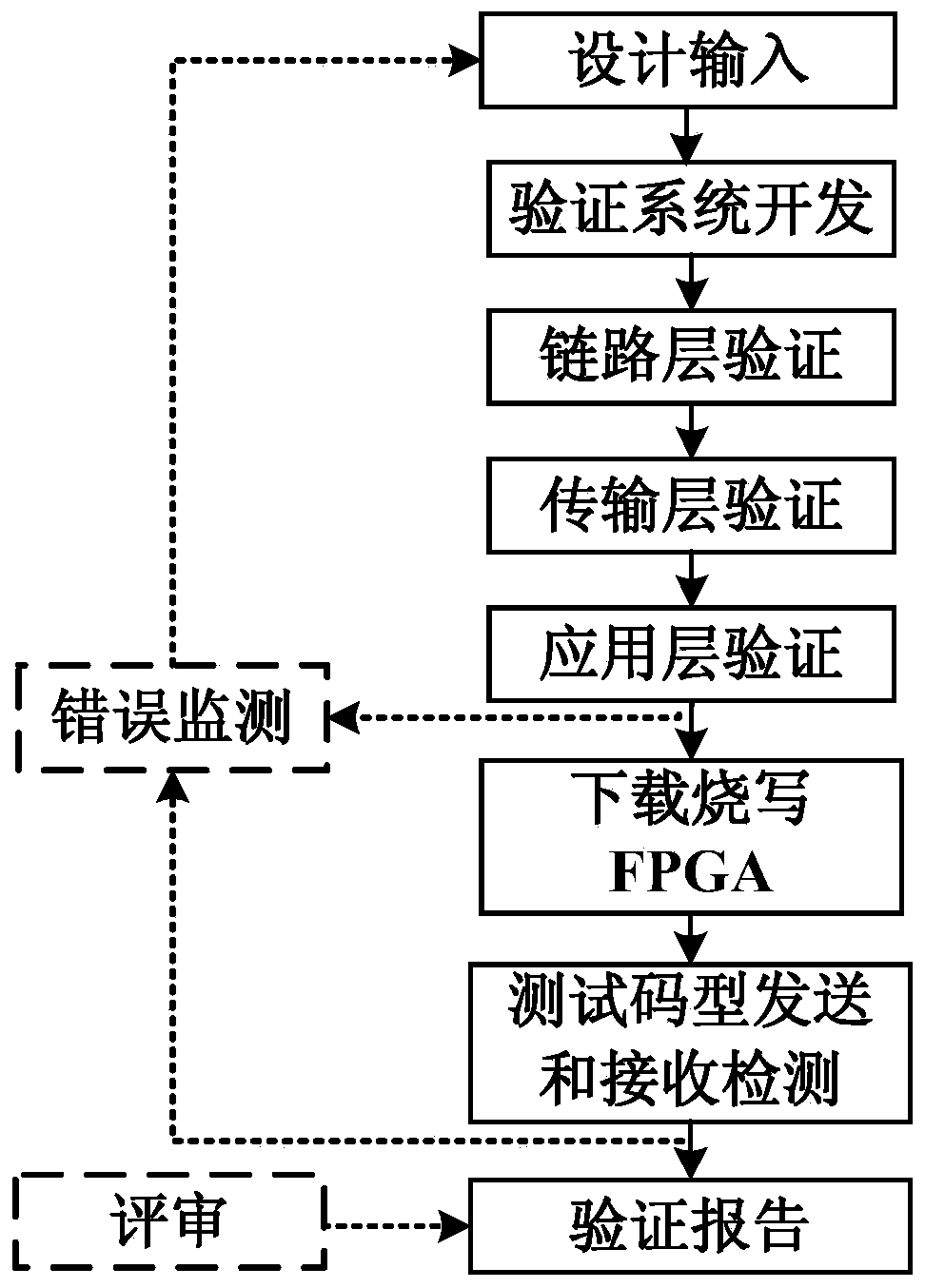

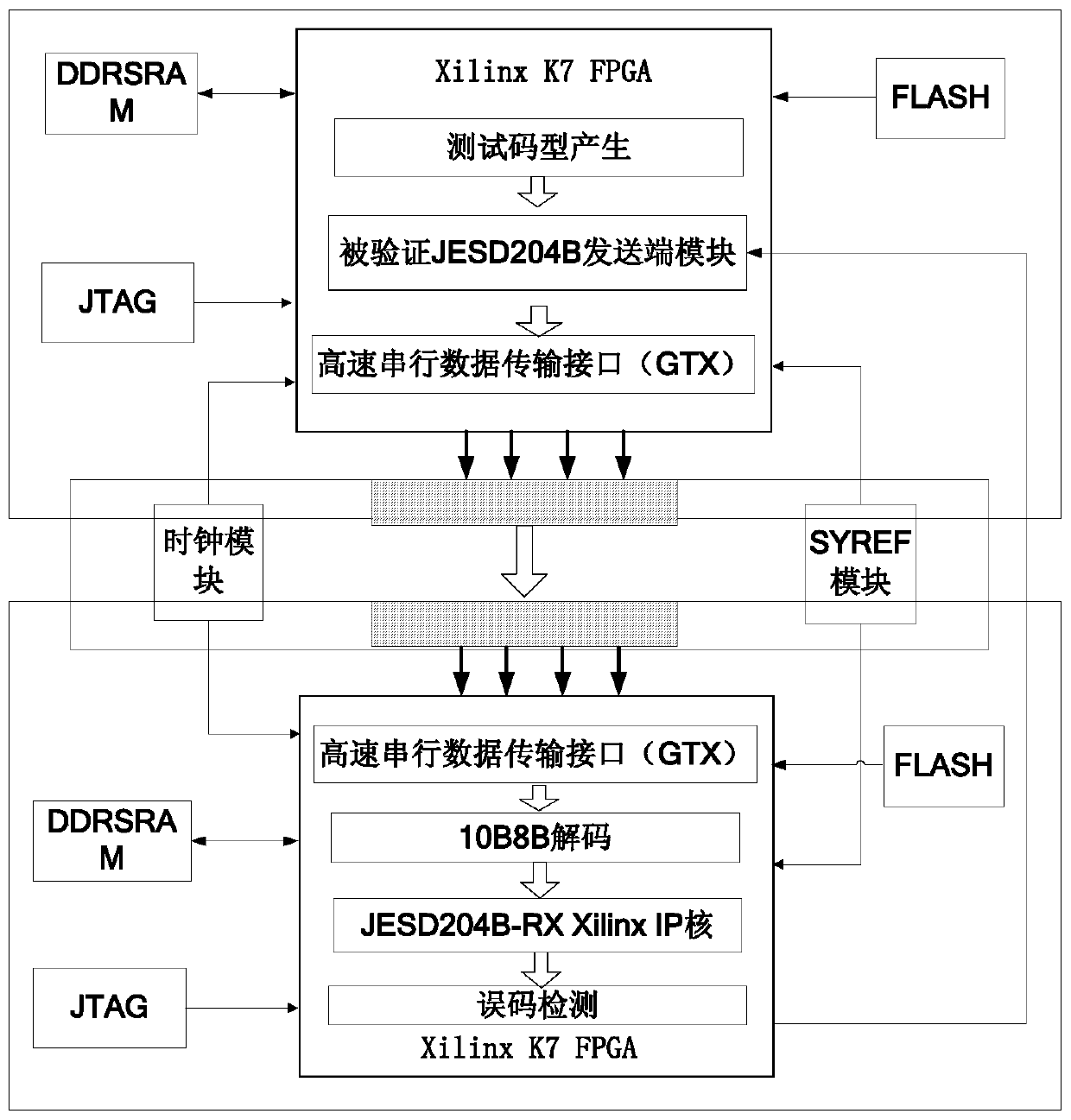

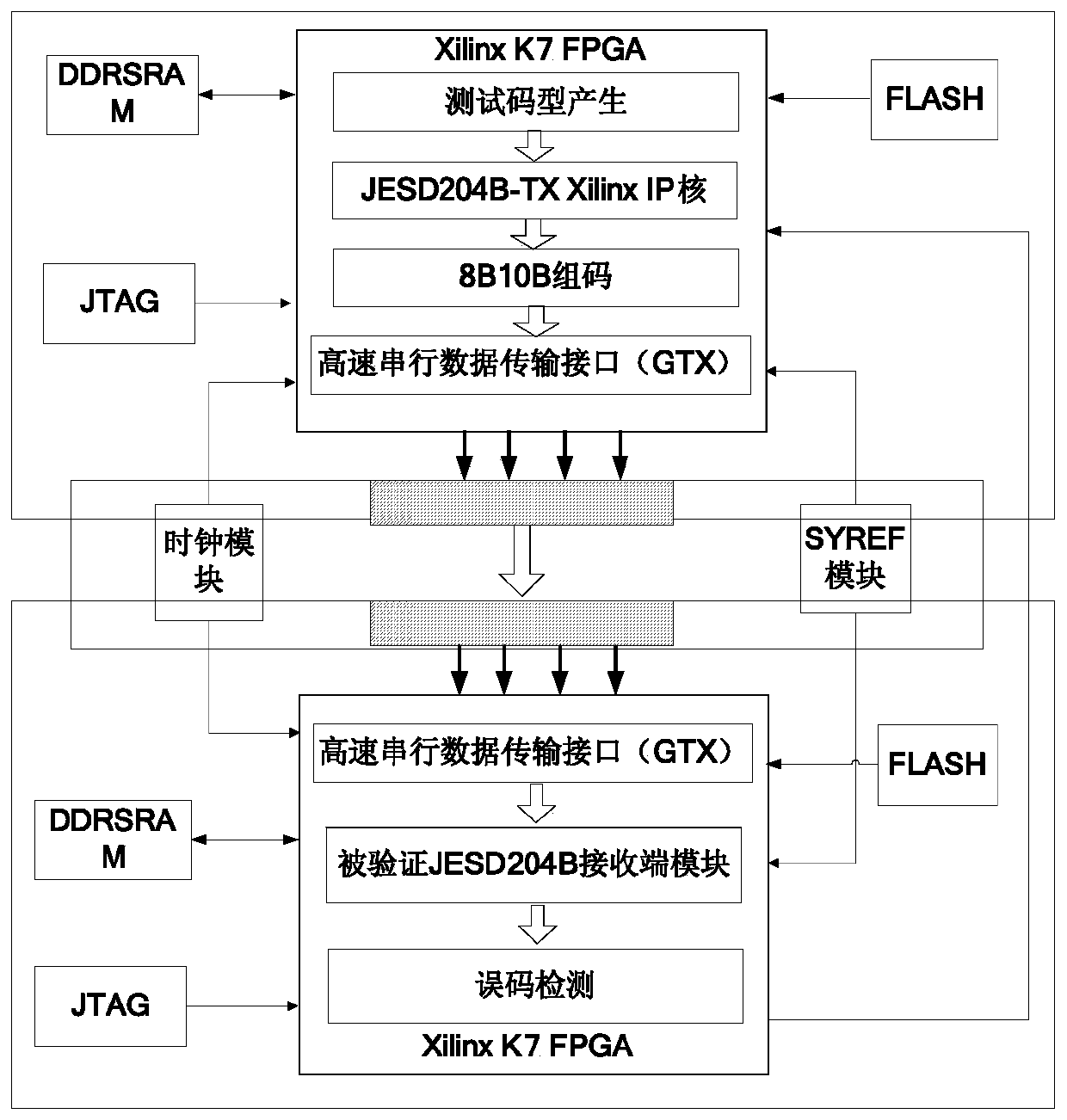

[0071] The JESD204B controller is composed of digital logic that meets the requirements of the JESD204B protocol. The accuracy and completeness of the design of the digital code part of the protocol needs to be verified by FPGA. The verification conditions are related to the accuracy, comprehensiveness and credibility of the verification results, and need to be carefully selected. Among them, there are generally two verification methods based on FPGA, tool simulation verification and actual debugging of board-level systems. The tool simulation verification is easy to operate. With the help of the components of the development tool and the internal model simulation test analysis, it is possible to obtain whether the timing relationship of the signal in the design, the logic function of the controller, and the timing of the controller meet the requireme...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap