A configurable floating point vector multiplication ip core based on fpga

A vector multiplication and multiplication technology, which is applied in the field of configurable floating-point vector multiplication IP cores, can solve problems such as the inability to customize the operation accuracy, the failure to take advantage of the FPGA hardware reconfigurability, and the inability to configure the number of operators, so as to improve resource utilization. efficiency and computing efficiency, realize FPGA parallel computing acceleration, and improve the effect of hardware resource utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] Exemplary embodiments of the present disclosure will be described in more detail below with reference to the accompanying drawings. Although exemplary embodiments of the present disclosure are shown in the drawings, it should be understood that the present disclosure may be embodied in various forms and should not be limited by the embodiments set forth herein. Rather, these embodiments are provided for more thorough understanding of the present disclosure and to fully convey the scope of the present disclosure to those skilled in the art.

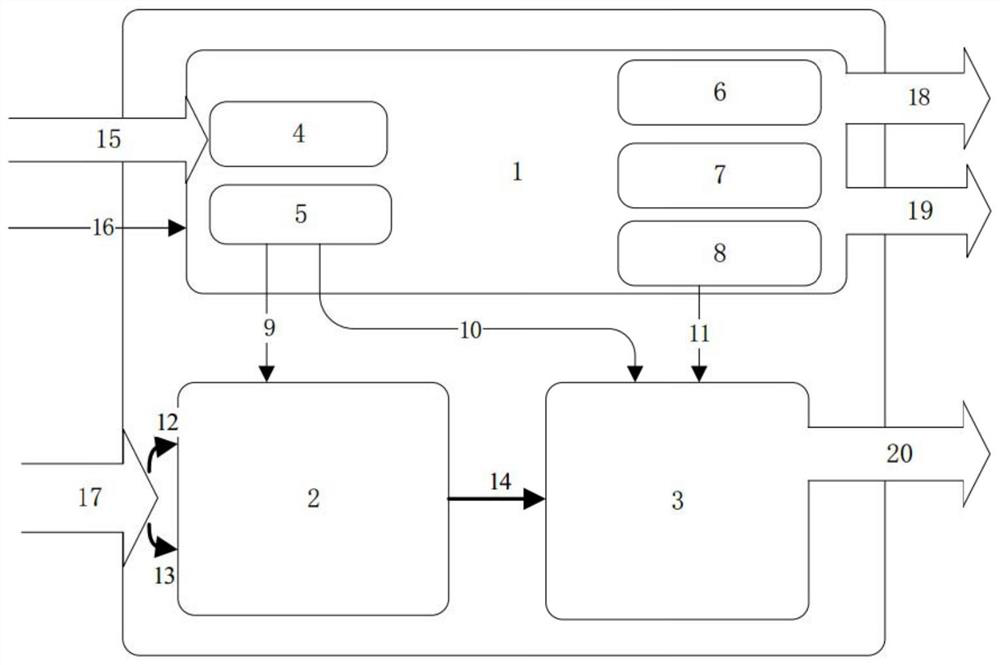

[0055] refer to figure 1 As shown, the embodiment of the present invention provides a FPGA-based configurable floating-point vector multiplication IP core, including: an operation controller 1, a multiplication array module 2 and an addition array module 3;

[0056] Among them, the operation controller 1 is used to receive the instruction signal 15 and obtain the input clock 16, and output the RAM control signal 18 and the status w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More