A nand Flash Bit Error Rate Prediction Method Based on Support Vector Regression

A technology of support vector regression and prediction method, which is applied to error detection of redundant codes, generation of response errors, instruments, etc. It can solve the problems of reduced storage reliability, reduced structure size, and smaller interval, and achieves fewer entry parameters. , The effect of short prediction time and high work efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

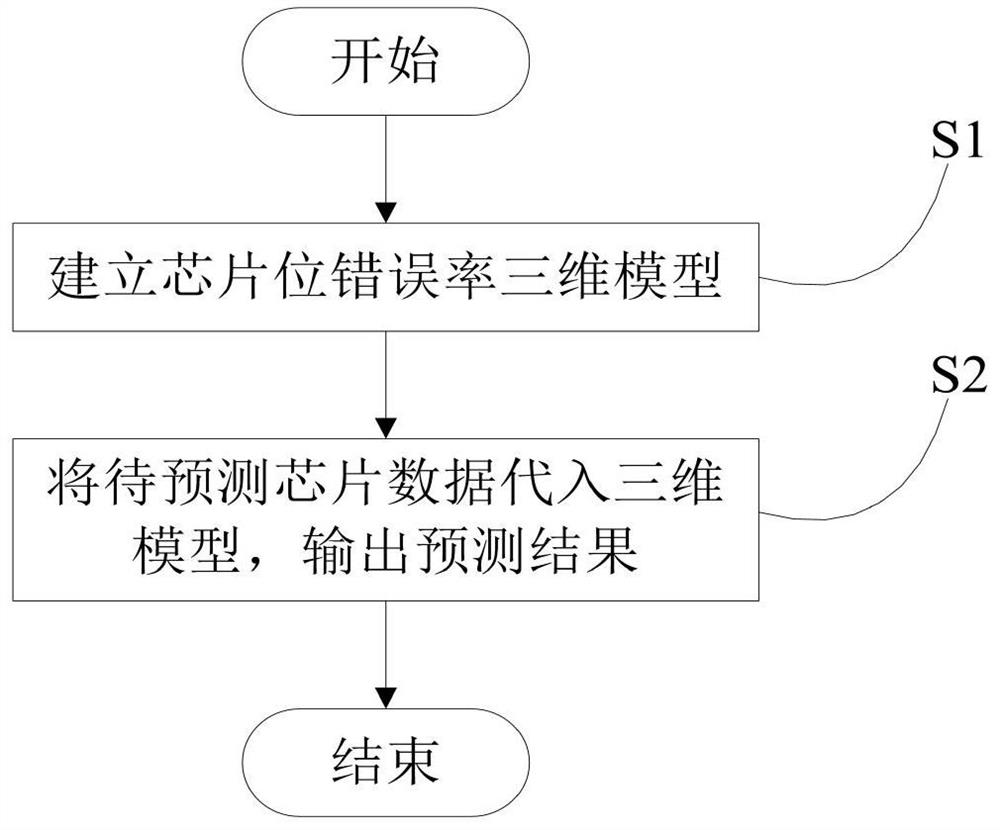

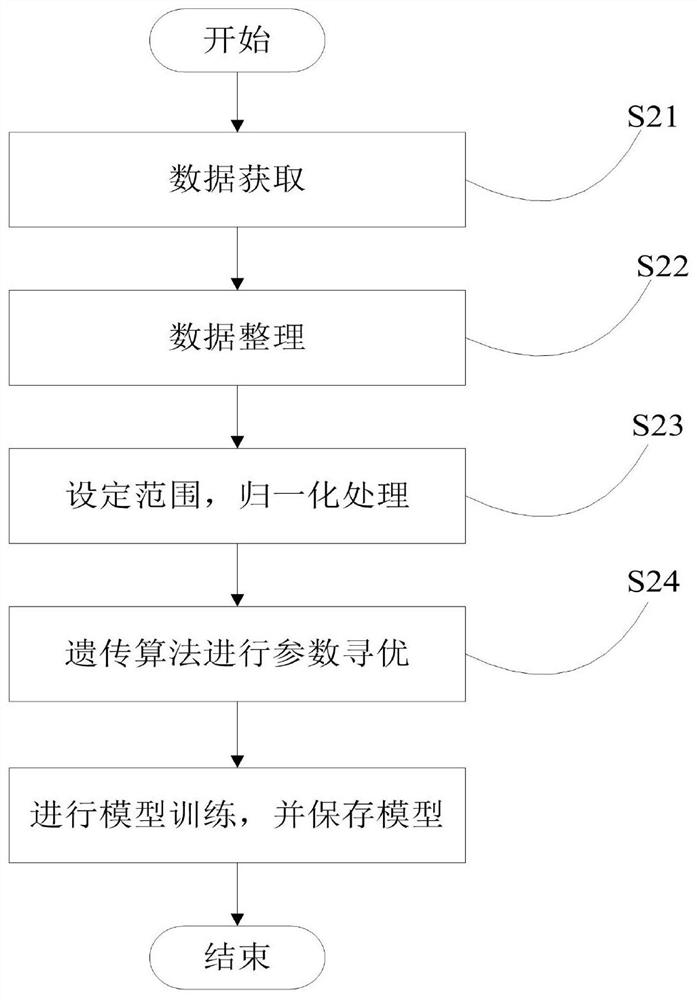

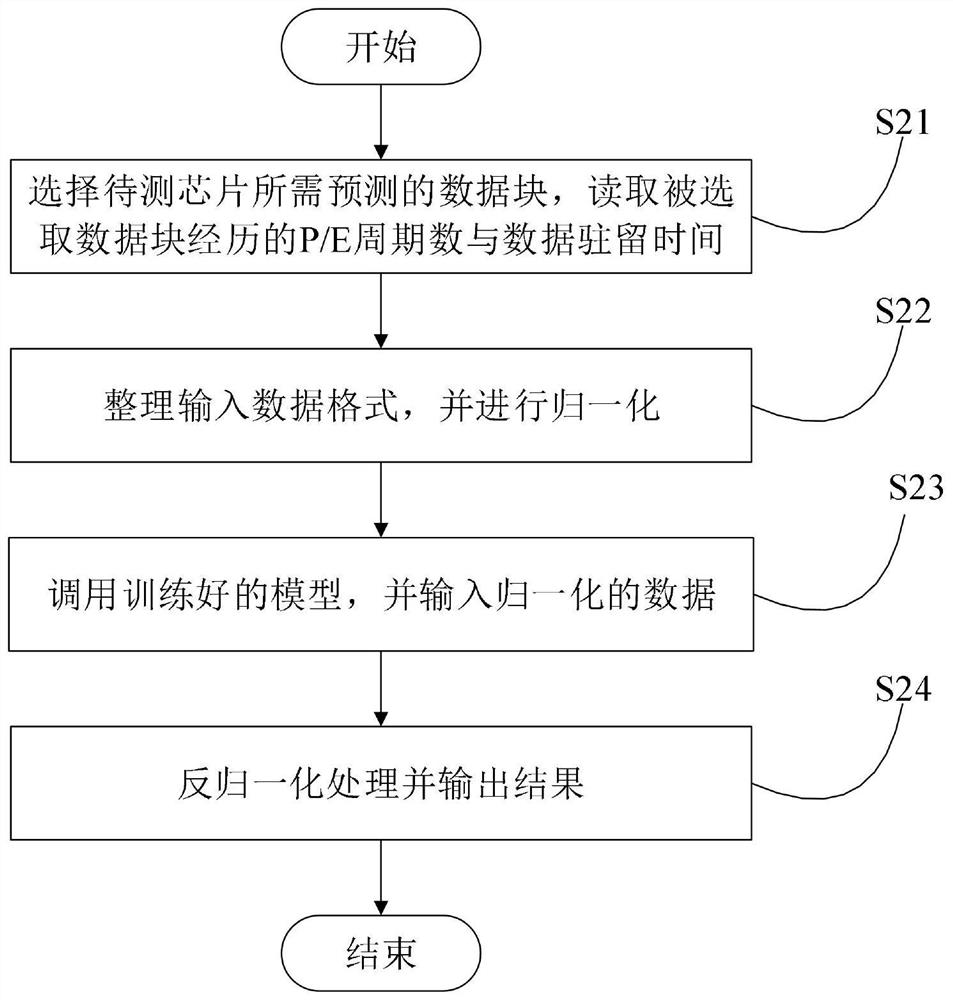

Method used

Image

Examples

Embodiment 1

[0074] An MLC NAND Flash chip with a page width of 4096 bytes from Micron was used as an experiment to predict the bit error rate. First, the random number generation function was used to generate a size of 4k bytes '0', and the ratio of '1' was 1: The data of 1 is written into different data pages of the NAND Flash chip respectively, and then 66 different physical blocks in the chip are selected, and each physical block corresponds to a fixed P / E cycle for uninterrupted programming / erasing cycles (P / E E) cycle, the selection rule of the P / E cycle number collection data in the present embodiment is, the wear strength of interval 100P / E cycle, from 1P / E cycle to 5000P / E cycle collects 51 groups of data altogether, with 1000P / E cycle The interval, from 5000P / E cycle to 20000P / E cycle, collects 15 sets of data in total. According to this collection rule, bit error rate data with different dwell times were continuously collected for a total of 200 days. According to the collected ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More