Convolution operation based on analog matrix operation unit and application thereof

A matrix operation and convolution operation technology, applied in the field of convolution operation, can solve the problems of consuming operation time and power consumption, computing unit and memory resource consumption, etc., to achieve area reduction, high computing parallelism, practicability and applicability strong effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0091] like figure 1 As shown, it is a single analog multiplication circuit that constitutes an analog matrix operation unit in this embodiment, including a pair of floating gate field effect transistors M 1 , M 2 and a differential current sense circuit;

[0092] where M 1 and M 2The common gate is connected to the voltage source, and the common drain or common source is connected to the analog voltage input. The differential current detection circuit includes two current input terminals and one output terminal, and the two current input terminals are correspondingly connected to M 1 and M 2 respective source or drain; it is stated here that if M 1 and M 2 The common drain is connected to the analog voltage input, and the two current input terminals are correspondingly connected to M 1 and M 2 respective sources, if M 1 and M 2 The common source is connected to the analog voltage input, and the two current input terminals are correspondingly connected to M 1 and M ...

Embodiment 2

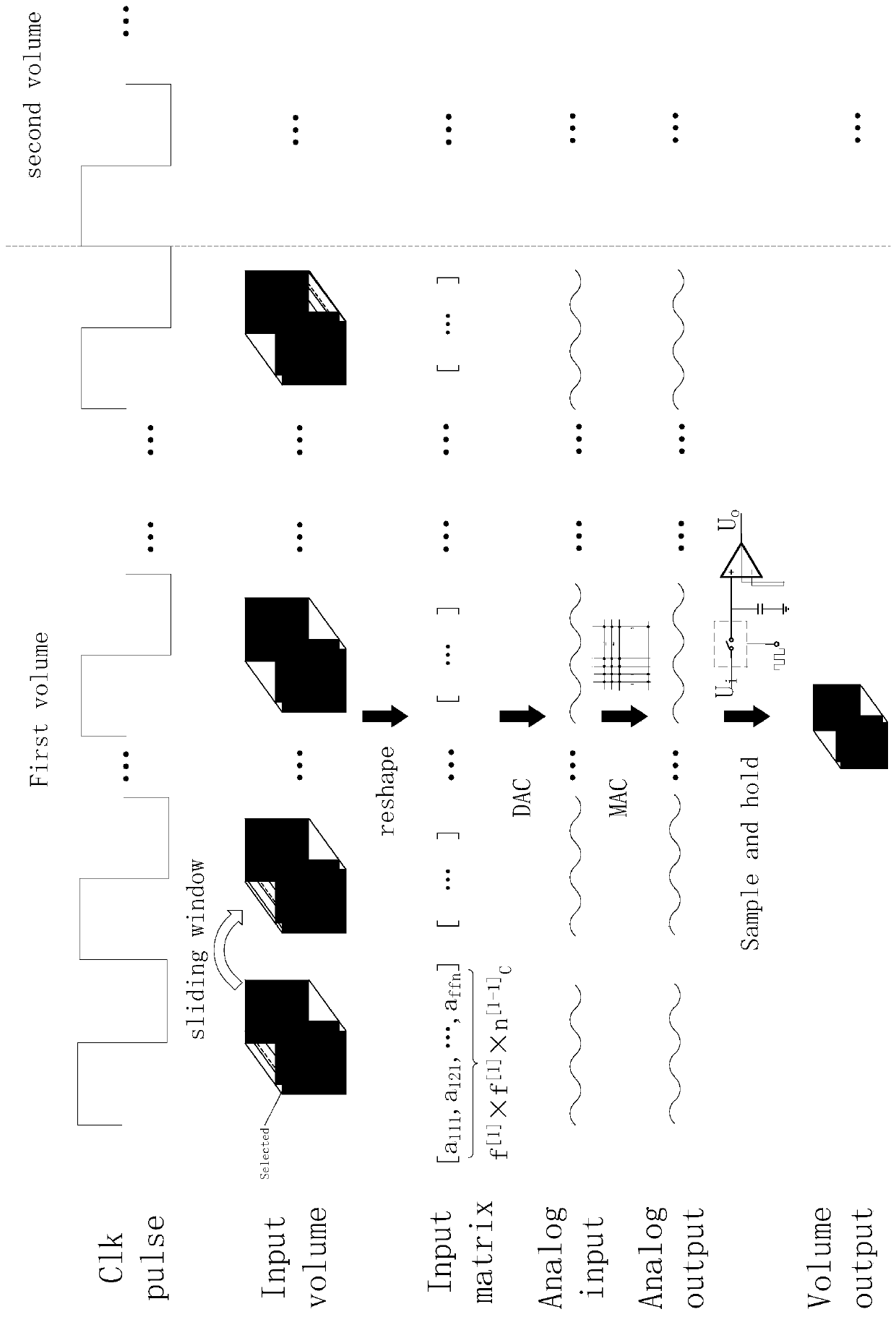

[0131] refer to Figure 12 , is a schematic diagram of a 2D convolution operation based on an analog matrix operation unit in this embodiment: the dimension of the input feature map is 5×5, the dimension of the output feature map is 3×3, and the dimension of the convolution kernel is 3×3 , without considering the bias bias.

[0132] Figure 13 It is the schematic diagram of the 2D convolution realized by the analog matrix operation unit; the convolution kernel with a size of 3×3 is converted into a horizontal quantity [w 11 ,w 12 ,w 13 ,w 21 ,w 22 ,w 23 ,w 31 ,w 32 ,w 33 ] to map it to a row of the analog matrix operation unit; convert the input feature map into 9 horizontal quantities according to the sliding window, namely [a 11 ,a 12 ,a 13 ,a 21 ,a 22 ,a 23 ,a 31 ,a 32 ,a 33 ], [a 12 ,a 13 ,a 14 ,a 22 ,a 23 ,a 24 ,a 32 ,a 33 ,a 34 ], ..., [a 33 ,a 34 ,a 35 ,a 43 ,a 44 ,a 45 ,a 53 ,a 54 ,a 55 ], convert it into an analog voltage, and then ...

Embodiment 3

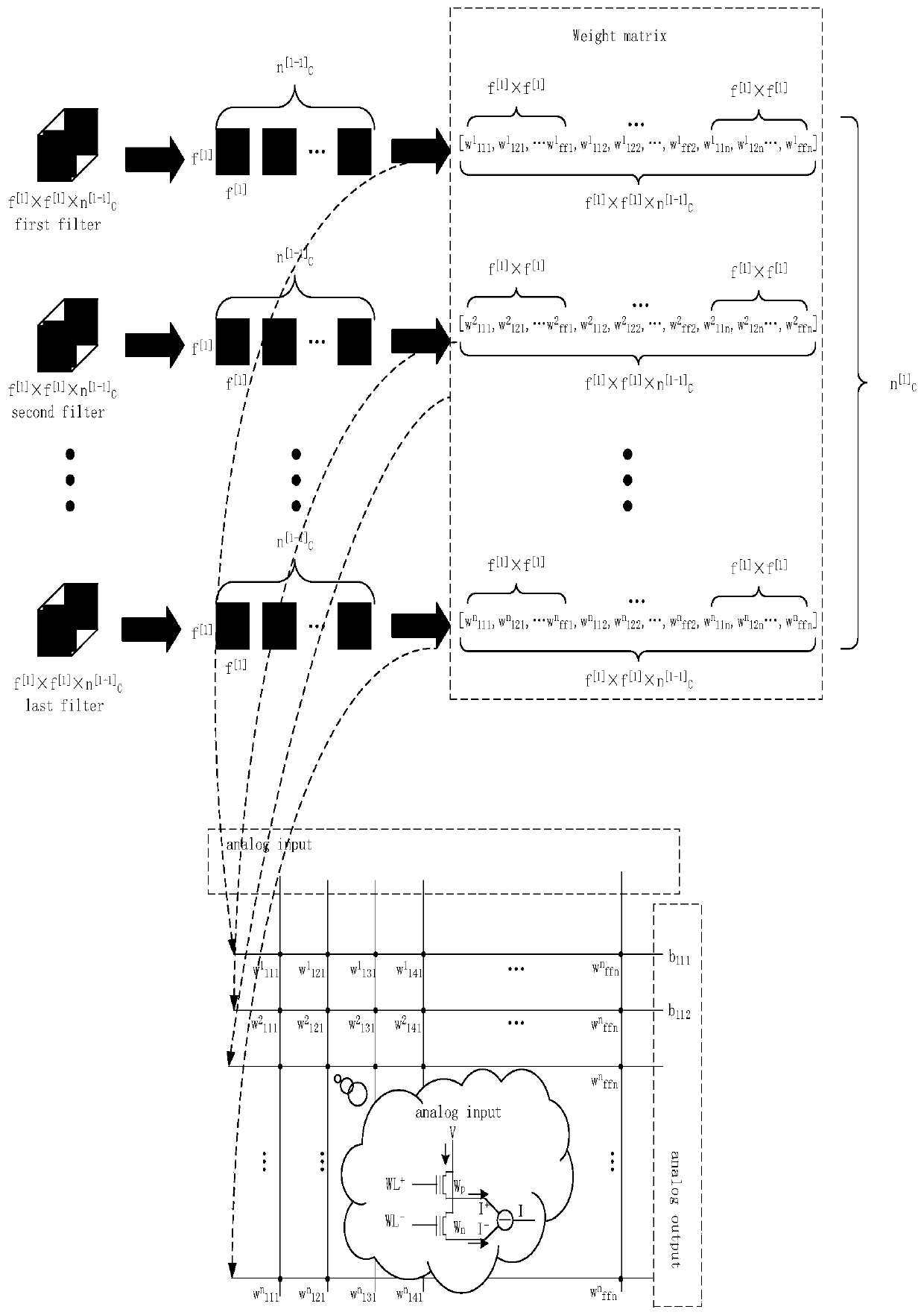

[0134] refer to Figure 14 , which is a schematic diagram of implementing a specific 3D convolution operation based on the analog matrix operation unit in this embodiment:

[0135] The dimension of the input feature map is 3×3×3, and the dimension of the output feature map is 3×3×2. Two 1×1×3 convolution kernels and two 1×1×1 biases are used.

[0136] refer to Figure 15 , is the schematic diagram of the 3D convolution realized by the analog matrix operation unit, which converts two convolution kernels with a size of 1×1×3 and two biases of 1×1×3 into two horizontal quantities [w 11 ,w 12 ,w 13 ,b 1 ], [w 21 ,w 22 ,w 23 ,b 2 ], map it to the two lines of the analog matrix operation unit; convert the input feature map into 9 horizontal quantities according to the sliding window, namely [a 111 ,a 112 ,a 113 ,1], [a 121 ,a 122 ,a 123 ,1],...,[a 331 ,a 332 ,a 333 ,1]. It is converted into an analog voltage, and then input in parallel sequence from the analog inpu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More