Semiconductor device and forming method and working method thereof

A semiconductor and device technology, applied in the field of semiconductor devices and their formation, can solve problems such as performance to be improved, and achieve the effects of reducing the probability of particles, improving the yield, and reducing the probability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] As mentioned in the background, semiconductor devices formed in the prior art have poor performance.

[0029] In order to make the above objects, features and beneficial effects of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

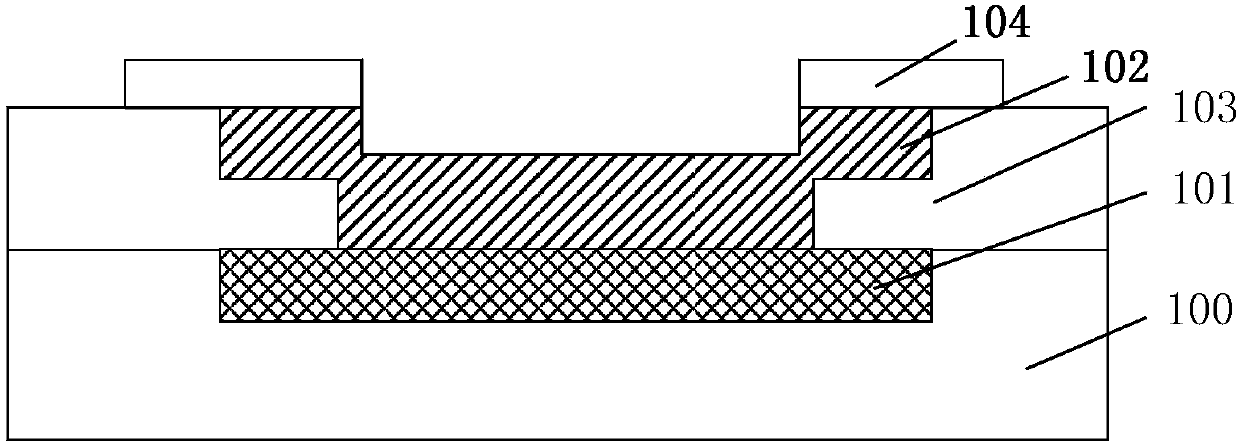

[0030] A semiconductor device, please refer to figure 1 , including: a semiconductor substrate 100; a device body (not shown) and pads located in the semiconductor substrate 100, the pads include a bottom pad layer 101, and a top pad layer 102, the bottom pad layer 101 and the top pad layer 102 The device body is electrically connected, and the top surface of the bottom pad layer 101 is flush with the top surface of the semiconductor substrate 100; the cover layer 103 on the bottom pad layer 101 has a top pad layer 102 in the cover layer, and the top pad layer 102 is located The surface of the bottom liner layer 101 ; the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More