Hundred-nanosecond-level trapezoidal wave pulse forming network and design method

A design method and trapezoidal wave technology, applied in pulse shaping, electric pulse generator circuit, calculation, etc., can solve the problems of large heat generation, large damage rate and low life of ceramic capacitors, achieve simple structure, prolong working life, High matching effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

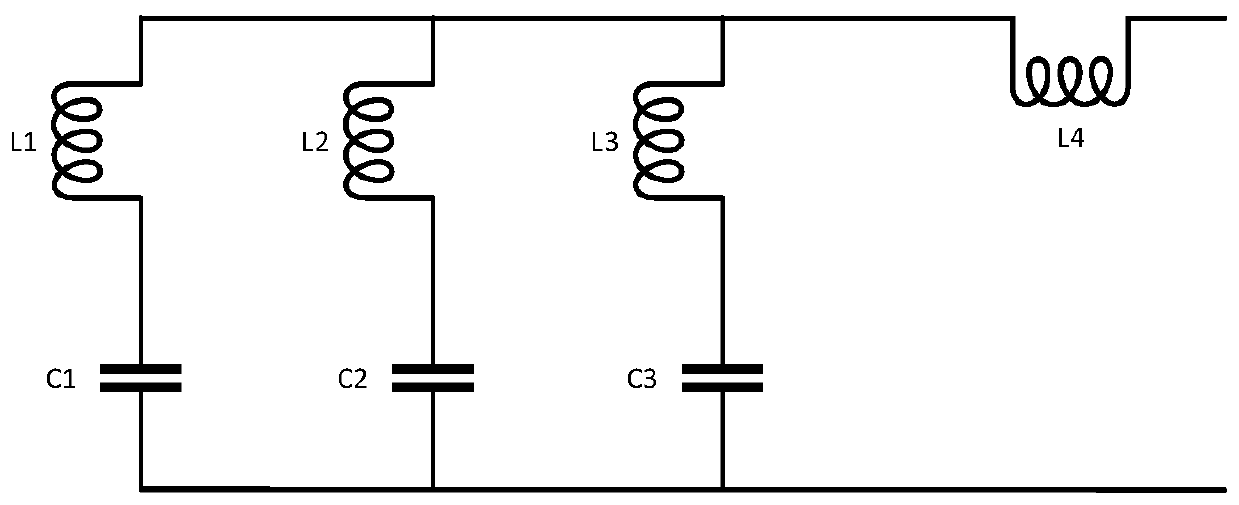

[0049] This embodiment discloses a trapezoidal wave pulse forming network of hundreds of nanoseconds, which includes no more than three LC series branches, wherein the inductance and capacitance of each LC series branch are represented as Ln and Cn respectively, and the not more than After the three LC series branches are connected in parallel, they are connected in series to a shaping inductor L4. The initial values of Ln, Cn, and L4 satisfy the following relationship:

[0050]

[0051]

[0052] n=1, 2..., the upper limit value is the number of LC series branches, a is the initialization parameter, and its value range is between 0.01-0.3, set according to the needs of different application scenarios, ρ is the circuit matching impedance design Value, τ is the design value of the bottom width of the output waveform. Generally, ρ<5Ω, τ<200ns. The value of a is inversely related to the number of network stages (that is, the number of LC series branches in the circuit). ...

Embodiment 2

[0058] This embodiment discloses a method for designing a hundred nanosecond trapezoidal wave pulse forming network, which includes the following steps:

[0059] A. Build a simulation circuit and configure the initial values of each inductor and capacitor. That is, no more than three LC series branches are connected in parallel, and then connected in series with the shaping inductor L4 to complete the construction of the simulation circuit. Configure the initial values of Ln, Cn, and L4 calculated based on formulas (1)-(3) to the corresponding devices. When calculating the initial values of each capacitance and inductance respectively, bit reservation processing is also performed on the settlement results, that is, the calculation results are reserved to ones, tenths, percentiles... . For example, when calculating the initial values of the respective inductances, the calculated values are rounded. Rounding is generally used for rounding. The specific bit reservati...

Embodiment 3

[0066] This embodiment discloses another design method of a hundred nanosecond trapezoidal wave pulse forming network, which includes the following steps:

[0067] A. Calculate the initial values of Ln, Cn, and L4 according to formulas (1)-(3), and select the corresponding capacitors and inductors to build the initial circuit. That is, the initial values of Ln, Cn, and L4 are calculated based on formulas (1)-(3), respectively, and the capacitance and inductance of the corresponding values are selected, and Ln and Cn are connected in series to form an LC series branch, and then each series branch is connected in parallel. , in series with L4. When calculating the initial values of each capacitance and inductance respectively, bit reservation processing is also performed on the settlement results, that is, the calculation results are reserved to ones, tenths, percentiles... . For example, when calculating the initial values of the respective inductances, the calculate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More