3D memory device and manufacturing method thereof

A storage device and manufacturing method technology, applied in the field of memory, can solve the problems of low read window, poor process, and unfavorable reliability of 3D storage devices in lower storage units, so as to increase the read window, improve reliability, and improve bottom interference coupling effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

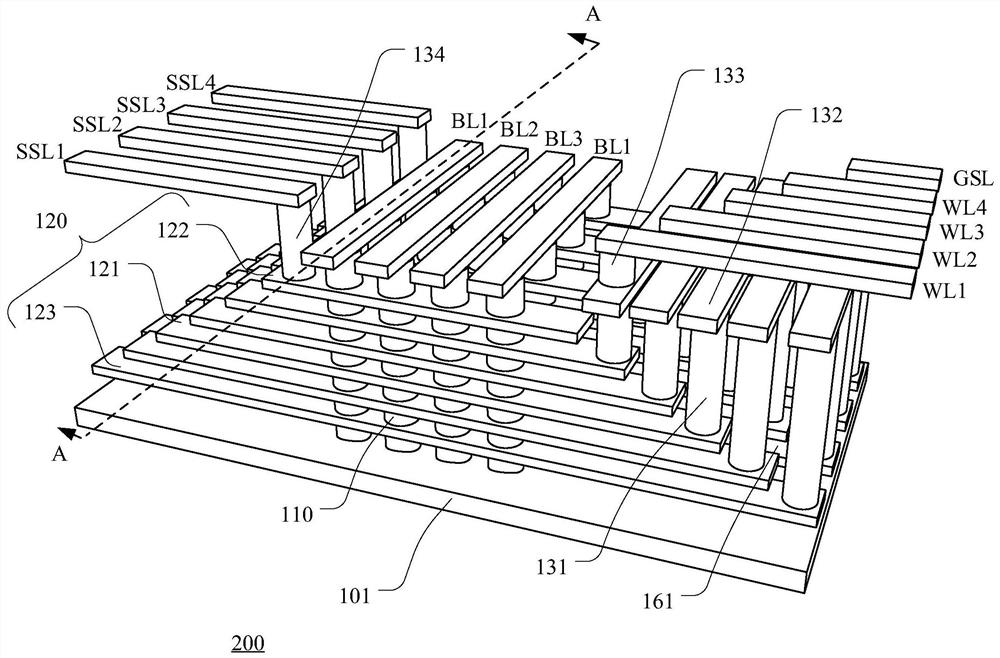

[0036] Various embodiments of the invention will be described in more detail below with reference to the accompanying drawings. In the various drawings, the same elements are denoted by the same or similar reference numerals. For the sake of clarity, various parts in the drawings have not been drawn to scale.

[0037] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

[0038] "Above" described in the present invention refers to being located above the plane of the substrate, which may refer to direct contact between materials, or may be arranged at intervals.

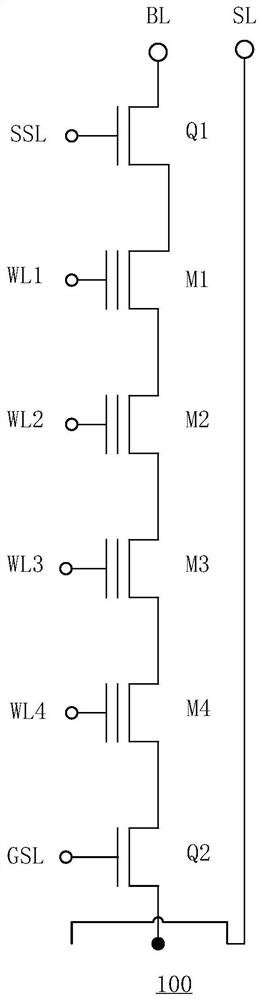

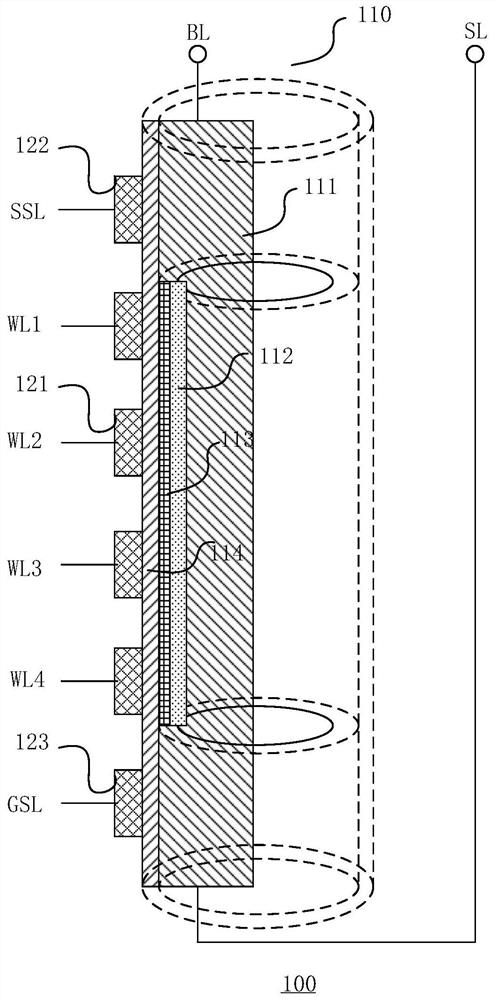

[0039] Figure 1a and Figure 1b A circuit diagram and a schematic structural diagram of a memory cell string of a 3D memory device are respectively shown. The memory cell string shown in this embodiment includes the case of 4 memory cells. It can be understood that the present invention is not limited...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More