Super junction MOS (Metal Oxide Semiconductor) type power semiconductor device and preparation method thereof

A technology of power semiconductors and semiconductors, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as charge imbalance, reduce device breakdown voltage, increase turn-off loss, etc., to solve the problem of breakdown voltage Reduced, high injection efficiency effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

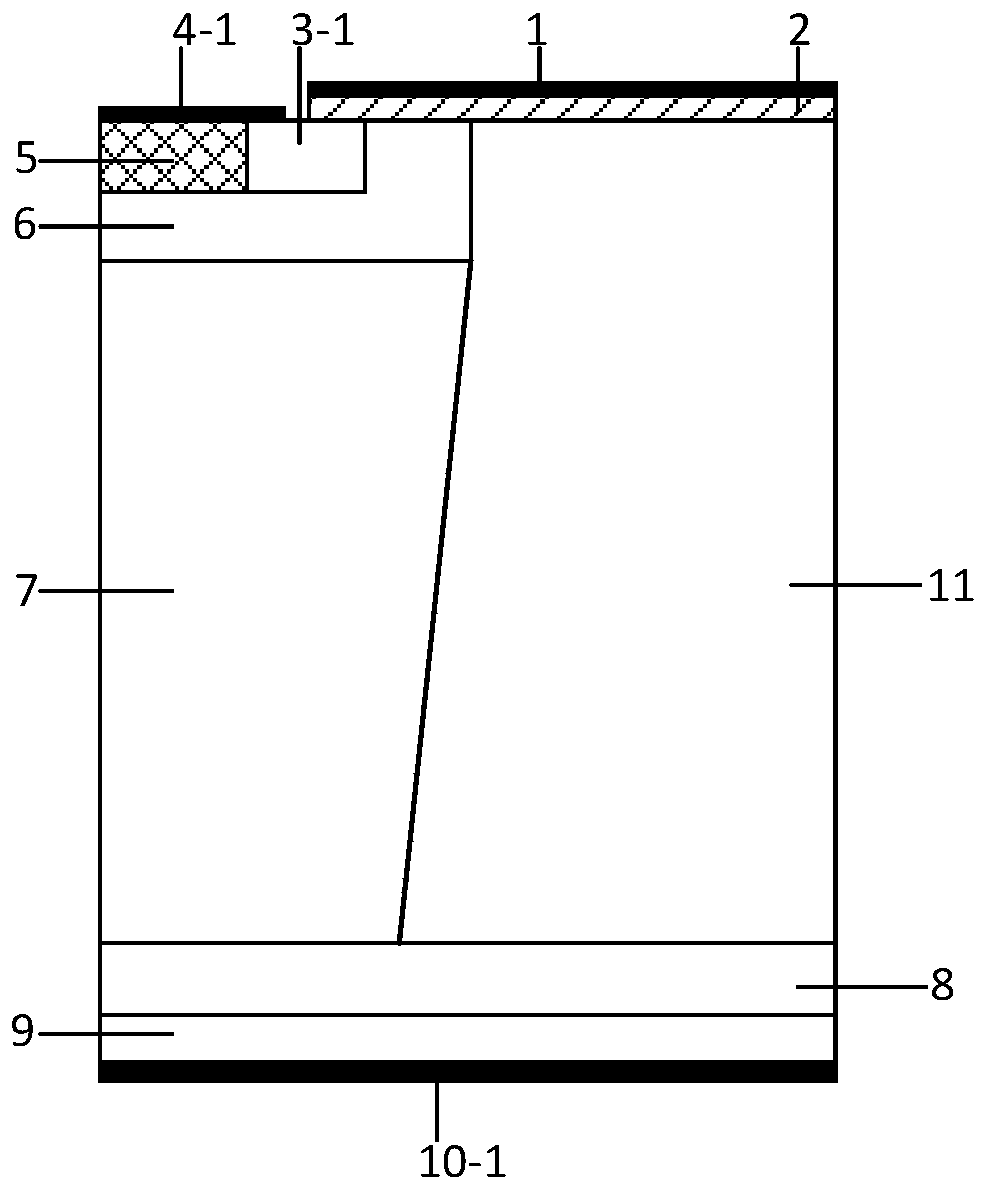

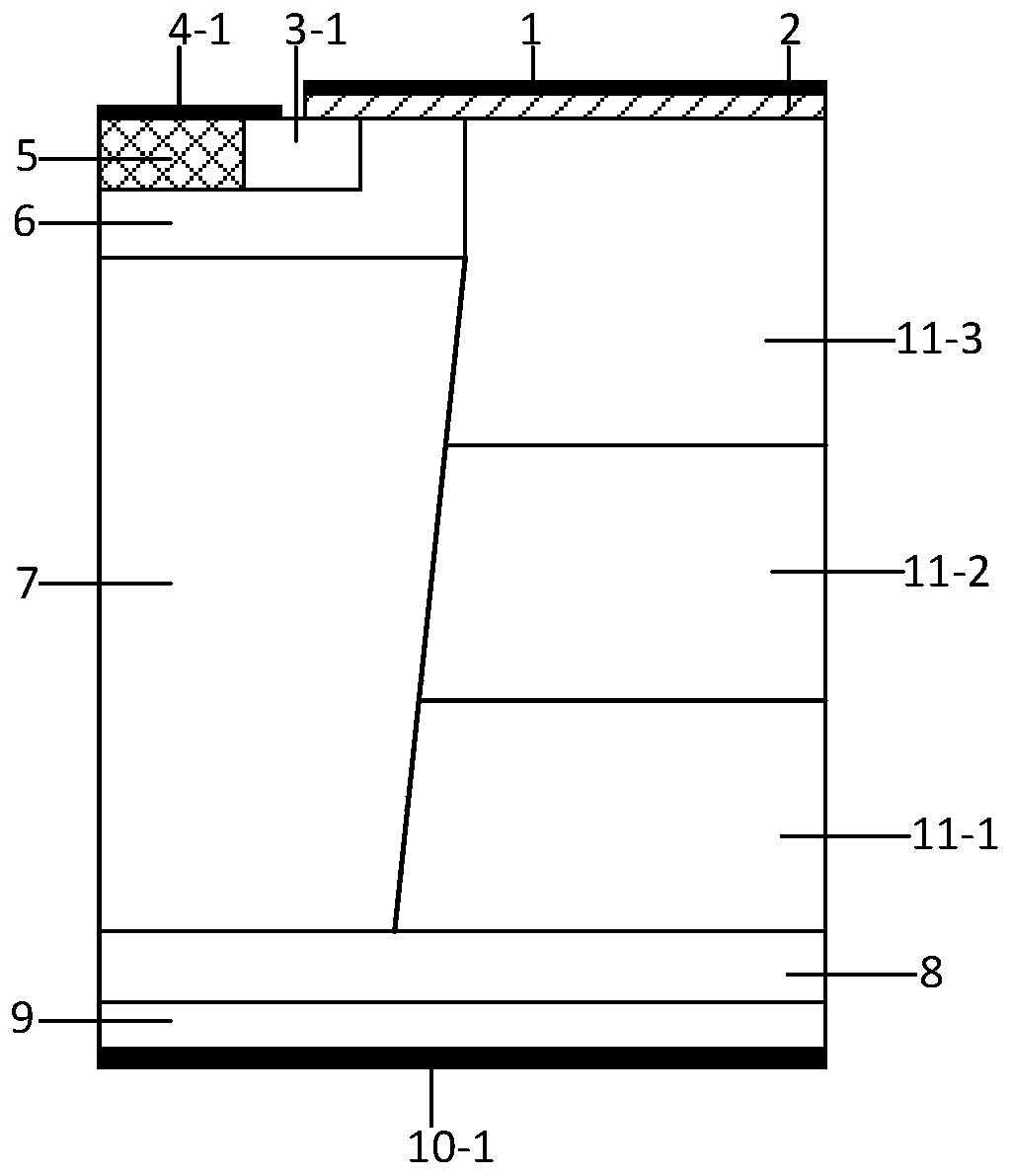

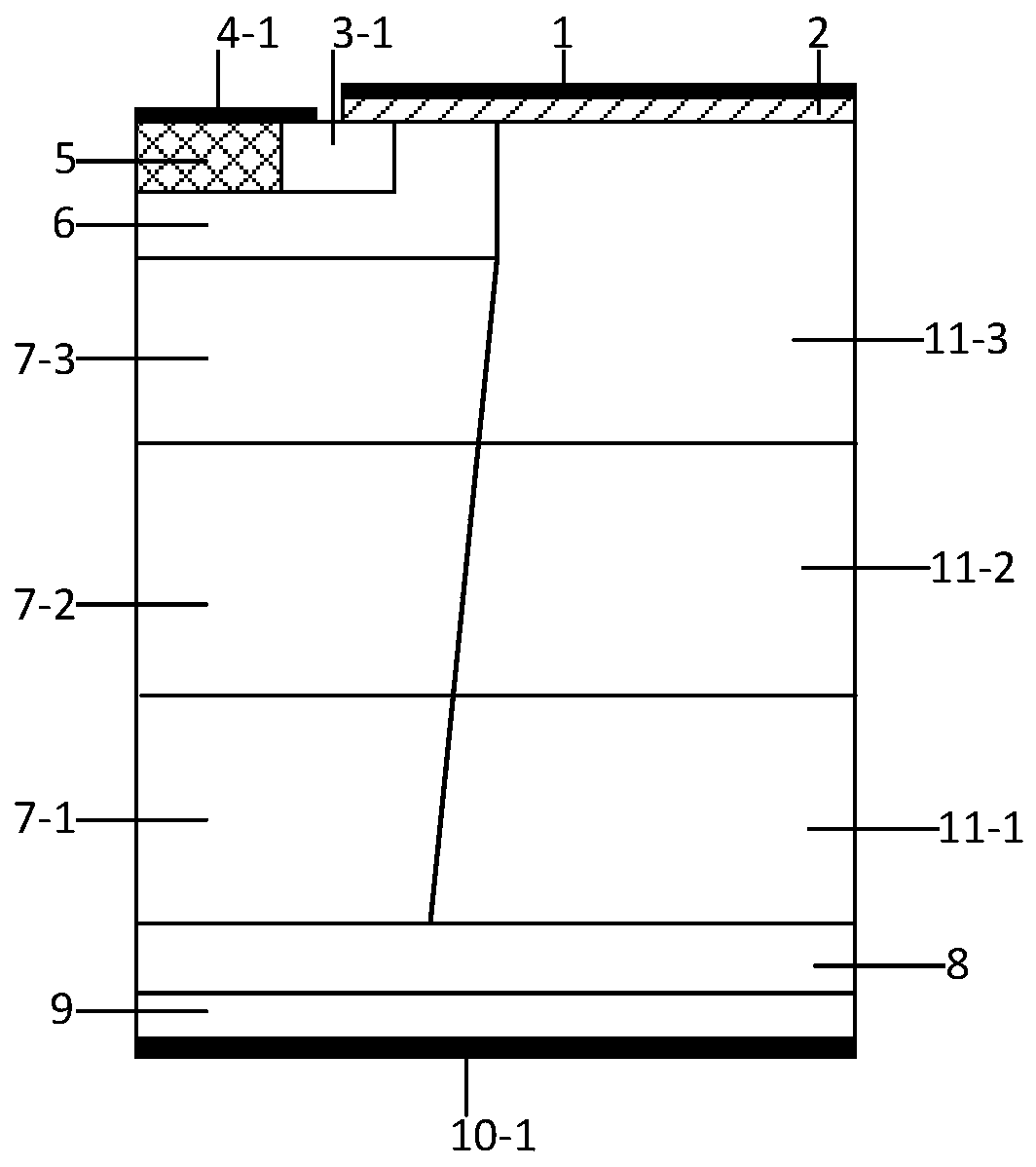

[0052] like figure 2 As shown, a super junction MOS type power semiconductor device provided by the first embodiment of the present invention includes: a metallized drain 10-1, a first conductivity type semiconductor drain region 9, a first conductivity type semiconductor field stop layer 8, The second conductivity type semiconductor column area 7, the first conductivity type semiconductor first column area 11-1, the first conductivity type semiconductor second column area 11-2, the first conductivity type semiconductor third column area 11-3, the second Conduction type semiconductor base region 6, second conductivity type semiconductor layer 5, first conductivity type semiconductor source region 3-1, planar gate s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More