Analog circuit optimization algorithm based on multi-objective acquisition function integrated parallel Bayesian optimization

A multi-objective integration and multi-objective optimization technology, which is applied in the field of analog circuit optimization algorithms based on multi-objective acquisition function integration parallel Bayesian optimization, can solve the problems of small number of simulations and inability to make full use of parallel resources, and achieve good optimization results Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0067] Now, the method of the present invention is described through the implementation process of specific calculation examples.

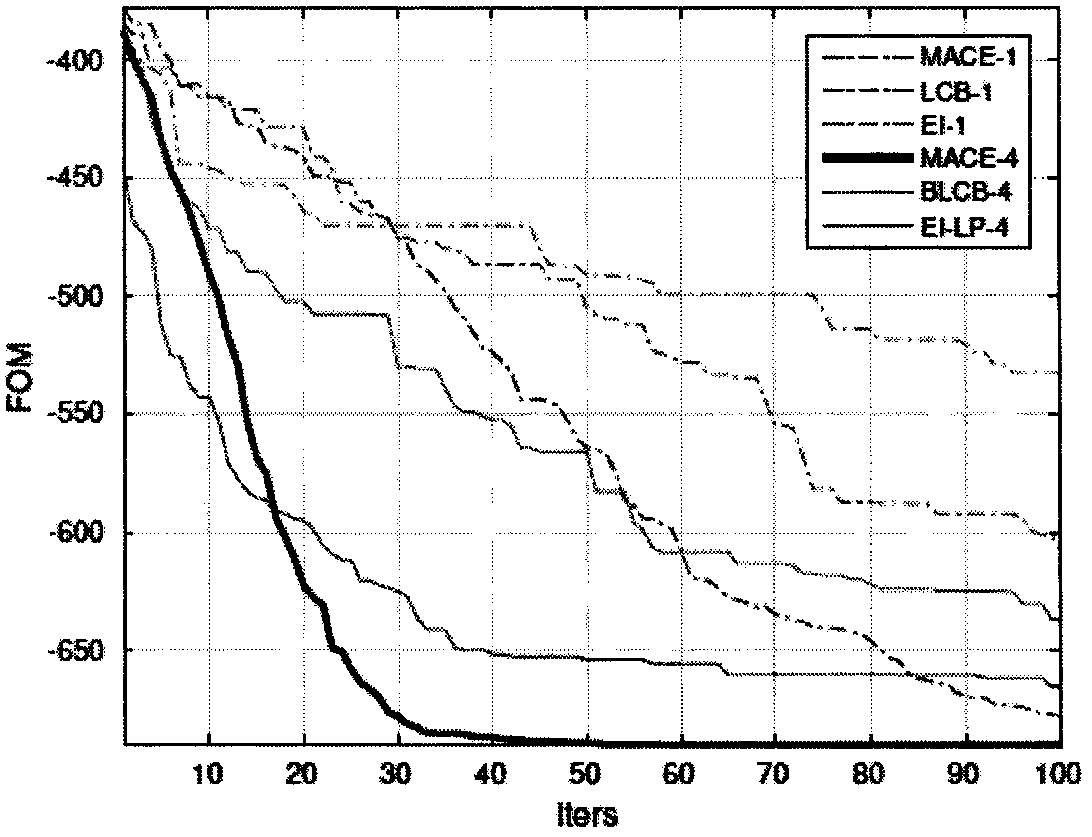

[0068] The Multi-Objective ACquisition function Ensemble (MACE) method proposed in this application is compared with other parallel Bayesian optimization algorithms. The methods to be compared include the BLCB algorithm proposed in the prior art [8], the local penalty (LP) algorithm proposed in the prior art [9], the qKG method proposed in the prior art [10] and the prior art [ 11] proposed qEI method.

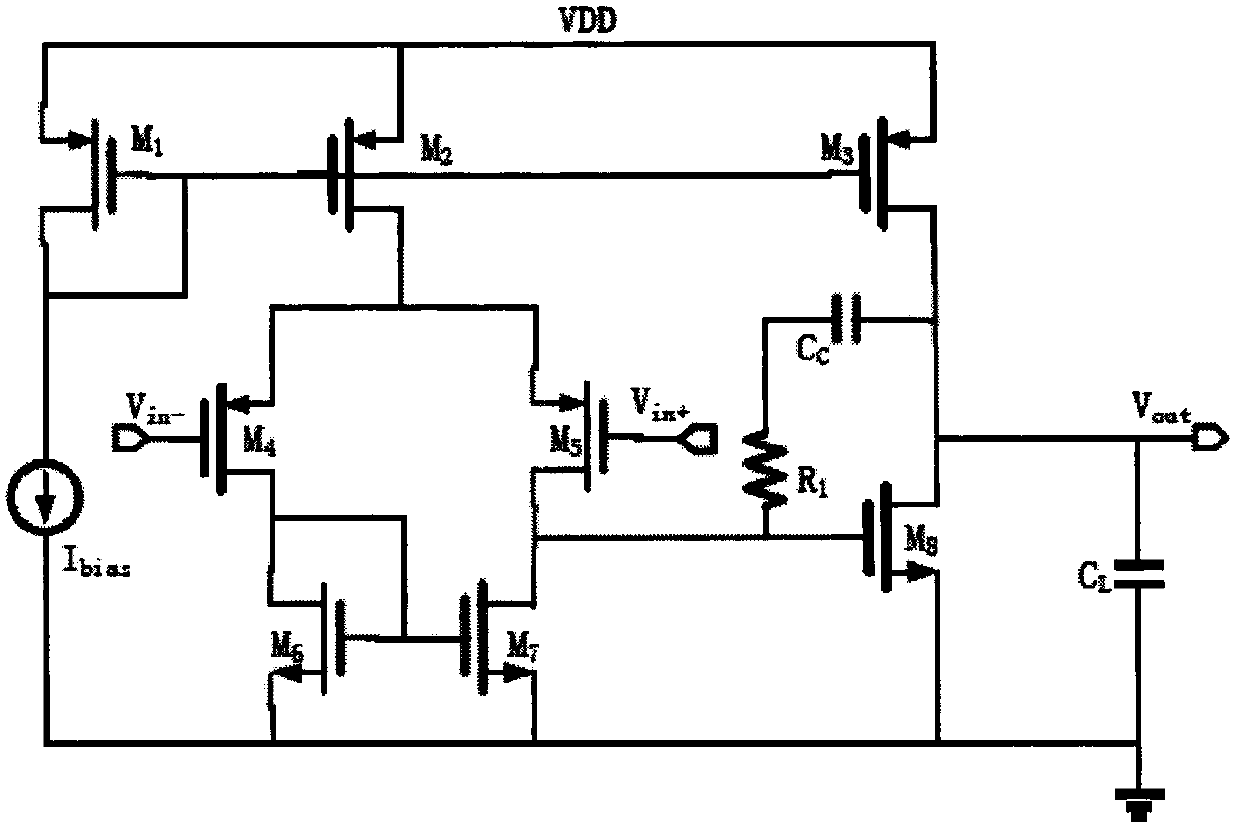

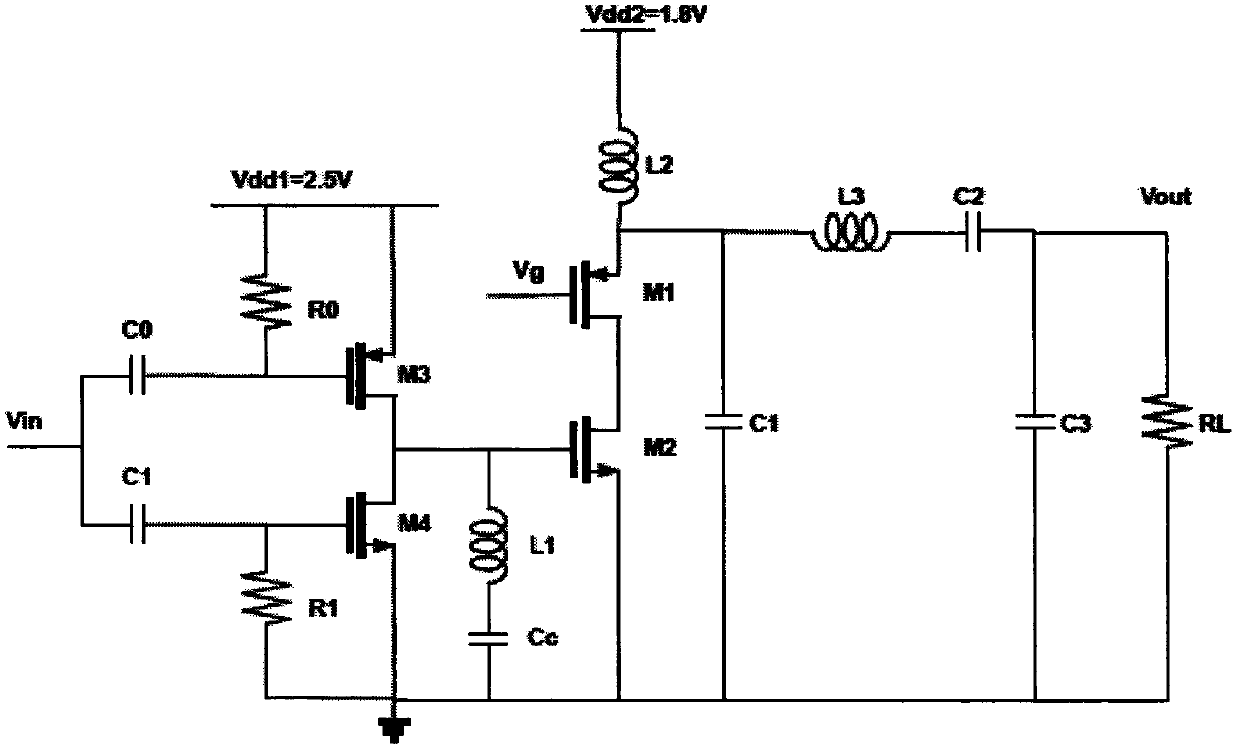

[0069] The present invention uses three calculation examples to test the MACE algorithm. The first calculation example is a general analytical test function, and the other two calculation examples are actual analog circuit netlists, including an operational amplifier and a power amplifier.

[0070] Implementation example 1

[0071] Eight general analytical test functions are used to test the MACE algorithm. The dimensions and computational searc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More